- 您现在的位置:买卖IC网 > PDF目录373890 > AD6623AS (ANALOG DEVICES INC) 4-Channel, 104 MSPS Digital Transmit Signal Processor TSP PDF资料下载

参数资料

| 型号: | AD6623AS |

| 厂商: | ANALOG DEVICES INC |

| 元件分类: | 通信及网络 |

| 英文描述: | 4-Channel, 104 MSPS Digital Transmit Signal Processor TSP |

| 中文描述: | SPECIALTY TELECOM CIRCUIT, PQFP128 |

| 封装: | PLASTIC, MQFP-128 |

| 文件页数: | 5/40页 |

| 文件大小: | 381K |

| 代理商: | AD6623AS |

第1页第2页第3页第4页当前第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页

REV. 0

–5–

AD6623

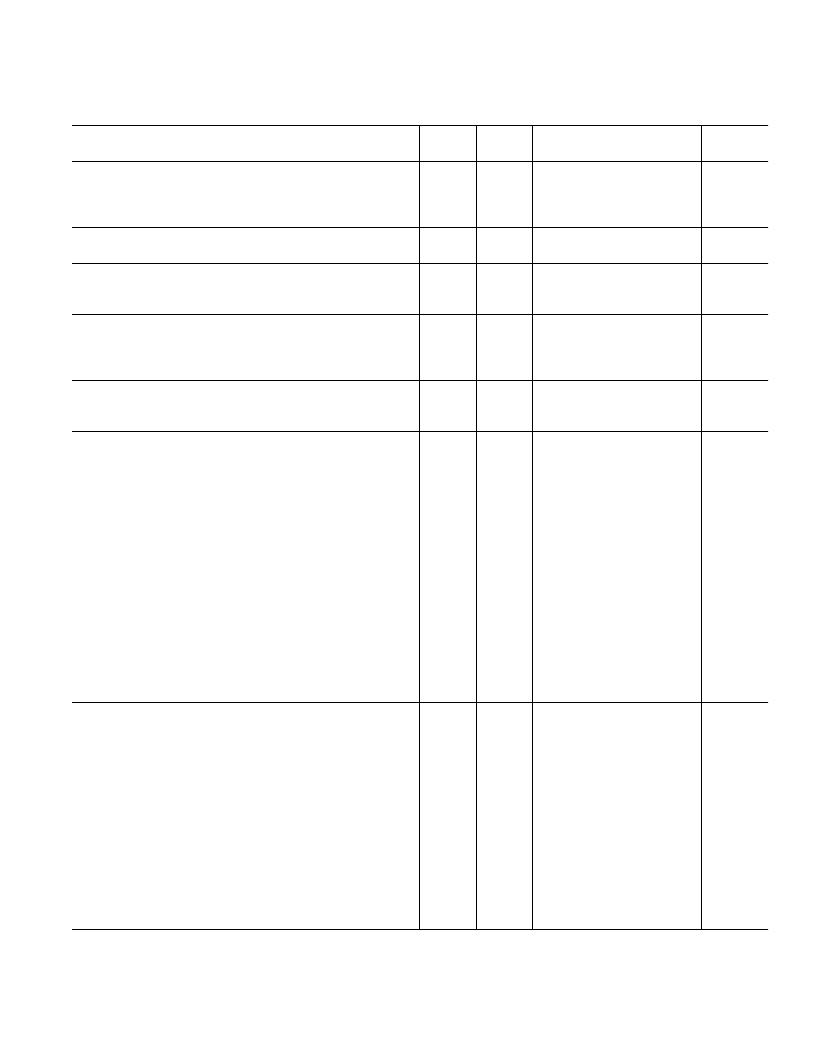

GENERAL TIMING CHARACTERISTICS

1, 2

Test

Level

AD6623AS

Typ

Parameter (Conditions)

Temp

Min

Max

Unit

CLK Timing Requirements:

t

CLK

t

CLKL

t

CLKH

RESET

Timing Requirement:

t

RESL

Input Data Timing Requirements:

t

SI

t

HI

Output Data Timing Characteristics:

t

DO

CLK Period

CLK Width Low

CLK Width High

Full

Full

Full

I

IV

IV

9.6

3

3

ns

ns

ns

0.5

×

t

CLK

RESET

Width Low

Full

I

30.0

ns

INOUT[17:0], QIN to

↑

CLK Setup Time

INOUT[17:0], QIN to

↑

CLK Hold Time

Full

Full

IV

IV

1

2

ns

ns

↑

CLK to OUT[17:0], INOUT[17:0],

QOUT Output Delay Time

OEN HIGH to OUT[17:0] Active

Full

Full

IV

IV

2

3

6

7.5

ns

ns

t

DZO

SYNC Timing Requirements:

t

SS

t

HS

Master Mode Serial Port Timing Requirements (SCS = 0):

Switching Characteristics

3

t

DSCLK1

↑

CLK to

↑

SCLK Delay (divide by 1)

t

DSCLKH

↑

CLK to

↑

SCLK Delay (for any other divisor)

t

DSCLKL

↑

CLK to

↓

SCLK Delay

(divide by 2 or even number)

t

DSCLKLL

↓

CLK to

↓

SCLK Delay

(divide by 3 or odd number)

Channel is Self-Framing

t

SSDI0

SDIN to

↑

SCLK Setup Time

t

HSDI0

SDIN to

↑

SCLK Hold Time

t

DSFO0A

↑

SCLK to SDFO Delay

Channel is External-Framing

t

SSFI0

SDFI to

↑

SCLK Setup Time

t

HSFI0

SDFI to

↑

SCLK Hold Time

t

SSDI0

SDIN to

↑

SCLK Setup Time

t

HSDI0

SDIN to

↑

SCLK Hold Time

t

DSFO0B

↑

SCLK to SDFO Delay

Slave Mode Serial Port Timing Requirements (SCS = 1):

Switching Characteristics

3

t

SCLK

SCLK Period

t

SCLKL

SCLK Low Time

t

SCLKH

SCLK High Time

Channel is Self-Framing

t

SSDH

SDIN to

↑

SCLK Setup Time

t

HSDH

SDIN to

↑

SCLK Hold Time

t

DSFO1

↑

SCLK to SDFO Delay

Channel is External-Framing

t

SSFI1

SDFI to

↑

SCLK Setup Time

t

HSFI1

SDFI to

↑

SCLK Hold Time

t

SSDI1

SDIN to

↑

SCLK Setup Time

t

HSDI1

SDIN to

↑

SCLK Hold Time

t

DSFO1

↓

SCLK to SDFO Delay

NOTES

1

All Timing Specifications valid over VDD range of 2.375 V to 2.675 V and VDDIO range of 3.0 V to 3.6 V.

2

C

LOAD

= 40 pF on all outputs (unless otherwise specified).

3

The timing parameters for SCLK, SDIN, SDFI, SDFO, and SYNC apply to all four channels (A, B, C, and D).

Specifications subject to change without notice.

SYNC(0, 1, 2, 3) to

↑

CLK Setup Time

SYNC(0, 1, 2, 3) to

↑

CLK Hold Time

Full

Full

IV

IV

1

2

ns

ns

Full

Full

IV

IV

4

5

10.5

13

ns

ns

Full

IV

3.5

9

ns

Full

IV

4

10

ns

Full

Full

Full

IV

IV

IV

1.7

0

0.5

ns

ns

ns

3.5

Full

Full

Full

Full

Full

IV

IV

IV

IV

IV

2

0

2

0

0.5

ns

ns

ns

ns

ns

3

Full

Full

Full

IV

IV

IV

2 t

CLK

ns

ns

ns

3.5

3.5

Full

Full

Full

IV

IV

IV

1

2.5

4

ns

ns

ns

10

Full

Full

Full

Full

Full

IV

IV

IV

IV

IV

2

1

1

2.5

10

ns

ns

ns

ns

ns

相关PDF资料 |

PDF描述 |

|---|---|

| AD6623PCB | 4-Channel, 104 MSPS Digital Transmit Signal Processor TSP |

| AD6624AS | Four-Channel, 80 MSPS Digital Receive Signal Processor (RSP) |

| AD6624A | Four-Channel, 100 MSPS Digital Receive Signal Processor (RSP) |

| AD6624AABC | Four-Channel, 100 MSPS Digital Receive Signal Processor (RSP) |

| AD6630AR-REEL | Differential, Low Noise IF Gain Block with Output Clamping |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD6623ASZ | 功能描述:IC TSP 4CHAN 104MSPS 128MQFP RoHS:是 类别:集成电路 (IC) >> 接口 - 专用 系列:- 特色产品:NXP - I2C Interface 标准包装:1 系列:- 应用:2 通道 I²C 多路复用器 接口:I²C,SM 总线 电源电压:2.3 V ~ 5.5 V 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:剪切带 (CT) 安装类型:表面贴装 产品目录页面:825 (CN2011-ZH PDF) 其它名称:568-1854-1 |

| AD6623BC/PCB | 制造商:AD 制造商全称:Analog Devices 功能描述:4-Channel, 104 MSPS Digital Transmit Signal Processor TSP |

| AD6623PCB | 制造商:AD 制造商全称:Analog Devices 功能描述:4-Channel, 104 MSPS Digital Transmit Signal Processor TSP |

| AD6623S/PCB | 制造商:Analog Devices 功能描述:4-CH, 104 MSPS DGTL TRANSMIT SGNL PROCESSOR (TSP) 28SOIC - Bulk |

| AD6624 | 制造商:AD 制造商全称:Analog Devices 功能描述:Four-Channel, 80 MSPS Digital Receive Signal Processor (RSP) |

发布紧急采购,3分钟左右您将得到回复。