- 您现在的位置:买卖IC网 > PDF目录373890 > AD6623AS (ANALOG DEVICES INC) 4-Channel, 104 MSPS Digital Transmit Signal Processor TSP PDF资料下载

参数资料

| 型号: | AD6623AS |

| 厂商: | ANALOG DEVICES INC |

| 元件分类: | 通信及网络 |

| 英文描述: | 4-Channel, 104 MSPS Digital Transmit Signal Processor TSP |

| 中文描述: | SPECIALTY TELECOM CIRCUIT, PQFP128 |

| 封装: | PLASTIC, MQFP-128 |

| 文件页数: | 21/40页 |

| 文件大小: | 381K |

| 代理商: | AD6623AS |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页当前第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页

REV. 0

AD6623

–21–

(2

–

15

) 2, or 0.00006103515625. The register values, in hexadecimal,

and the corresponding coefficient weight from positive full-scale

through zero to negative full-scale is illustrated in Table X.

Table X. Coefficient Weights

Register Value

Coefficient Weight

0x7FFF

..

0x0001

0x0000

0xFFFF

..

0x8001

0x8000

1.999938964844

0.00006103515625

0

–

0.00006103515625

–

1.999938964844

–

2

Table XI shows the recommended b

1

and b

2

coefficients for the

respective oversampling rate.

Table XI. b

1

and b

2

Coefficients

Oversampling

b

0

1

1

1

1

b

1

–

1.45514

–

1.56195

–

1.63412

–

1.72513

b

2

0.57832

0.64526

0.69414

0.76047

4

5

6

8

SCALE AND RAMP

Scale factors can be range from 0 to [CHF]

–

1/[CHF] with a

resolution 1/[CHF]

FINE SCALING

AD6623 allows fine scaling of the RCF output signal. A scale

factor of 12 to 14 bits is available through the Microport. The

Microport fine scale factor is located in Channel Register 0xn0E.

RCF POWER RAMPING

The output of the RCF will be multiplied by a 14-bit ramping

profile before entering the CIC filters. It is a RAM program-

mable engine that starts indexing through ramping coefficients

when the RAMP bit works its way through the chain. It will then

count a programmable number of samples and then RAMP down

in reverse order. This will allow the ramping values to update at

a modest rate relative to the DAC and still contain the spectral

leakage associated with the ramping. A user should provide

through the MicroPort the ramping coefficient values, the number

of samples to ramp up, and one bit to define the air-interface

standard. The programmable power ramp up/down unit allows

power ramping on time-slot basis as specified from some wireless

transmission technologies (e.g, TDMA).

CASCADED INTEGRATOR COMB (CIC)

INTERPOLATING FILTERS

The I and Q outputs of the RCF stage are interpolated by two

cascaded integrator comb (CIC) filters. The CIC section is sepa-

rated into three discrete blocks: a fifth order filter (CIC5), a second

order resampling filter (rCIC2), and a scaling block (CIC Scaling).

The CIC5 and rCIC2 blocks each exhibit a gain that changes with

respect to their rate change factors, L

rCIC2

, M

rCIC2

and L

CIC5

. The

product of these gains must be compensated for in a shared CIC

Scaling block and can be done to within 6 dB The remaining

compensation can come from the RCF (in the form of coeffi-

cient scaling) or the fine scaling unit.

SERIAL

8PSK

MAPPER

SPH

[2:0]

[3:0]

PHASE

[3:0]

[3:0]

RPH

3

Figure 24. 3

π

/8-8-PSK Mapper

MSK Look-Up Table

The MSK Look-Up Table mode for the RCF is selected in Control

Register 0x10C. In the MSK Mode, the RCF performs

arbitrary

pulse-shaping based on four symbols of impulse response.

For the

MSK Mode (3, [16] bits), the serial input format is 11 bits of scaling

(MSB first) followed by 1 bit of data. The 11 bits can be used to

scale the input data.

GMSK Look-Up Table

The GMSK Look-Up Table mode for the RCF is selected in Control

Register 0x10C. In the GMSK Mode, the RCF performs arbitrary

pulse-shaping based on four symbols of impulse response.

For the

GMSK Mode (3, [16] bits), the serial input format is 11

bits of

scaling (MSB first) followed by 1 bit of data. The 11 bits can be used

to scale the input data.

QPSK Look-Up Table

The QPSK Filter mode for the RCF is selected in Control

Register 0xX0C. In the QPSK Mode, the RCF performs baseband

linear pulse-shaping based on filter impulse response up to 12

symbols. For the QPSK Mode (3, [16]bits), the serial input format

is 13 bits of scaling (MSB first) followed by one bit I and then

one bit Q. The 13 bits can be used to scale the input data.

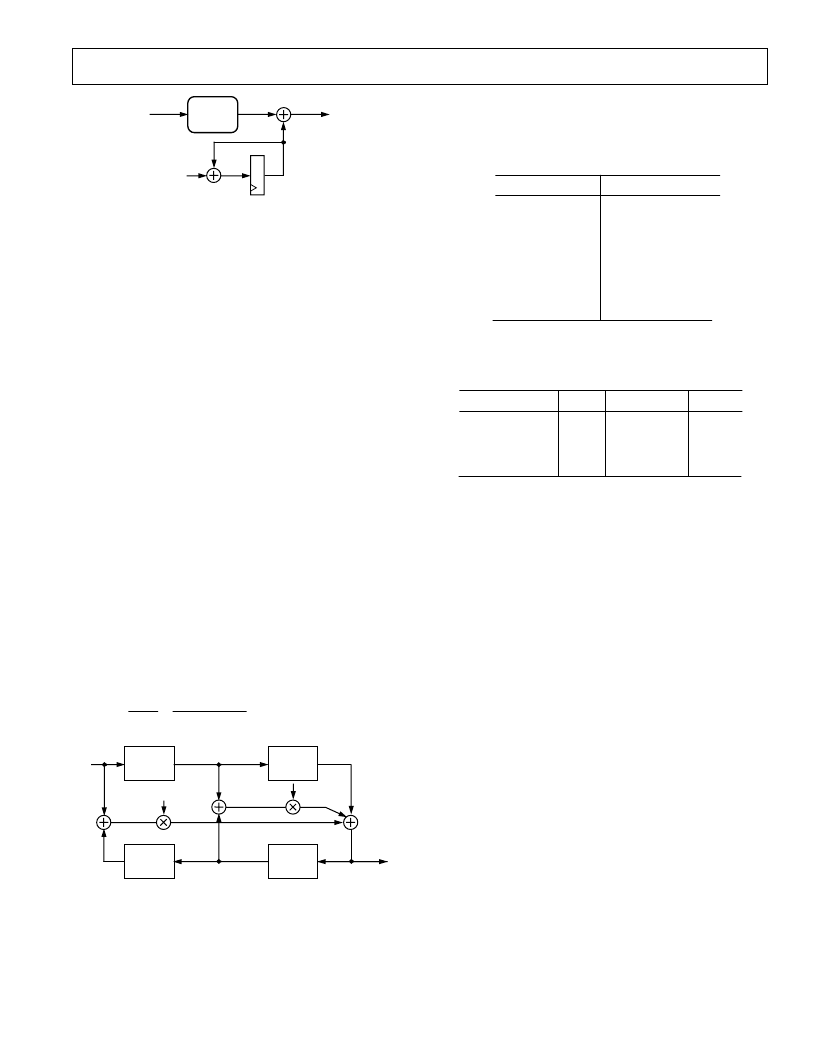

PHASE EQUALIZER

The IS-95 Standard includes a phase equalizer after matched

filtering at the baseband transmit side of a base station. This

filter pre-distorts the transmitted signal at the base station in

order to compensate for the distortion introduced to the received

signal by the analog baseband filtering in a handset. The AD6623

includes this functionality in the form of an Infinite Impulse

Response (IIR) all-pass filter in the RCF. This Phase Equalizer

pre-distort filter has the following transfer function:

H( )

Y( )

X( )

b z

+

b z

+

z

b z

1

b

=

=

+

2

+

1

1

2

2

2

(9)

Z

–

1

Z

–

1

Z

–

1

Z

–

1

X(z)

Y(z)

b

2

b

1

Figure 25. Second Order All-Pass IIR Filter

The Phase Equalizer is enabled/disabled in Control Register

0xn0D Bit 5. The coefficients b

1

and b

2

are located in Control

Registers 0xn10 and 0xn11 respectively

The format for b

1

and b

2

is two

’

s complement fractional binary

with a range of (

–

2, 2). With one bit for sign at most significant bit

position there are 15 bits for magnitude. The value of one bit

is

相关PDF资料 |

PDF描述 |

|---|---|

| AD6623PCB | 4-Channel, 104 MSPS Digital Transmit Signal Processor TSP |

| AD6624AS | Four-Channel, 80 MSPS Digital Receive Signal Processor (RSP) |

| AD6624A | Four-Channel, 100 MSPS Digital Receive Signal Processor (RSP) |

| AD6624AABC | Four-Channel, 100 MSPS Digital Receive Signal Processor (RSP) |

| AD6630AR-REEL | Differential, Low Noise IF Gain Block with Output Clamping |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD6623ASZ | 功能描述:IC TSP 4CHAN 104MSPS 128MQFP RoHS:是 类别:集成电路 (IC) >> 接口 - 专用 系列:- 特色产品:NXP - I2C Interface 标准包装:1 系列:- 应用:2 通道 I²C 多路复用器 接口:I²C,SM 总线 电源电压:2.3 V ~ 5.5 V 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:剪切带 (CT) 安装类型:表面贴装 产品目录页面:825 (CN2011-ZH PDF) 其它名称:568-1854-1 |

| AD6623BC/PCB | 制造商:AD 制造商全称:Analog Devices 功能描述:4-Channel, 104 MSPS Digital Transmit Signal Processor TSP |

| AD6623PCB | 制造商:AD 制造商全称:Analog Devices 功能描述:4-Channel, 104 MSPS Digital Transmit Signal Processor TSP |

| AD6623S/PCB | 制造商:Analog Devices 功能描述:4-CH, 104 MSPS DGTL TRANSMIT SGNL PROCESSOR (TSP) 28SOIC - Bulk |

| AD6624 | 制造商:AD 制造商全称:Analog Devices 功能描述:Four-Channel, 80 MSPS Digital Receive Signal Processor (RSP) |

发布紧急采购,3分钟左右您将得到回复。