参数资料

| 型号: | AD7194BCPZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 17/57页 |

| 文件大小: | 0K |

| 描述: | IC ADC 24BIT SPI 4.8K 32-LFCSP |

| 产品培训模块: | Weigh Scale Introduction |

| 标准包装: | 1 |

| 位数: | 24 |

| 采样率(每秒): | 4.8k |

| 数据接口: | DSP,MICROWIRE?,QSPI?,串行,SPI? |

| 转换器数目: | 1 |

| 电压电源: | 模拟和数字 |

| 工作温度: | -40°C ~ 105°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 32-WFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 32-LFCSP-WQ(5x5) |

| 包装: | 管件 |

| 输入数目和类型: | 8 个差分,单极;8 个差分,双极;16 个伪差分,单极;16 伪差分,双极 |

| 产品目录页面: | 777 (CN2011-ZH PDF) |

| 其它名称: | AD7194BRUZ AD7194BRUZ-ND |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页当前第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页

Data Sheet

AD7194

Rev. A | Page 23 of 56

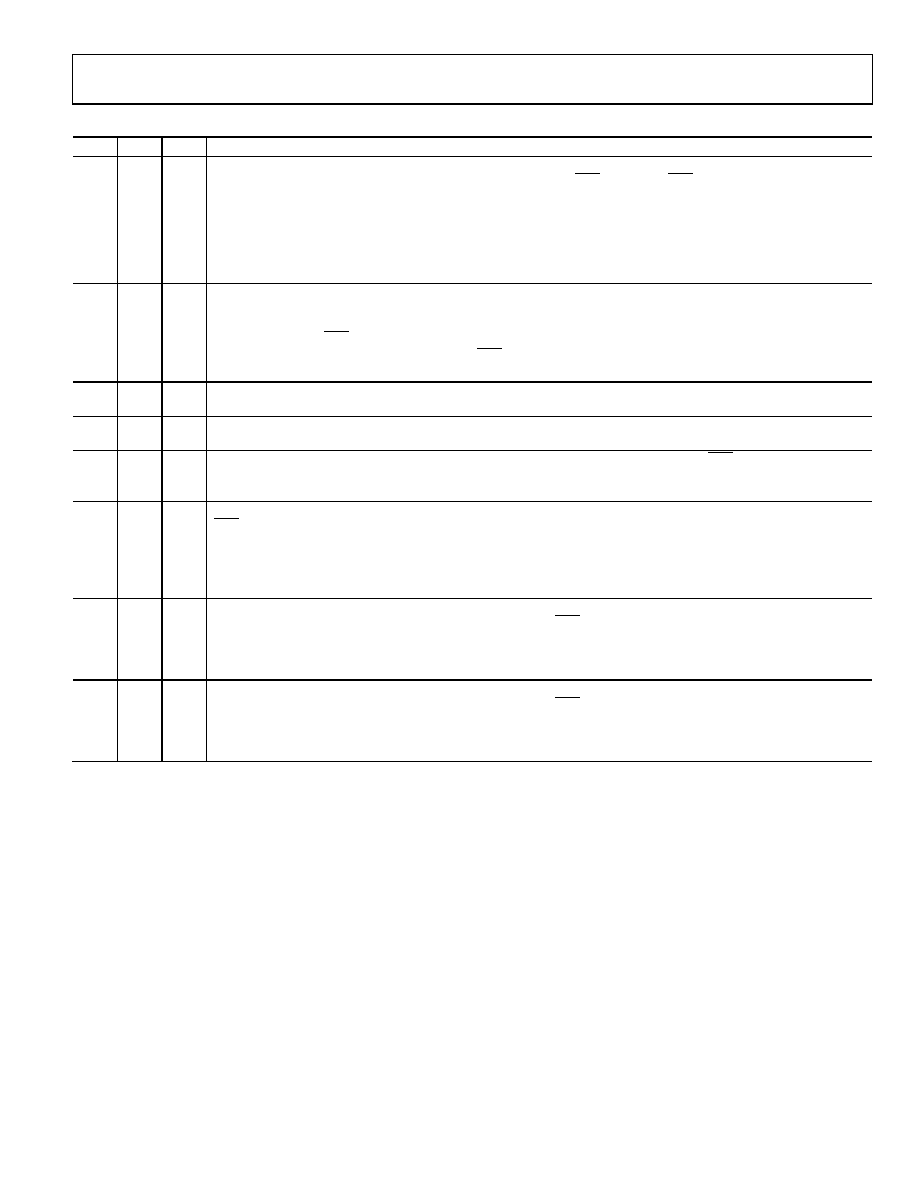

Table 20. Operating Modes (MD)

MD2

MD1

MD0

Mode

0

Continuous conversion mode (default). In continuous conversion mode, the ADC continuously performs

conversions and places the result in the data register. The DOUT/RDY pin and the RDY bit in the status register

go low when a conversion is complete. The user can read these conversions by setting the CREAD bit in the

communications register to 1, which enables continuous read. When continuous read is enabled, the conversions

are automatically placed on the DOUT line when SCLK pulses are applied. Alternatively, the user can instruct the

ADC to output each conversion by writing to the communications register. After power-on, a reset, or a recon-

figuration of the ADC, the complete settling time of the filter is required to generate the first valid conversion.

Subsequent conversions are available at the selected output data rate, which is dependent on filter choice.

0

1

Single conversion mode. When single conversion mode is selected, the ADC powers up and performs a single

conversion on the selected channel. The internal clock requires 200 s typically to power up and settle. The ADC

then performs the conversion, which requires the complete settling time of the filter. The conversion result is placed

in the data register. RDY goes low, and the ADC returns to power-down mode. The conversion remains in the data

register until another conversion is performed. RDY remains active (low) until the data is read or another conversion

is performed.

0

1

0

Idle mode. In idle mode, the ADC filter and modulator are held in a reset state even though the modulator clocks

continue to be provided.

0

1

Power-down mode. In power-down mode, all AD7194 circuitry is powered down. The external crystal, if selected,

remains active.

1

0

Internal zero-scale calibration. An internal short is automatically connected to the input. RDY goes high when the

calibration is initiated and returns low when the calibration is complete. The ADC is placed in idle mode following a

calibration. The measured offset coefficient is placed in the offset register of the selected channel.

1

0

1

Internal full-scale calibration. A full-scale input voltage is automatically connected to the input for this calibration.

RDY goes high when the calibration is initiated and returns low when the calibration is complete. The ADC is

placed in idle mode following a calibration. The measured full-scale coefficient is placed in the full-scale register

of the selected channel. A full-scale calibration is recommended each time that the gain of a channel is changed

to minimize the full-scale error. When AVDD is less than 4.75 V, the CLK_DIV bit must be set when performing the

internal full-scale calibration.

1

0

System zero-scale calibration. The user should connect the system zero-scale input to the channel input pins as

selected by the CH7 to CH0 bits in the configuration register. RDY goes high when the calibration is initiated and

returns low when the calibration is complete. The ADC is placed in idle mode following a calibration. The measured

offset coefficient is placed in the offset register of the selected channel. A system zero-scale calibration is recommended

each time that the gain of a channel is changed.

1

System full-scale calibration. The user should connect the system full-scale input to the channel input pins as

selected by the CH7 to CH0 bits in the configuration register. RDY goes high when the calibration is initiated and

returns low when the calibration is complete. The ADC is placed in idle mode following a calibration. The measured

full-scale coefficient is placed in the full-scale register of the selected channel. A full-scale calibration is recommended

each time the gain of a channel is changed.

相关PDF资料 |

PDF描述 |

|---|---|

| AD7195BCPZ-RL7 | IC AFE 24BIT 4.8K 32LFSP |

| AD7225BQ | IC DAC 8BIT QUAD W/AMP 24-CDIP |

| AD7226BQ | IC DAC 8BIT QUAD W/AMP 20-CDIP |

| AD7228CQ | IC DAC 8BIT OCTAL W/AMP 24-CDIP |

| AD7233BNZ | IC DAC 12BIT SRL W/AMP 8PDIP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD7194BCPZ-REEL | 功能描述:IC ADC 24BIT SPI 4.8KHZ 32LFCSP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1,000 系列:- 位数:16 采样率(每秒):45k 数据接口:串行 转换器数目:2 功率耗散(最大):315mW 电压电源:模拟和数字 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SOIC(0.295",7.50mm 宽) 供应商设备封装:28-SOIC W 包装:带卷 (TR) 输入数目和类型:2 个单端,单极 |

| AD7194BCPZ-REEL7 | 功能描述:IC ADC 24BIT SPI 4.8KHZ 32LFCSP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1,000 系列:- 位数:16 采样率(每秒):45k 数据接口:串行 转换器数目:2 功率耗散(最大):315mW 电压电源:模拟和数字 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SOIC(0.295",7.50mm 宽) 供应商设备封装:28-SOIC W 包装:带卷 (TR) 输入数目和类型:2 个单端,单极 |

| AD7195 | 制造商:AD 制造商全称:Analog Devices 功能描述:4.8 kHz, Ultralow Noise, 24-Bit Sigma-Delta ADC with PGA and AC Excitation |

| AD7195BCPZ | 功能描述:IC AFE 24BIT 4.8K 32LFSP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模拟前端 (AFE) 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 位数:- 通道数:2 功率(瓦特):- 电压 - 电源,模拟:3 V ~ 3.6 V 电压 - 电源,数字:3 V ~ 3.6 V 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:带卷 (TR) |

| AD7195BCPZ | 制造商:Analog Devices 功能描述:IC ADC 24BIT 4.8KSPS CSP-32 |

发布紧急采购,3分钟左右您将得到回复。