参数资料

| 型号: | AD7195BCPZ-RL7 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 30/45页 |

| 文件大小: | 0K |

| 描述: | IC AFE 24BIT 4.8K 32LFSP |

| 设计资源: | Precision Weigh Scale Design Using AD7195 with Internal PGA and AC Excitation (CN0155) |

| 标准包装: | 1,500 |

| 位数: | 24 |

| 通道数: | 4 |

| 电压 - 电源,模拟: | 4.75 V ~ 5.25 V |

| 电压 - 电源,数字: | 2.7 V ~ 5.25 V |

| 封装/外壳: | 32-WFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 32-LFCSP-WQ(5x5) |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页当前第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页

AD7195

Rev. 0 | Page 35 of 44

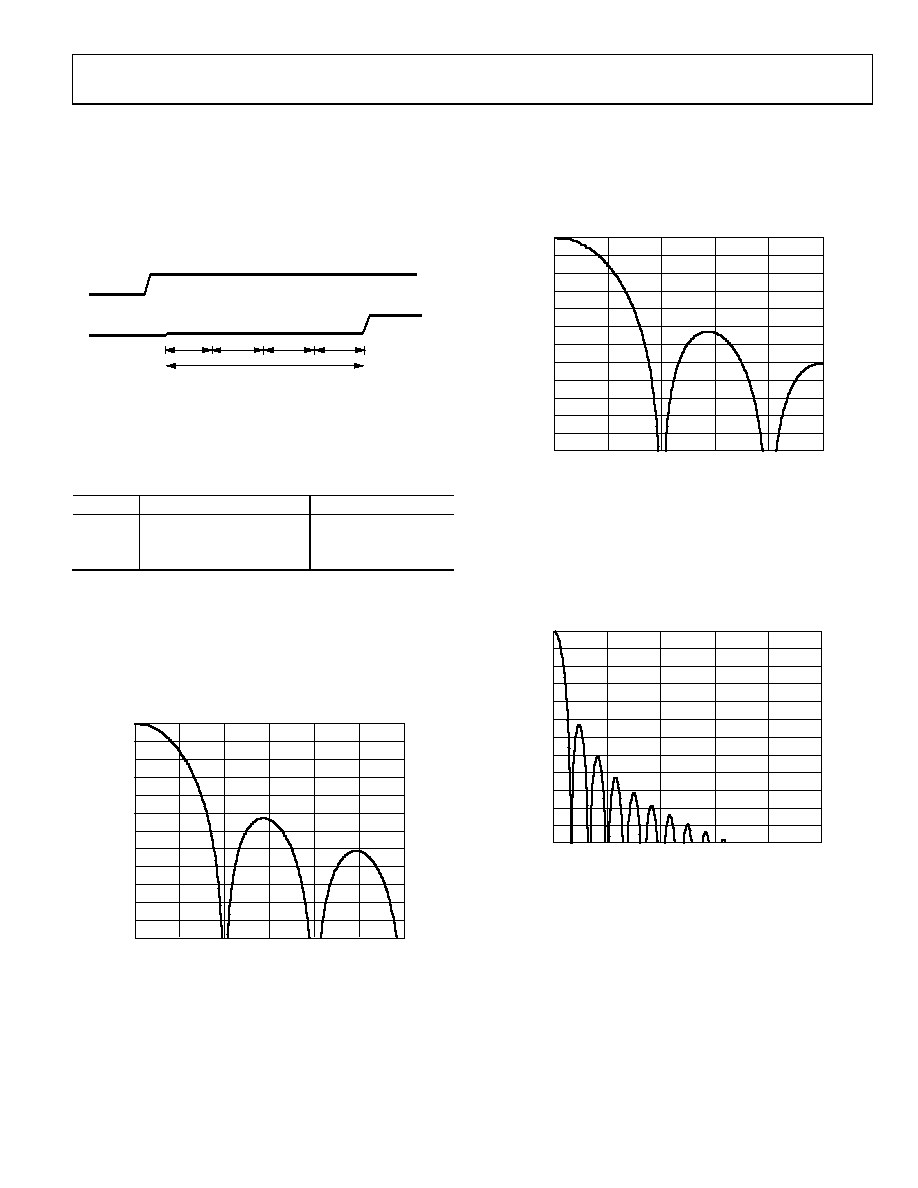

When the analog input is constant or a channel change occurs,

valid conversions are available at a constant output data rate.

When conversions are being performed on a single channel and

a step change occurs on the analog input, the ADC continues to

output fully settled conversions if the step change is synchronized

with the conversion process. If the step change is asynchronous,

one conversion is output from the ADC, which is not completely

settled (see Figure 27).

ANALOG

INPUT

ADC

OUTPUT

FULLY

SETTLED

1/

fADC

08

77

1-

0

40

Figure 27. Sinc4 Zero Latency Operation

Table 30 shows examples of output data rate and the corres-

ponding FS values.

Table 30. Examples of Output Data Rates and the

Corresponding Settling Time (Zero Latency)

FS[9:0]

Output Data Rate (Hz)

Settling Time (ms)

480

2.5

400

96

12.5

80

15

66.6

Sinc4 50 Hz/60 Hz Rejection

FS[9:0] is set to 96 and the master clock is 4.92 MHz. With zero

latency disabled, the output data rate is equal to 50 Hz. With

zero latency enabled, the output data rate is 12.5 Hz. The sinc4

filter provides 50 Hz (±1 Hz) rejection in excess of 120 dB

minimum, assuming a stable master clock.

–120

–110

–100

–90

–80

–70

–60

–50

–40

–30

–20

–10

0

25

50

75

100

125

150

FREQUENCY (Hz)

F

IL

T

E

R

GA

IN

(

d

B

)

08

77

1-

0

41

Figure 28. Sinc4 Filter Response (FS[9:0] = 96)

Figure 29 shows the frequency response when FS[9:0] is

programmed to 80 and the master clock is equal to 4.92 MHz.

The output data rate is 60 Hz when zero latency is disabled and

15 Hz when zero latency is enabled. The sinc4 filter provides

60 Hz (±1 Hz) rejection of 120 dB minimum, assuming a stable

master clock.

–120

–110

–100

–90

–80

–70

–60

–50

–40

–30

–20

–10

0

30

60

90

120

150

FREQUENCY (Hz)

F

IL

T

E

R

GA

IN

(

d

B

)

08

77

1-

04

2

Figure 29. Sinc4 Filter Response (FS[9:0] = 80)

Simultaneous 50 Hz and 60 Hz rejection is obtained when

FS[9:0] is programmed to 480 and the master clock equals

4.92 MHz. The output data rate is 10 Hz when zero latency is

disabled and 2.5 Hz when zero latency is enabled. The sinc4

filter provides 50 Hz (±1 Hz) and 60 Hz (±1 Hz) rejection of

120 dB minimum, assuming a stable master clock.

–120

–110

–100

–90

–80

–70

–60

–50

–40

–30

–20

–10

0

30

60

90

120

150

FREQUENCY (Hz)

FI

L

T

E

R

GA

IN

(

d

B

)

08

77

1-

0

43

Figure 30. Sinc4 Filter Response (FS[9:0] = 480)

Simultaneous 50 Hz/60 Hz rejection can also be achieved using

the REJ60 bit in the mode register. When FS[9:0] is set to 96

and REJ60 is set to 1, notches are placed at 50 Hz and 60 Hz.

相关PDF资料 |

PDF描述 |

|---|---|

| AD7225BQ | IC DAC 8BIT QUAD W/AMP 24-CDIP |

| AD7226BQ | IC DAC 8BIT QUAD W/AMP 20-CDIP |

| AD7228CQ | IC DAC 8BIT OCTAL W/AMP 24-CDIP |

| AD7233BNZ | IC DAC 12BIT SRL W/AMP 8PDIP |

| AD7243BQ | IC DAC 12BIT W/AMP W/REF 16-CDIP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD71L | 制造商:Johnson Components 功能描述:ADAPT - Bulk |

| AD72 | 制造商:Distributed By MCM 功能描述:REFRIGERATR DOOR GASKET DIRECT |

| AD720 | 制造商:AD 制造商全称:Analog Devices 功能描述:RGB to NTSC/PAL Encoders |

| AD720-00E | 功能描述:SENSOR MAG SW 28G STANDRD 8-MSOP 制造商:nve corp/sensor products 系列:AD 包装:管件 零件状态:有效 功能:全极开关 技术:霍尔效应 极化:任意一种 感应范围:±3.4mT 跳闸,±1.4mT 释放 测试条件:-40°C ~ 125°C 电压 - 电源:4.5 V ~ 30 V 电流 - 电源(最大值):4.5mA 电流 - 输出(最大值):20mA 输出类型:开路集电极 特性:- 工作温度:-40°C ~ 125°C(TA) 封装/外壳:8-TSSOP,8-MSOP(0.118",3.00mm 宽) 供应商器件封装:8-MSOP 标准包装:1,000 |

| AD720-02E | 功能描述:SENSOR MAG SW 28G STANDARD 8SOIC 制造商:nve corp/sensor products 系列:AD 包装:管件 零件状态:有效 功能:全极开关 技术:霍尔效应 极化:任意一种 感应范围:±3.4mT 跳闸,±1.4mT 释放 测试条件:-40°C ~ 125°C 电压 - 电源:4.5 V ~ 30 V 电流 - 电源(最大值):4.5mA 电流 - 输出(最大值):20mA 输出类型:开路集电极 特性:- 工作温度:-40°C ~ 125°C(TA) 封装/外壳:8-SOIC(0.154",3.90mm 宽) 供应商器件封装:8-SOIC 标准包装:1,000 |

发布紧急采购,3分钟左右您将得到回复。