- 您现在的位置:买卖IC网 > PDF目录10118 > AD7713ARZ-REEL (Analog Devices Inc)IC ADC 24BIT SIGMA-DELTA 24SOIC PDF资料下载

参数资料

| 型号: | AD7713ARZ-REEL |

| 厂商: | Analog Devices Inc |

| 文件页数: | 5/28页 |

| 文件大小: | 0K |

| 描述: | IC ADC 24BIT SIGMA-DELTA 24SOIC |

| 标准包装: | 1,000 |

| 位数: | 24 |

| 采样率(每秒): | 205 |

| 数据接口: | 串行 |

| 转换器数目: | 1 |

| 功率耗散(最大): | 5.5mW |

| 电压电源: | 模拟和数字 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 24-SOIC(0.295",7.50mm 宽) |

| 供应商设备封装: | 24-SOIC W |

| 包装: | 带卷 (TR) |

| 输入数目和类型: | 1 个单端,单极;1 个差分,单极;1 个差分,双极 |

第1页第2页第3页第4页当前第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页

REV. D

AD7713

–13–

The AD7713 gives the user access to the on-chip calibration

registers, allowing the microprocessor to read the device’s calibra-

tion coefficients and also to write its own calibration coefficients

to the part from prestored values in E

2PROM. This gives the

microprocessor much greater control over the AD7713’s calibra-

tion procedure. It also means that the user can verify that the

device has performed its calibration correctly by comparing the

coefficients after calibration with prestored values in E

2PROM.

For battery-operated or low power systems, the AD7713 offers

a standby mode (controlled by the

STANDBY pin) that reduces

idle power consumption to typically 150

W.

THEORY OF OPERATION

The general block diagram of a -

ADC is shown in Figure 4.

It contains the following elements:

A sample-hold amplifier

A differential amplifier or subtracter

An analog low-pass filter

A 1-bit ADC (comparator)

A 1-bit DAC

ANALOG

LOW-PASS

FILTER

DAC

DIGITAL

FILTER

DIGITAL DATA

COMPARATOR

S/H AMP

Figure 4. General

-

ADC

In operation, the analog signal sample is fed to the subtracter,

along with the output of the 1-bit DAC. The filtered difference

signal is fed to the comparator, whose output samples the differ-

ence signal at a frequency many times that of the analog signal

sampling frequency (oversampling).

Oversampling is fundamental to the operation of -

ADCs.

Using the quantization noise formula for an ADC

SNR

Number of Bits

dB

=×

+

()

602

1 76

..

a 1-bit ADC or comparator yields an SNR of 7.78 dB.

The AD7713 samples the input signal at a frequency of 7.8 kHz

or greater (see Table III). As a result, the quantization noise is

spread over a much wider frequency than that of the band of

interest. The noise in the band of interest is reduced still fur-

ther by analog filtering in the modulator loop, which shapes

the quantization noise spectrum to move most of the noise

energy to frequencies outside the bandwidth of interest. The

noise performance is thus improved from this 1-bit level to the

performance outlined in Tables I and II and in Figures 2a and 2b.

The output of the comparator provides the digital input for the

1-bit DAC, so that the system functions as a negative feedback

loop that tries to minimize the difference signal. The digital data

that represents the analog input voltage is contained in the duty

cycle of the pulse train appearing at the output of the compara-

tor. It can be retrieved as a parallel binary data-word using a

digital filter.

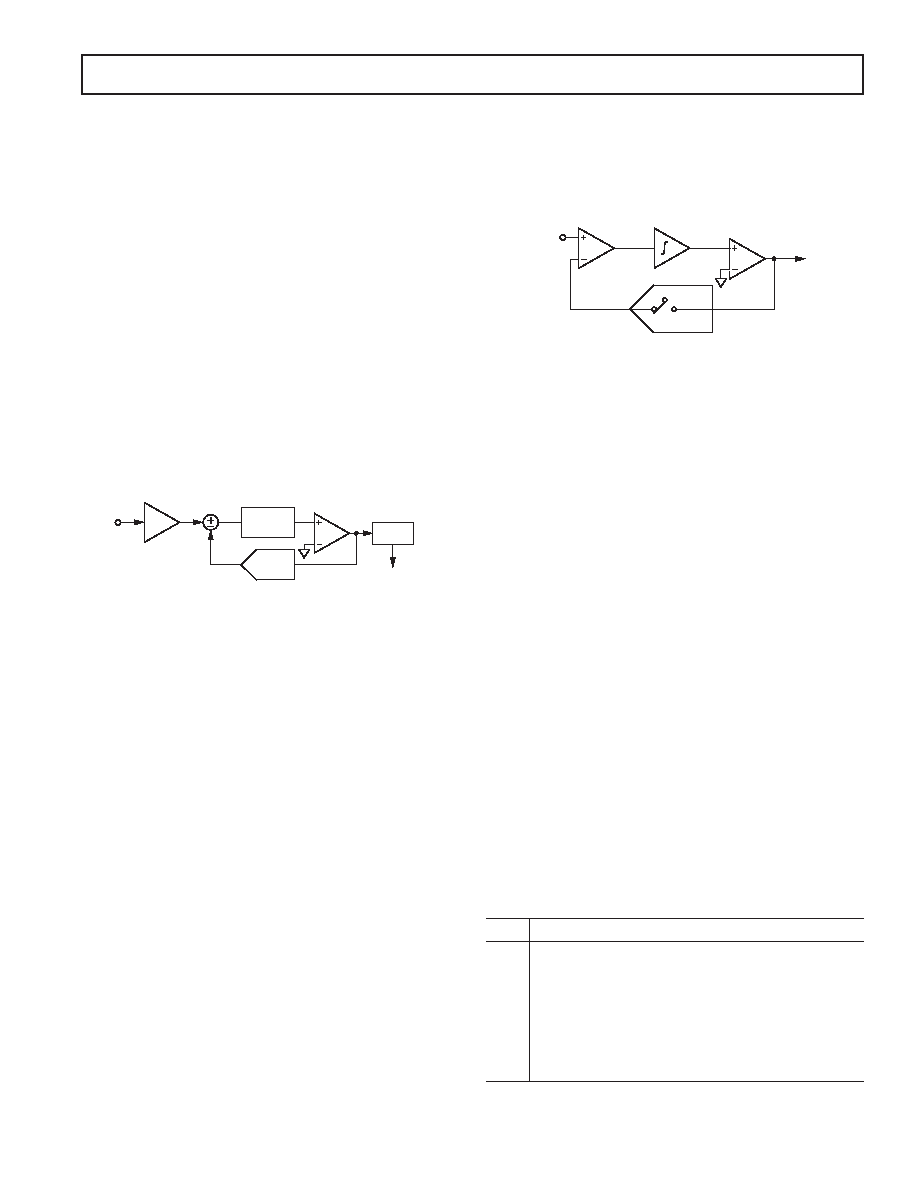

-

ADCs are generally described by the order of the analog

low-pass filter. A simple example of a first-order -

ADC is

shown in Figure 5. This contains only a first-order low-pass

filter or integrator. It also illustrates the derivation of the alter-

native name for these devices: charge balancing ADCs.

COMPARATOR

DIFFERENTIAL

AMPLIFIER

INTEGRATOR

+FS

–FS

DAC

VIN

Figure 5. Basic Charge-Balancing ADC

It consists of a differential amplifier (whose output is the differ-

ence between the analog input and the output of a 1-bit DAC),

an integrator, and a comparator. The term charge balancing comes

from the fact that this system is a negative feedback loop that tries

to keep the net charge on the integrator capacitor at 0 by balanc-

ing charge injected by the input voltage with charge injected by

the 1-bit DAC. When the analog input is 0, the only contribu-

tion to the integrator output comes from the 1-bit DAC. For the

net charge on the integrator capacitor to be 0, the DAC output

must spend half its time at +FS and half its time at –FS. Assum-

ing ideal components, the duty cycle of the comparator will be 50%.

When a positive analog input is applied, the output of the 1-bit

DAC must spend a larger proportion of the time at +FS, so the

duty cycle of the comparator increases. When a negative input

voltage is applied, the duty cycle decreases.

The AD7713 uses a second-order

-

modulator and a digital

filter that provides a rolling average of the sampled output.

After power-up or if there is a step change in the input voltage,

there is a settling time that must elapse before valid data is

obtained.

Input Sample Rate

The modulator sample frequency for the device remains at

fCLK IN/512 (3.9 kHz @ fCLK IN = 2 MHz) regardless of the

selected gain. However, gains greater than

1 are achieved by a

combination of multiple input samples per modulator cycle and

a scaling of the ratio of the reference capacitor to input capaci-

tor. As a result of the multiple sampling, the input the sample

rate of the device varies with the selected gain (see Table III).

The effective input impedance is 1/C

fS, where C is the input

sampling capacitance and fS is the input sample rate.

Table III. Input Sampling Frequency vs. Gain

Gain

Input Sampling Frequency (fS)

1fCLK IN/256 (7.8 kHz @ fCLK IN = 2 MHz)

22

fCLK IN/256 (15.6 kHz @ fCLK IN = 2 MHz)

44

fCLK IN/256 (31.2 kHz @ fCLK IN = 2 MHz)

88

fCLK IN/256 (62.4 kHz @ fCLK IN = 2 MHz)

16

8

fCLK IN/256 (62.4 kHz @ fCLK IN = 2 MHz)

32

8

fCLK IN/256 (62.4 kHz @ fCLK IN = 2 MHz)

64

8

fCLK IN/256 (62.4 kHz @ fCLK IN = 2 MHz)

128

8

fCLK IN/256 (62.4 kHz @ fCLK IN = 2 MHz)

相关PDF资料 |

PDF描述 |

|---|---|

| MS27467T9B44S | CONN PLUG 4POS STRAIGHT W/SCKT |

| AD977CRZ | IC ADC 16BIT 100KSPS 20SOIC |

| VI-2NR-MX-F1 | CONVERTER MOD DC/DC 7.5V 75W |

| AD7892ANZ-1 | IC ADC 12BIT LP 500KSPS 24DIP |

| VI-2NP-MX-F4 | CONVERTER MOD DC/DC 13.8V 75W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD7713SQ | 制造商:Analog Devices 功能描述: 制造商:Rochester Electronics LLC 功能描述: |

| AD7714 | 制造商:AD 制造商全称:Analog Devices 功能描述:3 V/5 V, CMOS, 500 uA Signal Conditioning ADC |

| AD7714ACHIPS-3 | 制造商:AD 制造商全称:Analog Devices 功能描述:3 V/5 V, CMOS, 500 uA Signal Conditioning ADC |

| AD7714ACHIPS-5 | 制造商:AD 制造商全称:Analog Devices 功能描述:3 V/5 V, CMOS, 500 uA Signal Conditioning ADC |

发布紧急采购,3分钟左右您将得到回复。