- 您现在的位置:买卖IC网 > PDF目录10212 > AD7731BRZ-REEL (Analog Devices Inc)IC ADC 24BIT SIGMA-DELTA 24-SOIC PDF资料下载

参数资料

| 型号: | AD7731BRZ-REEL |

| 厂商: | Analog Devices Inc |

| 文件页数: | 18/44页 |

| 文件大小: | 0K |

| 描述: | IC ADC 24BIT SIGMA-DELTA 24-SOIC |

| 标准包装: | 1,000 |

| 位数: | 24 |

| 采样率(每秒): | 6.4k |

| 数据接口: | DSP,串行,SPI? |

| 转换器数目: | 1 |

| 功率耗散(最大): | 125mW |

| 电压电源: | 模拟和数字 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 24-SOIC(0.295",7.50mm 宽) |

| 供应商设备封装: | 24-SOIC W |

| 包装: | 带卷 (TR) |

| 输入数目和类型: | 3 个差分,单极;3 个差分,双极;5 个伪差分,单极;5 个伪差分,双极 |

| 配用: | EVAL-AD7731EBZ-ND - BOARD EVALUATION FOR AD7731 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页当前第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页

AD7731

–25–

REV. 0

The operation mode can be changed to achieve optimum per-

formance in various applications. The CHP bit should generally

be set to 0 when using the AD7731 in applications where higher

throughput rates are a concern or in applications where the

reduced rejection at the chopping frequency in chop mode is an

issue. The part should be operated with CHP = 1 when drift,

noise rejection and optimum EMI rejection are important crite-

ria in the application.

The output update rate of the AD7731 is programmed using the

SF bits of the Filter Register. With CHP = 0, the output update

is determined by the relationship:

Output Rate

= f

MOD ×

1

SF

CHP

= 0

()

where SF is the decimal equivalent of the data loaded to the SF

bits of the Filter Register and fMOD is the modulator frequency

and is 1/16th of the master clock frequency.

With CHP = 1, the output update is determined by the relation-

ship:

Output Rate

= f

MOD ×

1

3

× SF

CHP

= 1

()

where SF is the decimal equivalent of the data loaded to the SF

bits of the Filter Register and fMOD is the modulator frequency

and is 1/16th of the master clock frequency.

Thus for a given SF word the output rate from the AD7731 is

three times faster with CHP = 0 than CHP = 1.

The various filter stages and options are discussed in the follow-

ing sections.

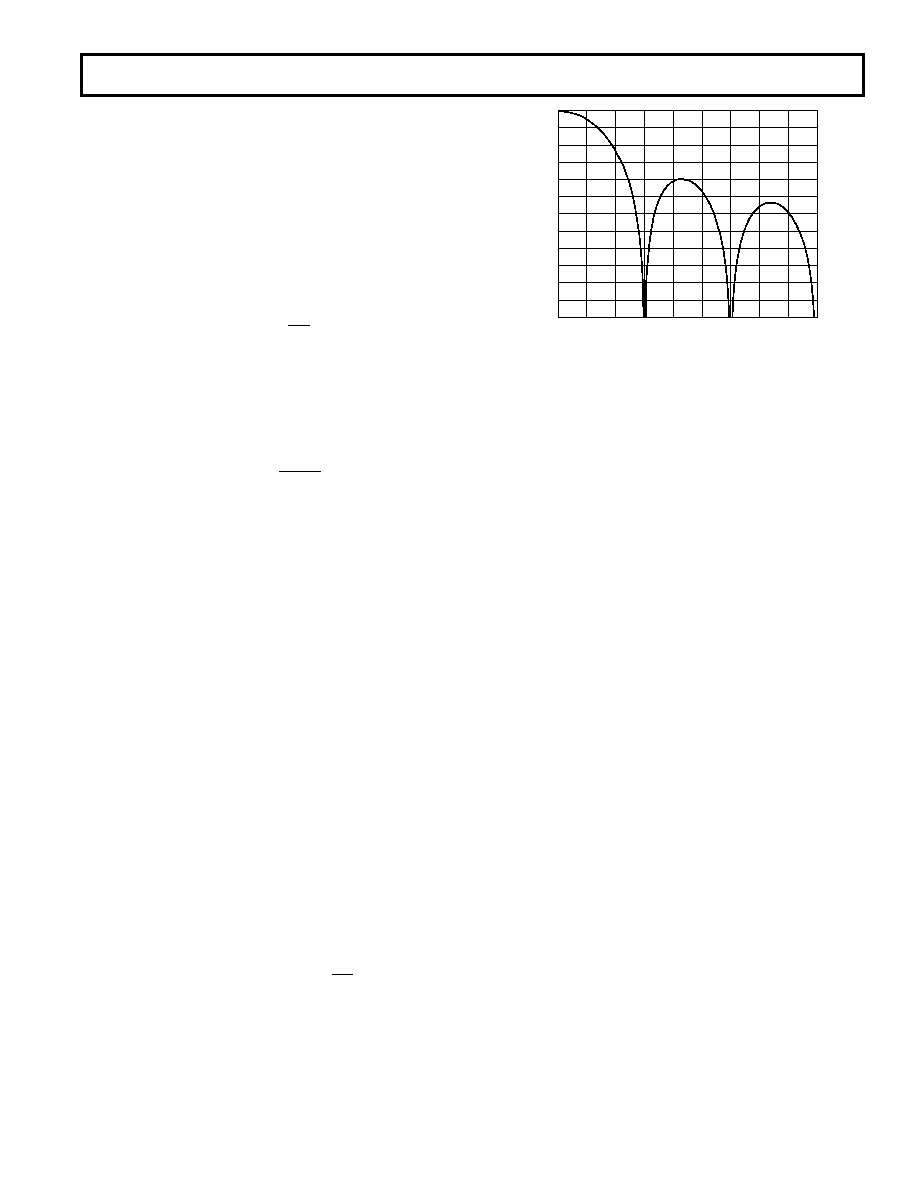

First Stage Filter/SKIP Mode Enabled (SKIP = 1)

With SKIP mode enabled, the only filtering on the part is the

first stage filter. The frequency response for this first stage filter

is shown in Figure 8. The response of this first stage filter is

similar to that of an averaging filter but with a sharper roll-off.

With CHP = 0, the output rate for the filter corresponds with

the positioning of the first notch of the filter’s frequency re-

sponse. Thus, for the plot of Figure 8 where the output rate is

600 Hz (fCLK IN = 4.9152 MHz and SF = 512), the first notch of

the filter is at 600 Hz. With CHP = 1, the magnitude response

is the same as in Figure 8 but in this case, the output rate is

1/3rd the output rate so for the example shown in Figure 8 the

output data rate is 200 Hz. The notches of this sinc

3 filter fre-

quency response are repeated at multiples of the first notch. The

filter provides attenuation of better than 100 dB around these

notches. Programming a different cutoff frequency via SF0 –

SF11 does not alter the profile of the filter response; it simply

changes the location of the notches. The –3 dB frequency for both

Chop and Nonchop modes is defined as:

f

3 dB = 0. 262 × f MOD ×

1

SF

Nonchop Mode (SKIP = 1, CHP = 0)

With CHP = 0, the input chopping on the AD7731 is disabled

and any offset content in the samples to the first stage filter are

all of the same polarity. When using the part in SKIP mode, the

user can take the output from the AD7731 directly. Time to the

first output for the part is 3

× 1/Output Rate in this mode. Table

XVIII summarizes the settling time and subsequent throughput

rate for the various different modes.

FREQUENCY – Hz

0

–60

–100

0

1800

GAIN

–

dB

200

400

600

800

1000

1200

1400

1600

–10

–50

–70

–90

–30

–40

–80

–20

–120

–110

Figure 8. SKIP Mode Frequency Response (SKIP = 1,

SF = 512)

Chop Mode (SKIP = 1, CHP = 1)

With CHP = 1, the AD7731 alternatively reverses the ADC

inputs, producing an output which contains the channel offset

when not reversed and the negative of the offset when reversed.

As a result, when operating in SKIP mode, the user has to take

two subsequent outputs from the AD7731 and average them to

produce a valid output from the first stage filter. While operat-

ing in this mode gives the benefits of chopping without the

longer settling time associated with the 22-tap FIR filter, care

should be taken with input signals near positive full-scale or

negative full-scale (zero-scale in unipolar mode). Since the

calibration coefficients are generated for the averaged offset, and

not for the individual offsets represented in each sample, one of

the two samples in the pair may record an all 1s or all 0s read-

ing. If this happens it will result in an error in the averaged

reading. Time to first output for the part is 1/Output Rate in

this mode. However, since the user really needs two outputs to

derive a correct chopped result, the time to get two outputs for

averaging is 2

× 1/Output Rate. Table XVIII summarizes the

settling time and subsequent throughput rate for the various

different modes. If the user wants the benefits of chopping with-

out the longer settling time associated with the 22-tap FIR filter,

it is recommended that the part be used in FASTStep mode.

Second Stage Filter

With SKIP mode disabled, the second stage filter is included in

the signal processing. This second stage filter produces a differ-

ent response depending on the CHP and FAST bits.

Normal FIR Operation (SKIP = 0)

The normal mode of operation of the second stage filter is as a

22-tap low-pass FIR filter. This second stage filter processes the

output of the first stage filter and the net frequency response of

the filter is simply a product of the filter response of both filters.

The overall filter response of the AD7731 is guaranteed to have

no overshoot.

REV. A

相关PDF资料 |

PDF描述 |

|---|---|

| SP3076EEN-L/TR | IC TXRX RS485/RS422 ESD 14NSOIC |

| AD7667ACPZRL | IC ADC 16BIT UNIPOLAR 48LFCSP |

| SP3075EEN-L/TR | IC TXRX RS485/RS422 ESD 8NSOIC |

| AD7667ASTZRL | IC ADC 16BIT UNIPOLAR 48LQFP |

| SP3074EEN-L/TR | IC TXRX RS485/RS422 ESD 8NSOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD7731BRZ-REEL7 | 功能描述:IC ADC 24BIT SIGMA-DELTA 24-SOIC RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1,000 系列:- 位数:12 采样率(每秒):300k 数据接口:并联 转换器数目:1 功率耗散(最大):75mW 电压电源:单电源 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:24-SOIC(0.295",7.50mm 宽) 供应商设备封装:24-SOIC 包装:带卷 (TR) 输入数目和类型:1 个单端,单极;1 个单端,双极 |

| AD7731EB | 制造商:AD 制造商全称:Analog Devices 功能描述:Low Noise High Throughput 24-Bit Sigma-Delta ADC(411.99 k) |

| AD7732 | 制造商:AD 制造商全称:Analog Devices 功能描述:2-Channel, +-10 V Input Range, High Throughput, 24-Bit SIGMA- ADC |

| AD7732BRU | 功能描述:IC ADC 24BIT 2-CH 28-TSSOP RoHS:否 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1,000 系列:- 位数:12 采样率(每秒):300k 数据接口:并联 转换器数目:1 功率耗散(最大):75mW 电压电源:单电源 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:24-SOIC(0.295",7.50mm 宽) 供应商设备封装:24-SOIC 包装:带卷 (TR) 输入数目和类型:1 个单端,单极;1 个单端,双极 |

| AD7732BRU-REEL | 制造商:Analog Devices 功能描述:ADC Single Delta-Sigma 15.437ksps 24-bit Serial 28-Pin TSSOP T/R 制造商:Analog Devices 功能描述:ADC SGL DELTA-SIGMA 15.437KSPS 24BIT SERL 28TSSOP - Tape and Reel |

发布紧急采购,3分钟左右您将得到回复。