参数资料

| 型号: | AD8155ACPZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 11/36页 |

| 文件大小: | 0K |

| 描述: | IC MUX/DEMUX DUAL BUFFER 64LFCSP |

| 标准包装: | 1 |

| 系列: | XStream™ |

| 功能: | 多路复用器/多路分解器 |

| 电路: | 2 x 2:1 |

| 电压电源: | 单电源 |

| 电压 - 电源,单路/双路(±): | 1.6 V ~ 3.6 V |

| 电流 - 电源: | 735mA |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 64-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 64-LFCSP-VQ(9x9) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页当前第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页

AD8155

Rev. 0 | Page 19 of 36

Lane Disables

By default, the receivers and transmitters enable in an on-demand

fashion according to the state of the SEL[1:0], LB_[A:C], and

BICAST pins or to the state of the equivalent registers in serial

control mode. Register 0x40, Register 0x80, and Register 0xC0

implement per-lane disables for the receivers, and Register 0x48,

Register 0x88, and Register 0xC8 implement per-lane transmit-

ter disables. These disables override the default settings. Each

bit in the register is named for the lane and function it disables.

For example, RXDIS B0 disables the receiver on Lane 0 of Port B

whereas TXDIS C1 disables the Lane 1 transmitter of Port C

(see Table 11).

Lane Inversion: P/N Swap

The receiver P/N swap function is a convenience intended to

allow the user to implement the equivalent of a board-level

routing crossover in a much smaller area while eliminating vias

(impedance discontinuities) that compromise the high frequency

integrity of the signal path. Using this feature to correct an

inversion downstream of the receiver may require the user to be

aware of the sign of the data when switching connectivity (the

mux/demux path). The feature is available on a per-lane setting

through Register 0x44, Register 0x84, and Register 0xC4.

Setting the bit true flips the sign sense of the P and N inputs for

the associated lane. The default setting is 0 (no inversion).

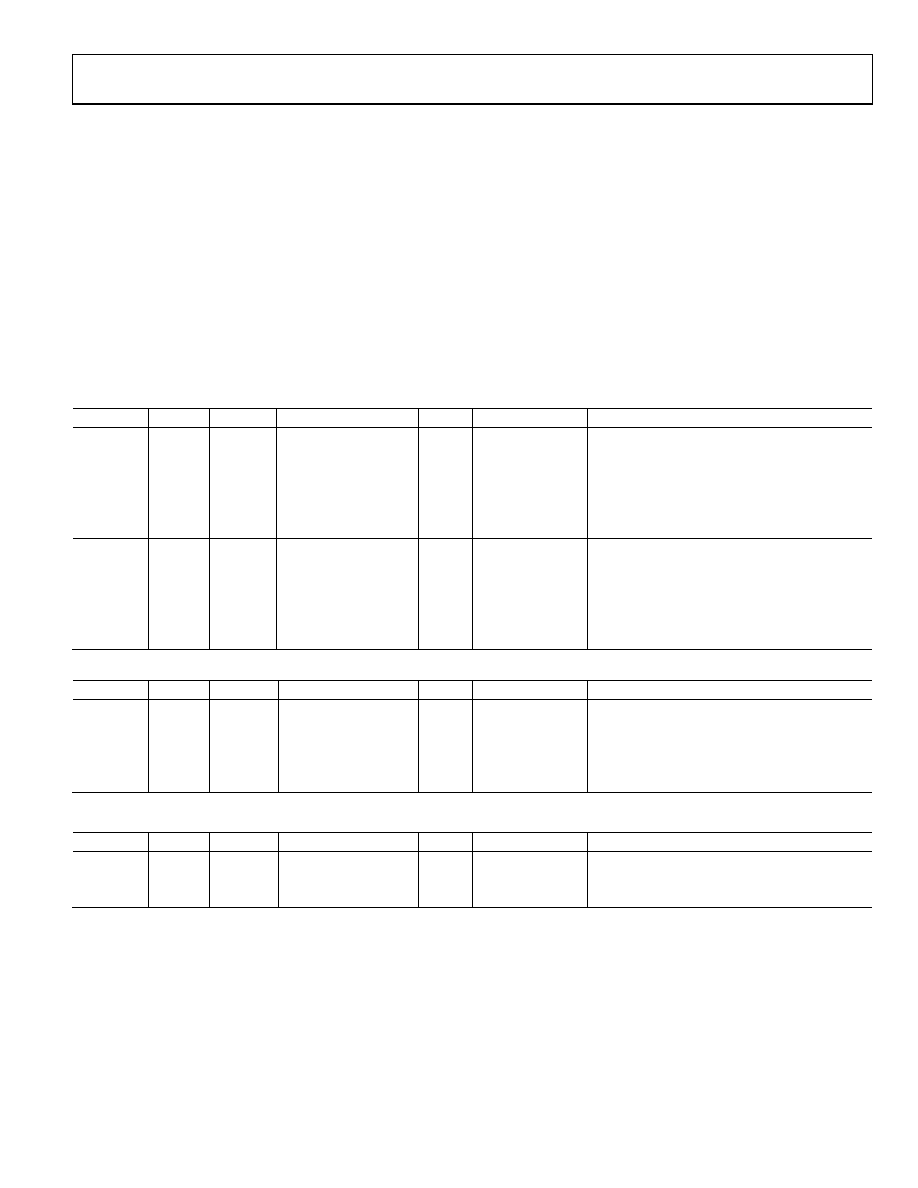

Table 11. Per-Lane Disables

Address

Port

Default

Register Name

Bit

Bit Name

Functionality Description

0x40

Port A

0x00

RX[A/B/C] disable

7:4

Reserved

Set to 0

0x80

Port B

0x00

3:2

Reserved

0xC0

Port C

0x00

1

RXDIS [A/B/C]1

0: RX Port [A/B/C], Lane 1, enabled

1: RX Port [A/B/C], Lane 1, disabled

0

RXDIS [A/B/C]0

0: RX Port [A/B/C], Lane 0, enabled

1: RX Port [A/B/C], Lane 0, disabled

0x48

Port A

0x00

TX[A/B/C] disable

7:4

Reserved

Set to 0

0x88

Port B

0x00

3:2

Reserved

0xC8

Port C

0x00

1

TXDIS [A/B/C]1

0: TX Port [A/B/C], Lane 1, enabled

1: TX Port [A/B/C], Lane 1, disabled

0

TXDIS [A/B/C]0

0: TX Port [A/B/C], Lane 0, enabled

1: TX Port [A/B/C], Lane 0, disabled

Table 12. Lane Inversion

Address

Port

Default

Register Name

Bit

Bit Name

Functionality Description

0x44

Port A

0x00

RX[A/B/C] P/N swap

7:2

Reserved

Set to 0

0x84

Port B

0x00

1

PN[A/B/C]1

0: Lane 1, noninverted

1: Lane 1, inverted

0xC4

Port C

0x00

0

PN[A/B/C]0

0: Lane 0, noninverted

1: Lane 0, inverted

Table 13. Port-Level EQ Setting

Address

Port

Default

Register Name

Bit

Bit Name

Functionality Description

0x41

Port A

0x00

RX[A/B/C] EQ setting

7:4

Reserved

Set to 0

0x81

Port B

0x00

3:0

[A/B/C]EQ[3:0]

0xC1

Port C

0x00

相关PDF资料 |

PDF描述 |

|---|---|

| AD8156ABCZ | IC SWITCH XPT 4X4 W/EQ 49CSPBGA |

| AD8158ACPZ | IC MUX/DEMUX QUAD 2X1 100LFCSP |

| AD8159ASVZ | IC MUX/DEMUX QUAD BUFF 100TQFP |

| AD8174ANZ | IC MUX SW W/AMP 250MHZ 14-DIP |

| AD8175ABPZ | IC CROSSPOINT SWITCH TRPL 676BGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD8155ACPZ-R7 | 功能描述:IC MUX/DEMUX DUAL BUFFER 64LFCSP RoHS:是 类别:集成电路 (IC) >> 接口 - 模拟开关,多路复用器,多路分解器 系列:XStream™ 其它有关文件:STG4159 View All Specifications 标准包装:5,000 系列:- 功能:开关 电路:1 x SPDT 导通状态电阻:300 毫欧 电压电源:双电源 电压 - 电源,单路/双路(±):±1.65 V ~ 4.8 V 电流 - 电源:50nA 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:7-WFBGA,FCBGA 供应商设备封装:7-覆晶 包装:带卷 (TR) |

| AD8155-EVALZ | 制造商:AD 制造商全称:Analog Devices 功能描述:6.5 Gbps Dual Buffer Mux/Demux |

| AD8155XCPZ | 制造商:Analog Devices 功能描述: |

| AD8156 | 制造商:AD 制造商全称:Analog Devices 功能描述:6.25 Gbps 4】4 Digital Crosspoint Switch with EQ |

| AD8156ABCZ | 功能描述:IC SWITCH XPT 4X4 W/EQ 49CSPBGA RoHS:是 类别:集成电路 (IC) >> 接口 - 专用 系列:XStream™ 特色产品:NXP - I2C Interface 标准包装:1 系列:- 应用:2 通道 I²C 多路复用器 接口:I²C,SM 总线 电源电压:2.3 V ~ 5.5 V 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:剪切带 (CT) 安装类型:表面贴装 产品目录页面:825 (CN2011-ZH PDF) 其它名称:568-1854-1 |

发布紧急采购,3分钟左右您将得到回复。