参数资料

| 型号: | AD9510BCPZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 7/56页 |

| 文件大小: | 0K |

| 描述: | IC CLOCK DIST 8OUT PLL 64LFCSP |

| 标准包装: | 1 |

| 类型: | 扇出缓冲器(分配),除法器 |

| PLL: | 是 |

| 输入: | 时钟 |

| 输出: | CMOS,LVDS,LVPECL |

| 电路数: | 1 |

| 比率 - 输入:输出: | 2:8 |

| 差分 - 输入:输出: | 是/是 |

| 频率 - 最大: | 1.2GHz |

| 除法器/乘法器: | 是/无 |

| 电源电压: | 3.135 V ~ 3.465 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 64-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 64-LFCSP-VQ(9x9) |

| 包装: | 托盘 |

| 配用: | AD9510-VCO/PCBZ-ND - BOARD EVALUATION FOR AD9510 AD9510/PCBZ-ND - BOARD EVALUATION FOR AD9510 |

第1页第2页第3页第4页第5页第6页当前第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页

Data Sheet

AD9510

Rev. B | Page 15 of 56

POWER

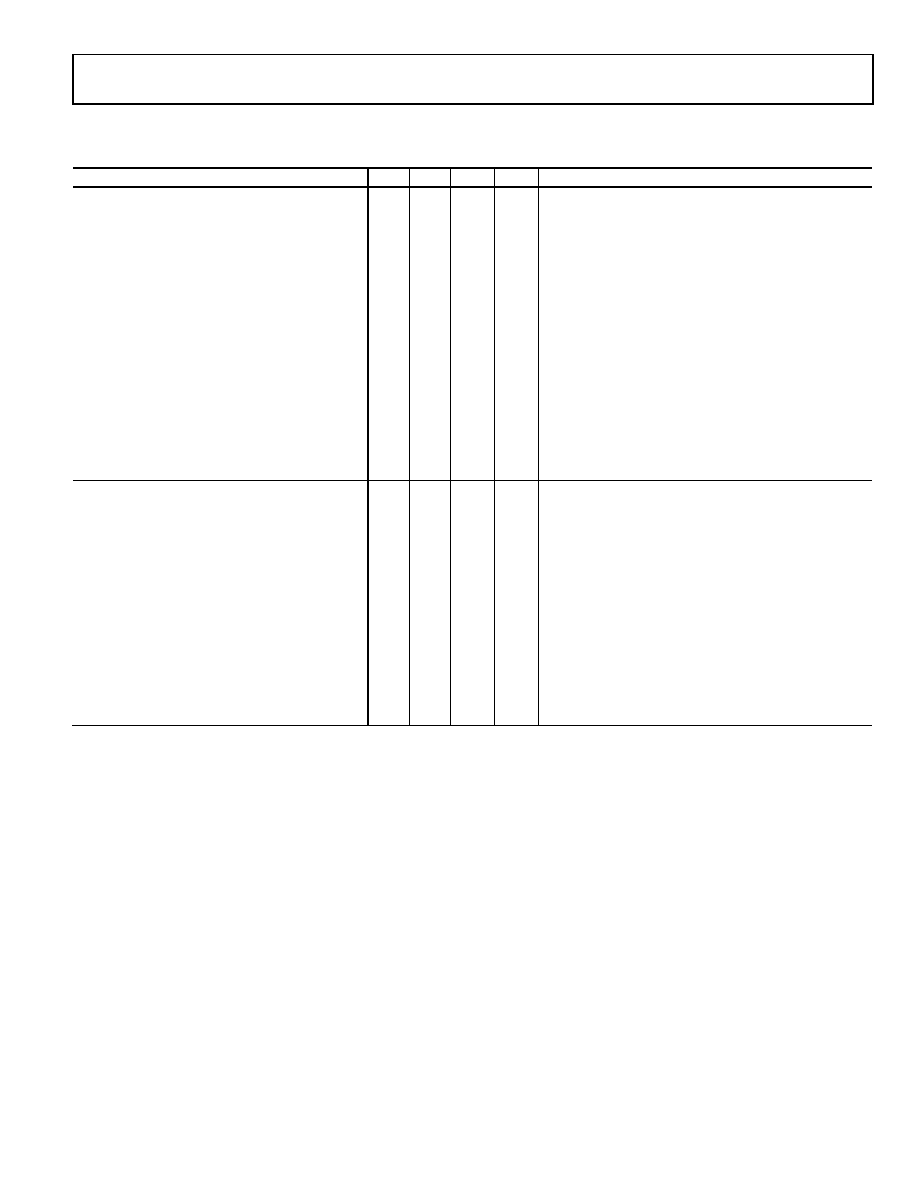

Table 11.

Parameter

Min

Typ

Max

Unit

Test Conditions/Comments

POWER-UP DEFAULT MODE POWER DISSIPATION

550

600

mW

Power-up default state, does not include power

dissipated in output load resistors; no clock

Power Dissipation

1.1

W

All outputs on; four LVPECL outputs at 800 MHz, 4 LVDS

out at 800 MHz; does not include power dissipated in

external resistors

Power Dissipation

1.3

W

All outputs on; four LVPECL outputs at 800 MHz, 4 CMOS

out at 62 MHz (5 pF load); does not include power

dissipated in external resistors

Power Dissipation

1.5

W

All outputs on; four LVPECL outputs at 800 MHz, 4 CMOS

out at 125 MHz (5 pF load); does not include power

dissipated in external resistors

Full Sleep Power-Down

35

60

mW

Maximum sleep is entered by setting Register 0x0A[1:0] =

01b and Register 0x58[4] = 1b; this powers off the PLL BG

and the distribution BG references; does not include

power dissipated in terminations

Power-Down (PDB)

60

80

mW

Set the FUNCTION pin for PDB operation by setting

Register 0x58[6:5] = 11b; pull PDB low; does not include

power dissipated in terminations

POWER DELTA

CLK1, CLK2 Power-Down

10

15

25

mW

Divider, DIV 2 32 to Bypass

23

27

33

mW

For each divider

LVPECL Output Power-Down (PD2, PD3)

50

65

75

mW

For each output; does not include dissipation in

termination (PD2 only)

LVDS Output Power-Down

80

92

110

mW

For each output

CMOS Output Power-Down (Static)

56

70

85

mW

For each output; static (no clock)

CMOS Output Power-Down (Dynamic)

115

150

190

mW

For each CMOS output, single-ended; clocking at

62 MHz with 5 pF load

CMOS Output Power-Down (Dynamic)

125

165

210

mW

For each CMOS output, single-ended; clocking at

125 MHz with 5 pF load

Delay Block Bypass

20

24

60

mW

Versus delay block operation at 1 ns fs with maximum

delay, output clocking at 25 MHz

PLL Section Power-Down

5

15

40

mW

相关PDF资料 |

PDF描述 |

|---|---|

| VI-BWF-MW-B1 | CONVERTER MOD DC/DC 72V 100W |

| AD9520-5BCPZ | IC CLOCK GEN EXT VCO 64-LFCSP |

| M83723/83G1203N | CONN RCPT 3POS WALL MT W/PINS |

| X9116WM8 | IC DIGITAL POT 10K 16TP 8MSOP |

| MS27467E25F35SD | CONN PLUG 128POS STRAIGHT W/SCKT |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9510BCPZ-REEL7 | 功能描述:IC CLOCK DIST 8OUT PLL 64LFCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:2,000 系列:- 类型:PLL 时钟发生器 PLL:带旁路 输入:LVCMOS,LVPECL 输出:LVCMOS 电路数:1 比率 - 输入:输出:2:11 差分 - 输入:输出:是/无 频率 - 最大:240MHz 除法器/乘法器:是/无 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:32-LQFP 供应商设备封装:32-TQFP(7x7) 包装:带卷 (TR) |

| AD9510-VCO/PCB | 制造商:Analog Devices 功能描述:EVAL BD FOR 1.2 GHZ CLOCK DISTRIBUTION IC, PLL CORE, DIVIDER - Bulk 制造商:Analog Devices 功能描述:IC ((NS)) |

| AD9510-VCO/PCBZ | 功能描述:BOARD EVALUATION FOR AD9510 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 标准包装:1 系列:PSoC® 主要目的:电源管理,热管理 嵌入式:- 已用 IC / 零件:- 主要属性:- 次要属性:- 已供物品:板,CD,电源 |

| AD9511 | 制造商:AD 制造商全称:Analog Devices 功能描述:1.2 GHz Clock Distribution IC, PLL Core, Dividers, Delay Adjust, Five Outputs |

| AD9511/PCB | 制造商:Analog Devices 功能描述:1.2 GHZ CLOCK DISTRIBUTION IC, PLL CORE,DIVIDERS, DELAY ADJUST, FIVE OUTPUTS 制造商:Analog Devices 功能描述:EVAL BD FOR AD9511 1.2 GHZ CLOCK DISTRIBUTION IC, PLL CORE,D - Bulk |

发布紧急采购,3分钟左右您将得到回复。