参数资料

| 型号: | AD9552BCPZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 10/32页 |

| 文件大小: | 0K |

| 描述: | IC PLL CLOCK GEN LP 32LFCSP |

| 设计资源: | Clock Distribution Circuit with Pin-Programmable Output Frequency, Output Logic Levels, and Fanout (CN0152) |

| 标准包装: | 1 |

| 类型: | 时钟发生器 |

| PLL: | 带旁路 |

| 输入: | CMOS,晶体 |

| 输出: | CMOS,LVDS,LVPECL |

| 电路数: | 1 |

| 比率 - 输入:输出: | 2:2 |

| 差分 - 输入:输出: | 无/是 |

| 频率 - 最大: | 900MHz |

| 除法器/乘法器: | 是/无 |

| 电源电压: | 3.135 V ~ 3.465 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 32-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 32-LFCSP-VQ(5x5) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页当前第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页

AD9552

Data Sheet

Rev. E | Page 18 of 32

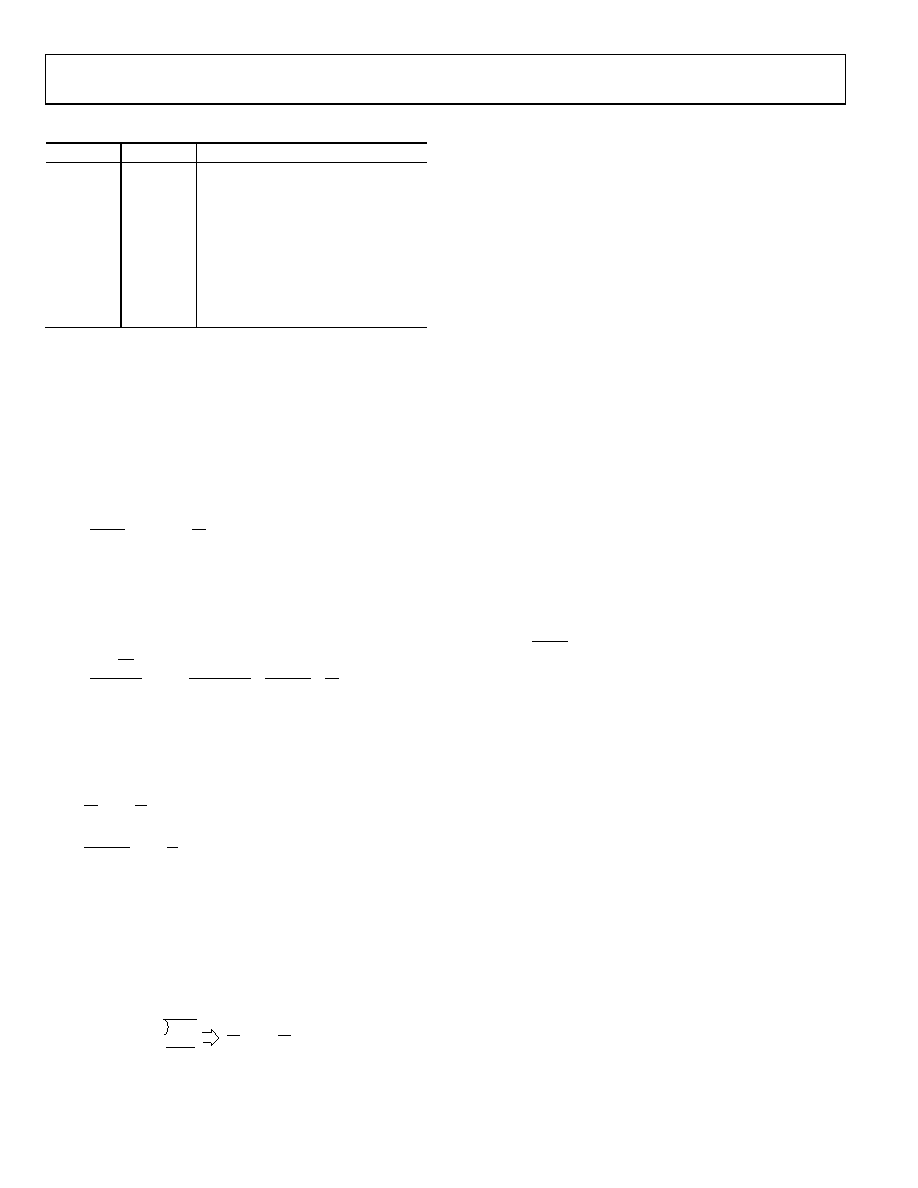

Table 12. Combinations for P0 and P1

P

0

P

1

ODF (P

0 × P1)

4

9

36

4

10

40

5

7

35

5

8

40

6

36

7

5

35

8

5

40

9

4

36

10

4

40

The P0 and P1 combinations listed in Table 12 are all equally

valid. However, note that they yield only three valid ODF

values (35, 36, and 40) from the original range of 34 to 40.

3. Determine the feedback divider values for the PLL.

Repeat this step for each ODF when multiple ODFs exist

(for example, 35, 36, and 40 in the case of Table 12).

To calculate the feedback divider values for a given ODF,

use the following equation:

Y

X

ODF

f

REF

OUT

=

×

1

Note that the left side of the equation contains variables with

known quantities. Furthermore, the values are necessarily

rational, so the left side is expressible as a ratio of two inte-

gers, X and Y. Following is an example equation.

Y

X

=

×

1664

500

,

247

)

64

(

26

)

6

)(

66

(

625

6

26

64

66

625

In the context of the AD9552, X/Y is always an improper

fraction. Therefore, it is expressible as the sum of an integer,

N, and the proper fraction, R/Y (R and Y are integers).

Y

R

N

Y

X

+

=

Y

R

N

+

=

1664

500

,

247

This particular example yields N = 148, Y = 1664, and

R = 1228. To arrive at this result, use long division to convert

the improper fraction, X/Y, to an integer (N) and a proper

fraction (R/Y). Note that dividing Y into X by means of

long division yields an integer, N, and a remainder, R. The

proper fraction has a numerator (R, the remainder) and a

denominator (Y, the divisor), as shown in Figure 21.

07806-

005

Y X

N

R

–NY

= N +

X

Y

R

Y

Figure 21. Example Long Division

It is imperative that long division be used to obtain the correct

results. Avoid the use of a calculator or math program, because

these do not always yield correct results due to internal rounding

and/or truncation. Some calculators or math programs may be up

to the task if they can handle very large integer operations, but such

are not common.

In the example, N = 148 and R/Y = 1228/1664, which reduces

to R/Y = 307/416. These values of N, R, and Y constitute the

following respective feedback divider values:

N = 148, FRAC = 307, and MOD = 416.

The only caveat is that N and MOD must meet the constraints

given in the Output/Input Frequency Relationship section.

In the example, FRAC is nonzero, so the division value is an

integer plus the fractional component, FRAC/MOD. This

implies that the feedback SDM is necessary as part of the

feedback divider. If FRAC = 0, the feedback division factor

is an integer and the SDM is not required (it can be bypassed).

Although the feedback divider values obtained in this way

provide the proper feedback divide ratio to synthesize the exact

output frequency, they may not yield optimal jitter performance

at the final output. One reason for this is that the value of MOD

defines the period of the SDM, which has a direct impact on the

spurious output of the SDM. Specifically, in the spectral band

from dc to fPFD, the SDM exhibits spurs at intervals of fPFD/

MOD. Thus, the spectral separation (Δf) of the spurs associated

with the feedback SDM is

MOD

f

PFD

=

Because the SDM is in the feedback path of the PLL, these spurs

appear in the output signal as spurious components offset by Δf

from fOUT1. Therefore, a small MOD value pro-duces relatively

large spurs with relatively large frequency offsets from fOUT1,

whereas a large MOD value produces smaller spurs but more

closely spaced to fOUT1. Clearly, the value of MOD has a direct

impact on the spurious content (that is, jitter) at OUT1.

Generally, the largest possible MOD value yields the smallest spurs.

Thus, it is desirable to scale MOD and FRAC by the integer part

of 220 divided by the value of MOD obtained previously. In the

example, the value of MOD is 416, yield-ing a scale factor of 2520

(the integer part of 220/416). A scale factor of 2520 leads to FRAC

= 307 × 2520 = 773,640 and MOD = 416 × 2520 = 1,048,320.

LOW DROPOUT (LDO) REGULATORS

The AD9552 is powered from a single 3.3 V supply and contains

on-chip LDO regulators for each function to eliminate the need

for external LDOs. To ensure optimal performance, each LDO

output should have a 0.47 μF capacitor connected between its

access pin and ground, and this capacitor should be kept as

close to the device as possible.

相关PDF资料 |

PDF描述 |

|---|---|

| VE-JVR-MZ-S | CONVERTER MOD DC/DC 7.5V 25W |

| ISL90841UIV1427Z | IC XDCP 256-TAP 50KOHM TSSOP-14 |

| SY100EP140LZG | IC FREQUENCY DETECTOR 3.3V 8SOIC |

| VE-JVP-MZ-S | CONVERTER MOD DC/DC 13.8V 25W |

| VI-B13-MY-F3 | CONVERTER MOD DC/DC 24V 50W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9552BCPZ | 制造商:Analog Devices 功能描述:IC PLL CLOCK GENERATOR 112.5MHZ LFCSP-32 |

| AD9552BCPZ-REEL7 | 功能描述:IC PLL CLOCK GEN LP 32LFCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:1,000 系列:Precision Edge® 类型:时钟/频率合成器 PLL:无 输入:CML,PECL 输出:CML 电路数:1 比率 - 输入:输出:2:1 差分 - 输入:输出:是/是 频率 - 最大:10.7GHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-VFQFN 裸露焊盘,16-MLF? 供应商设备封装:16-MLF?(3x3) 包装:带卷 (TR) 其它名称:SY58052UMGTRSY58052UMGTR-ND |

| AD9552PCBZ | 制造商:AD 制造商全称:Analog Devices 功能描述:Oscillator Frequency Upconverter |

| AD9553 | 制造商:AD 制造商全称:Analog Devices 功能描述:Flexible Clock Translator for GPON, Base Station, SONET/SDH, T1/E1, and Ethernet |

| AD9553/PCBZ | 功能描述:BOARD EVAL FOR AD9553 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 标准包装:1 系列:- 主要目的:电信,线路接口单元(LIU) 嵌入式:- 已用 IC / 零件:IDT82V2081 主要属性:T1/J1/E1 LIU 次要属性:- 已供物品:板,电源,线缆,CD 其它名称:82EBV2081 |

发布紧急采购,3分钟左右您将得到回复。