参数资料

| 型号: | AD9552BCPZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 8/32页 |

| 文件大小: | 0K |

| 描述: | IC PLL CLOCK GEN LP 32LFCSP |

| 设计资源: | Clock Distribution Circuit with Pin-Programmable Output Frequency, Output Logic Levels, and Fanout (CN0152) |

| 标准包装: | 1 |

| 类型: | 时钟发生器 |

| PLL: | 带旁路 |

| 输入: | CMOS,晶体 |

| 输出: | CMOS,LVDS,LVPECL |

| 电路数: | 1 |

| 比率 - 输入:输出: | 2:2 |

| 差分 - 输入:输出: | 无/是 |

| 频率 - 最大: | 900MHz |

| 除法器/乘法器: | 是/无 |

| 电源电压: | 3.135 V ~ 3.465 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 32-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 32-LFCSP-VQ(5x5) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页当前第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页

AD9552

Data Sheet

Rev. E | Page 16 of 32

The gain of the PLL is proportional to the current delivered

by the charge pump. The user can override the default charge

pump current setting, and, thereby, the PLL gain, by using

Register 0x0A[7:0].

The PLL has a VCO with 128 frequency bands spanning a range

of 3350 MHz to 4050 MHz (3700 MHz nominal). However, the

actual operating frequency within a particular band depends on

the control voltage that appears on the loop filter capacitor. The

control voltage causes the VCO output frequency to vary linearly

within the selected band. This frequency variability allows the

control loop of the PLL to synchronize the VCO output signal

with the reference signal applied to the PFD. Typically, selection

of the VCO frequency band (as well as gain adjustment) occurs

automatically as part of the device’s automatic VCO calibration

process, which initiates at power up (or reset). Alternatively, the

user can force VCO calibration by first enabling SPI control of

VCO calibration (Register 0x0E[2] = 1) and then writing a 1 to

the calibrate VCO bit (Register 0x0E[7]). To facilitate system

debugging, the user can override the VCO band setting by first

enabling SPI control of VCO band (Register 0x0E[0] = 1) and

then writing the desired value to Register 0x10[7:1].

The PLL has a feedback divider coupled with a third-order

SDM that enables the PLL to provide integer-plus-fractional

frequency upconversion. The integer factor, N, is variable via

an 8-bit programming register. The range of N is from NMIN to

255, where NMIN is 36 or 47 depending on whether the SDM is

disabled or enabled, respectively. The SDM in the feedback path

allows for a fractional divide value that takes the form of N +

F/M, where N is the integer part (eight bits), M is the modulus

(20 bits), and F is the fractional part (20 bits), with all three

parameters being positive integers.

The feedback SDM gives the AD9552 the ability to support a

wide range of output frequencies with exact frequency ratios

relative to the input reference.

PLL Locked Indicator

The PLL provides a status indicator that appears at an external

pin (LOCKED). The indicator shows when the PLL has acquired

a locked condition.

Output Dividers

Two integer dividers exist in the output chain. The first divider (P0)

yields an integer submultiple of the VCO frequency. The second

divider (P1) establishes the frequency at OUT1 as an integer

submultiple of the output frequency of the P0 divider.

Input-to-OUT2 Option

By default, OUT2 delivers an output frequency that is the same

frequency as OUT1. However, the user has the option of making

OUT2 a replica of the input frequency (REF or XTAL) by

programming Register 33[3] = 1.

Output Drivers

The user has control over the following output driver parameters

via the programming registers:

Logic family and pin functionality

Polarity (for CMOS family only)

Drive current

Power-down

The logic families are LVDS, LVPECL, and CMOS. Selection of

the logic family is via the mode control bits in the OUT1 driver

control register (Register 0x32[5:3]) and the OUT2 driver control

register (Register 0x34[5:3]), as detailed in Table 11. Regardless

of the selected logic family, each output driver uses two pins:

OUT1 and OUT1 are used by one driver, and OUT2 and OUT2

are used by the other. This enables support of the differential

signals associated with the LVDS and LVPECL logic families.

CMOS, on the other hand, is a single-ended signal requiring

only one output pin, but both output pins are available for

optional provision of a dual, single-ended CMOS output clock.

Refer to the first entry (CMOS (both pins)) in Table 11.

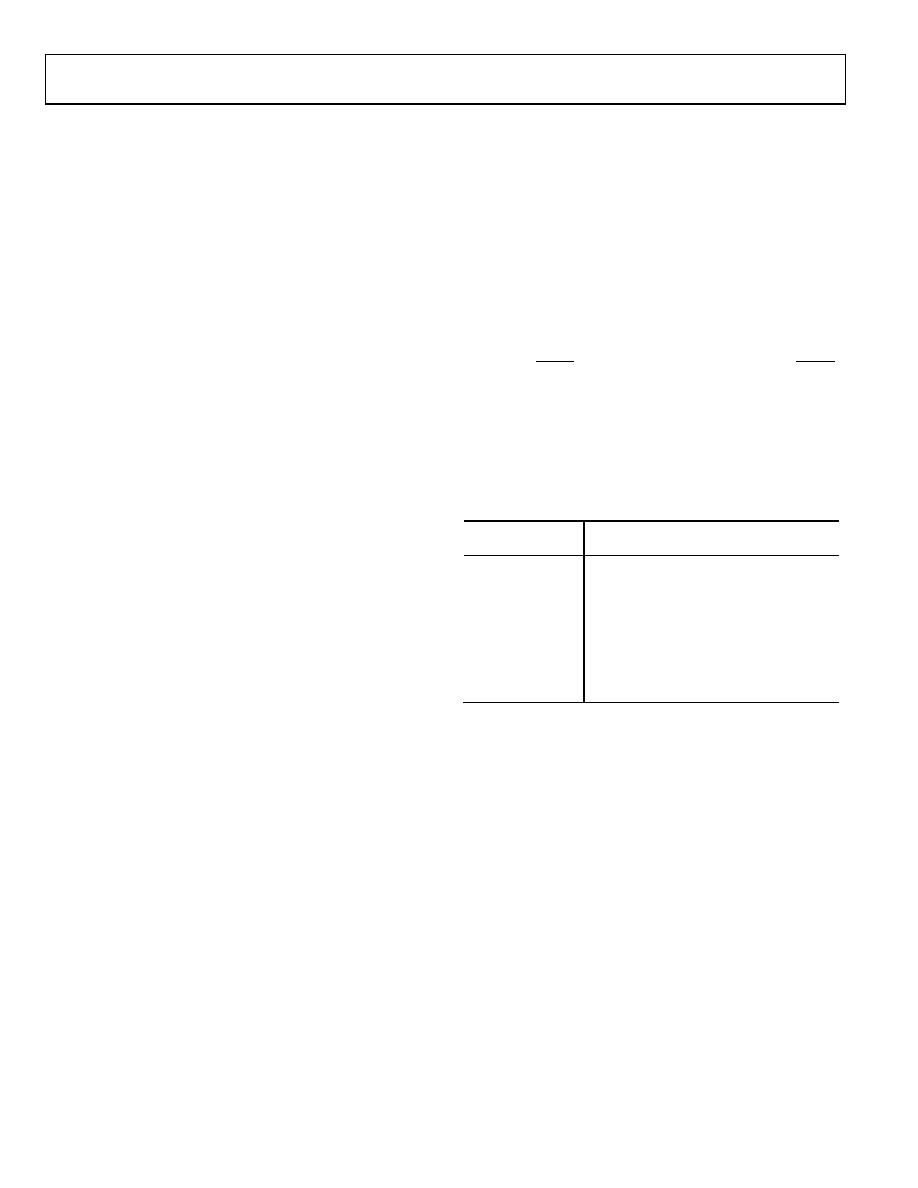

Table 11. Output Channel Logic Family and Pin Functionality

Mode

Control Bits[2:0]

Logic Family and Pin Functionality

000

CMOS (both pins)

001

CMOS (positive pin), tristate (negative pin)

010

Tristate (positive pin), CMOS (negative pin)

011

Tristate (both pins)

100

LVDS

101

LVPECL

110

Undefined

111

Undefined

If the mode bits indicate the CMOS logic family, the user has

control of the logic polarity associated with each CMOS output

pin via the OUT1 and OUT2 driver control registers.

If the mode bits indicate the CMOS or LVDS logic family, the

user can select whether the output driver uses weak or strong

drive capability via the OUT1 and OUT2 driver control registers.

In the case of the CMOS family, the strong setting allows for

driving increased capacitive loads. In the case of the LVDS

family, the nominal weak and strong drive currents are 3.5 mA

and 7 mA, respectively.

The OUT1 and OUT2 driver control registers also have a power-

down bit to enable/disable the output drivers. The power-down

function is independent of the logic family selection.

Note that, unless the user programs the device to allow SPI port

control of the output drivers, the drivers default to LVPECL or

LVDS, depending on the logic level on the OUTSEL pin (Pin 15).

For OUTSEL = 0, both outputs are LVDS. For OUTSEL = 1, both

outputs are LVPECL. In the pin-selected LVDS mode, the user

can still control the drive strength, using the SPI port.

相关PDF资料 |

PDF描述 |

|---|---|

| VE-JVR-MZ-S | CONVERTER MOD DC/DC 7.5V 25W |

| ISL90841UIV1427Z | IC XDCP 256-TAP 50KOHM TSSOP-14 |

| SY100EP140LZG | IC FREQUENCY DETECTOR 3.3V 8SOIC |

| VE-JVP-MZ-S | CONVERTER MOD DC/DC 13.8V 25W |

| VI-B13-MY-F3 | CONVERTER MOD DC/DC 24V 50W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9552BCPZ | 制造商:Analog Devices 功能描述:IC PLL CLOCK GENERATOR 112.5MHZ LFCSP-32 |

| AD9552BCPZ-REEL7 | 功能描述:IC PLL CLOCK GEN LP 32LFCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:1,000 系列:Precision Edge® 类型:时钟/频率合成器 PLL:无 输入:CML,PECL 输出:CML 电路数:1 比率 - 输入:输出:2:1 差分 - 输入:输出:是/是 频率 - 最大:10.7GHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-VFQFN 裸露焊盘,16-MLF? 供应商设备封装:16-MLF?(3x3) 包装:带卷 (TR) 其它名称:SY58052UMGTRSY58052UMGTR-ND |

| AD9552PCBZ | 制造商:AD 制造商全称:Analog Devices 功能描述:Oscillator Frequency Upconverter |

| AD9553 | 制造商:AD 制造商全称:Analog Devices 功能描述:Flexible Clock Translator for GPON, Base Station, SONET/SDH, T1/E1, and Ethernet |

| AD9553/PCBZ | 功能描述:BOARD EVAL FOR AD9553 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 标准包装:1 系列:- 主要目的:电信,线路接口单元(LIU) 嵌入式:- 已用 IC / 零件:IDT82V2081 主要属性:T1/J1/E1 LIU 次要属性:- 已供物品:板,电源,线缆,CD 其它名称:82EBV2081 |

发布紧急采购,3分钟左右您将得到回复。