- 您现在的位置:买卖IC网 > PDF目录1987 > AD9553BCPZ-REEL7 (Analog Devices Inc)IC INTEGER-N CLCK GEN 32LFCSP PDF资料下载

参数资料

| 型号: | AD9553BCPZ-REEL7 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 41/44页 |

| 文件大小: | 0K |

| 描述: | IC INTEGER-N CLCK GEN 32LFCSP |

| 标准包装: | 1,500 |

| 类型: | 时钟/频率转换器 |

| PLL: | 是 |

| 主要目的: | 以太网,GPON,SONET/SHD,T1/E1 |

| 输入: | CMOS,LVDS,晶体 |

| 输出: | CMOS,LVDS,LVPECL |

| 电路数: | 1 |

| 比率 - 输入:输出: | 1:2 |

| 差分 - 输入:输出: | 是/是 |

| 频率 - 最大: | 810MHz |

| 电源电压: | 3.135 V ~ 3.465 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 32-WFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 32-LFCSP(5x5) |

| 包装: | 带卷 (TR) |

| 配用: | AD9553/PCBZ-ND - BOARD EVAL FOR AD9553 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页当前第41页第42页第43页第44页

AD9553

Rev. A | Page 6 of 44

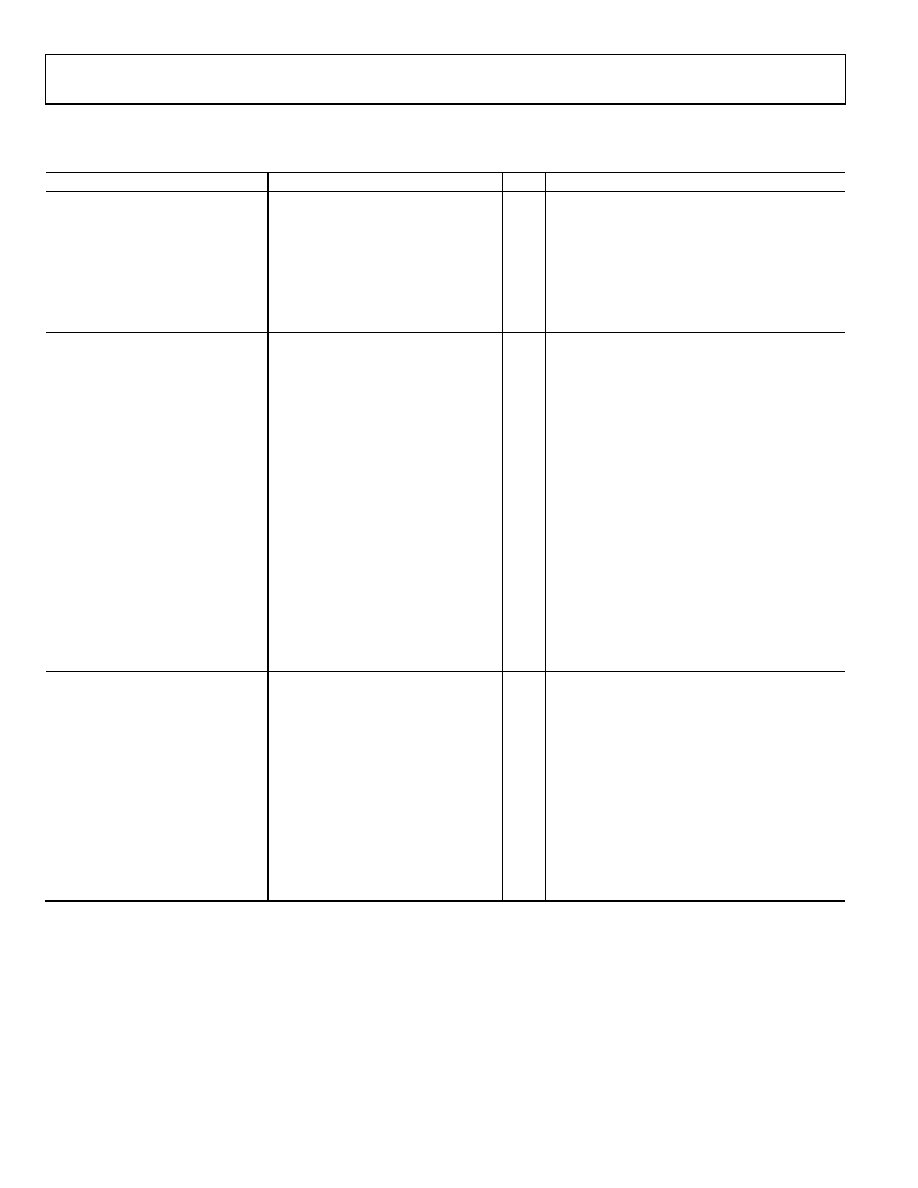

OUTPUT CHARACTERISTICS

Table 8.

Parameter

Min

Typ

Max

Unit

Test Conditions/Comments

LVPECL MODE

Differential Output Voltage Swing

690

800

890

mV

Output driver static (for dynamic performance, see

Common-Mode Output Voltage

VDD 1.66

VDD 1.34

VDD 1.01

V

Output driver static

Frequency Range

0

810

MHz

Duty Cycle

40

60

%

Up to 805 MHz output frequency

Rise/Fall Time1 (20% to 80%)

255

305

ps

100 Ω termination between both pins of the

output driver

LVDS MODE

Differential Output Voltage Swing

Output driver static (for dynamic performance, see

Balanced, V

OD

297

398

mV

Voltage swing between the pins of a differential

output pair with the output driver static

Unbalanced, ΔV

OD

8.3

mV

Absolute difference between voltage swing of

normal pin and inverted pin with the output

driver static

Offset Voltage

Common Mode, V

OS

1.17

1.35

V

(V

OH + VOL)/2 across a differential pair with output

driver static

Common-Mode Difference, ΔV

OS

7.3

mV

This is the absolute value of the difference

between V

OS when the normal output is high vs.

when the complementary output is high with

output driver static

Short-Circuit Output Current

17

24

mA

Output shorted to GND

Frequency Range

0

810

MHz

Duty Cycle

40

60

%

Up to 805 MHz output frequency

Rise/Fall Time1 (20% to 80%)

285

355

ps

100 Ω termination between both pins of the

output driver

CMOS MODE

Output Voltage High, V

OH

Output driver static; standard drive strength setting

I

OH = 10 mA

2.8

V

I

OH = 1 mA

2.8

V

Output Voltage Low, V

OL

Output driver static; standard drive strength setting

I

OL = 10 mA

0.5

V

I

OL = 1 mA

0.3

V

Frequency Range

0

200

MHz

3.3 V CMOS; standard drive strength setting;

output toggle rates in excess of the maximum are

possible, but with reduced amplitude (see Figure 17)

Duty Cycle

45

55

%

At maximum output frequency

Rise/Fall Time1 (20% to 80%)

500

745

ps

3.3 V CMOS; standard drive strength setting;

10 pF load

1 The listed values are for the slower edge (rise or fall).

相关PDF资料 |

PDF描述 |

|---|---|

| AD9557BCPZ-REEL7 | IC CLK XLATR PLL 1250MHZ 40LFCSP |

| AD9558BCPZ-REEL7 | IC CLK XLATR PLL 1250MHZ 64LFCSP |

| AD9571ACPZPEC-R7 | IC PLL CLOCK GEN 25MHZ 40LFCSP |

| AD9572ACPZLVD-R7 | IC PLL CLOCK GEN 25MHZ 40LFCSP |

| AD9573ARUZ-RL7 | IC PCI CLCOK GEN 25MHZ 16TSSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9554/PCBZ | 功能描述:AD9554 - Timing, Clock Generator Evaluation Board 制造商:analog devices inc. 系列:- 零件状态:有效 主要用途:计时,时钟发生器 嵌入式:- 使用的 IC/零件:AD9554 主要属性:- 辅助属性:LED 状态指示器 所含物品:板 标准包装:1 |

| AD9554-1/PCBZ | 功能描述:AD9554-1 - Timing, Clock Generator Evaluation Board 制造商:analog devices inc. 系列:- 零件状态:有效 主要用途:计时,时钟发生器 嵌入式:- 使用的 IC/零件:AD9554-1 主要属性:- 辅助属性:LED 状态指示器 所含物品:板 标准包装:1 |

| AD9554-1BCPZ | 功能描述:IC PLL CLOCK GEN 4OUT 72LFCSP 制造商:analog devices inc. 系列:- 包装:托盘 零件状态:有效 PLL:是 主要用途:以太网,SONET/SDH,Stratum 输入:CMOS,LVDS 输出:HCSL,LVDS,LVPECL 电路数:1 比率 - 输入:输出:4:4 差分 - 输入:输出:是/是 频率 - 最大值:942MHz 电压 - 电源:1.4 V ~ 2.625 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:56-WFQFN 裸焊盘,CSP 供应商器件封装:56-LFCSP-WQ(8x8) 标准包装:1 |

| AD9554-1BCPZ-REEL7 | 功能描述:IC PLL CLOCK GEN 4OUT 72LFCSP 制造商:analog devices inc. 系列:- 包装:带卷(TR) 零件状态:有效 PLL:是 主要用途:以太网,SONET/SDH,Stratum 输入:CMOS,LVDS 输出:HCSL,LVDS,LVPECL 电路数:1 比率 - 输入:输出:4:4 差分 - 输入:输出:是/是 频率 - 最大值:942MHz 电压 - 电源:1.4 V ~ 2.625 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:56-WFQFN 裸焊盘,CSP 供应商器件封装:56-LFCSP-WQ(8x8) 标准包装:750 |

| AD9554BCPZ | 功能描述:IC CLOCK TRANSLATOR 8OUT 72LFCSP 制造商:analog devices inc. 系列:- 包装:托盘 零件状态:有效 PLL:是 主要用途:以太网,SONET/SDH,Stratum 输入:CMOS,LVDS 输出:HCSL,LVDS,LVPECL 电路数:1 比率 - 输入:输出:4:8 差分 - 输入:输出:是/是 频率 - 最大值:941MHz 电压 - 电源:1.47 V ~ 1.89 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:72-VFQFN 裸露焊盘,CSP 供应商器件封装:72-LFCSP-VQ(10x10) 标准包装:1 |

发布紧急采购,3分钟左右您将得到回复。