参数资料

| 型号: | AD9600ABCPZ-150 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 22/72页 |

| 文件大小: | 0K |

| 描述: | IC ADC 10BIT 150MSPS 64LFCSP |

| 标准包装: | 1 |

| 位数: | 10 |

| 采样率(每秒): | 150M |

| 数据接口: | 串行,SPI? |

| 转换器数目: | 2 |

| 功率耗散(最大): | 890mW |

| 电压电源: | 模拟和数字 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 64-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 64-LFCSP-VQ(9x9) |

| 包装: | 托盘 |

| 输入数目和类型: | 4 个单端,单极;2 个差分,单极 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页当前第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页

AD9600

Rev. B | Page 29 of 72

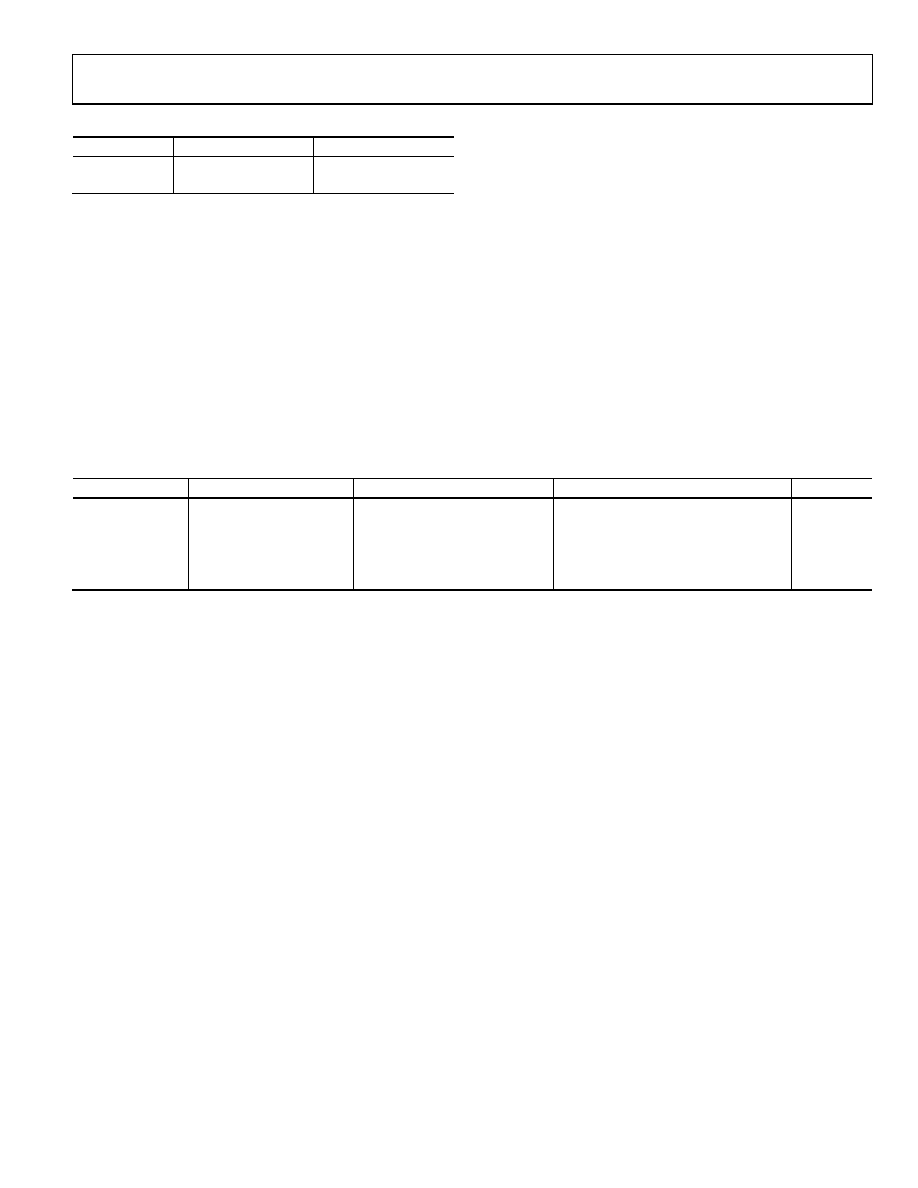

Table 12. SCLK/DFS Mode Selection (External Pin Mode)

Voltage at Pin

SCLK/DFS

SDIO/DCS

AGND

Offset binary (default)

DCS disabled

AVDD

Twos complement

DCS enabled (default)

Digital Output Enable Function (OEB)

The AD9600 has a flexible three-state ability for the digital

output pins. The three-state mode can be enabled by using the

SMI SDO/OEB pin or the SPI interface. If the SMI SDO/OEB pin

is low, the output data drivers are enabled. If the SMI SDO/OEB pin

is high, the output data drivers are placed into a high impedance

state. This output enable function is not intended for rapid access

to the data bus. Note that OEB is referenced to the digital output

driver supply (DRVDD) and should not exceed that supply voltage.

When the device uses the SPI interface, each channel’s data and

fast detect output pins can be independently three-stated by

using the output enable bar bit in Register 0x14.

TIMING

The AD9600 provides latched data with a pipeline delay of

12 clock cycles. Data outputs are available one propagation

delay (tPD) after the rising edge of the clock signal.

The length of the output data lines and the loads placed on them

should be minimized to reduce transients within the AD9600.

These transients can degrade the dynamic performance of the

converter. The lowest typical conversion rate of the AD9600 is

typically 10 MSPS. At clock rates below 10 MSPS, dynamic

performance may degrade.

Data Clock Output (DCO)

The AD9600 provides two data clock output (DCO) signals

intended for capturing the data in an external register. The data

outputs are valid on the rising edge of DCO, unless the polarity

has been changed via the SPI. See the timing diagrams shown

Table 13. Output Data Format

Input (V)

Condition (V)

Binary Output Mode

Twos Complement Mode

Overrange

(VIN+ ) (VIN )

< VREF 0.5 LSB

00 0000 0000

10 0000 0000

1

(VIN+ ) (VIN )

= –VREF

00 0000 0000

10 0000 0000

0

(VIN+ ) (VIN )

= 0

10 0000 0000

00 0000 0000

0

(VIN+ ) (VIN )

= +VREF 1.0 LSB

11 1111 1111

01 1111 1111

0

(VIN+ ) (VIN )

> +VREF 0.5 LSB

11 1111 1111

01 1111 1111

1

相关PDF资料 |

PDF描述 |

|---|---|

| AD9608BCPZRL7-125 | IC ADC 10BIT 125MSPS 64LFCSP |

| AD9609BCPZRL7-80 | IC ADC 10BIT SRL/SPI 80M 32LFCSP |

| AD9613BCPZ-170 | IC ADC 12BIT SRL 170MSPS 64LFCSP |

| AD9627ABCPZ-125 | IC ADC 12BIT 1255MSPS 64LFCSP |

| AD9627ABCPZ11-150 | IC ADC 11BIT 150MSPS 64LFCSP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9600BCPZ-105 | 制造商:Analog Devices 功能描述:ADC Dual Pipelined 105Msps 10-bit Parallel/LVDS 64-Pin LFCSP EP |

| AD9600BCPZ-125 | 制造商:Analog Devices 功能描述:ADC Dual Pipelined 125Msps 10-bit Parallel/LVDS 64-Pin LFCSP EP |

| AD9600BCPZ-150 | 制造商:Analog Devices 功能描述: |

| AD9601 | 制造商:AD 制造商全称:Analog Devices 功能描述:10-Bit, 200 MSPS/250 MSPS 1.8 V Analog-to-Digital Converter |

| AD9601-250EBZ | 功能描述:数据转换 IC 开发工具 10-Bit 250 Msps LowPwr CMOS ADC RoHS:否 制造商:Texas Instruments 产品:Demonstration Kits 类型:ADC 工具用于评估:ADS130E08 接口类型:SPI 工作电源电压:- 6 V to + 6 V |

发布紧急采购,3分钟左右您将得到回复。