参数资料

| 型号: | AD9600ABCPZ-150 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 24/72页 |

| 文件大小: | 0K |

| 描述: | IC ADC 10BIT 150MSPS 64LFCSP |

| 标准包装: | 1 |

| 位数: | 10 |

| 采样率(每秒): | 150M |

| 数据接口: | 串行,SPI? |

| 转换器数目: | 2 |

| 功率耗散(最大): | 890mW |

| 电压电源: | 模拟和数字 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 64-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 64-LFCSP-VQ(9x9) |

| 包装: | 托盘 |

| 输入数目和类型: | 4 个单端,单极;2 个差分,单极 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页当前第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页

AD9600

Rev. B | Page 30 of 72

ADC OVERRANGE AND GAIN CONTROL

In receiver applications, it is desirable to have a mechanism to

reliably determine when the converter is about to be clipped.

The standard overflow indicator provides after-the-fact infor-

mation on the state of the analog input that is of limited usefulness.

Therefore, it is helpful to have a programmable threshold below

full scale that allows time to reduce the gain before the clip

actually occurs. In addition, because input signals can have

significant slew rates, latency of this function is of major concern.

Highly pipelined converters can have significant latency. A good

compromise is to use the output bits from the first stage of the

ADC for this function. Latency for these output bits is very low,

and overall resolution is not highly significant. Peak input signals

are typically between full scale and 6 dB to 10 dB below full

scale. A 3-bit or 4-bit output provides adequate range and

resolution for this function.

Via the SPI port, the user can provide a threshold above which

an overrange output would be active. As long as the signal is below

that threshold, the output should remain low. The fast detect

output pins can also be programmed via the SPI port so that one of

the pins functions as a traditional overrange pin for customers

who currently use this feature. In this mode, all 12 bits of the

converter are examined in the traditional manner, and the output is

high for the condition normally defined as overflow. In either

mode, the magnitude of the data is considered in the calculation

of the condition (but the sign of the data is not considered). The

threshold detection responds identically to positive and negative

signals outside the desired magnitude range.

FAST DETECT OVERVIEW

The AD9600 contains circuitry to facilitate fast overrange detec-

tion, allowing very flexible external gain control implementations.

Each ADC has four fast detect output pins that are used to output

information about the current state of the ADC input level. The

function of these pins is programmable via the fast detect mode

select bits and the fast detect enable bit in Register 0x104, allowing

range information to be output from several points in the internal

datapath. These pins can also be set up to indicate the presence of

overrange or underrange conditions, according to programmable

threshold levels. Table 14 shows the six configurations available

for the fast detect pins.

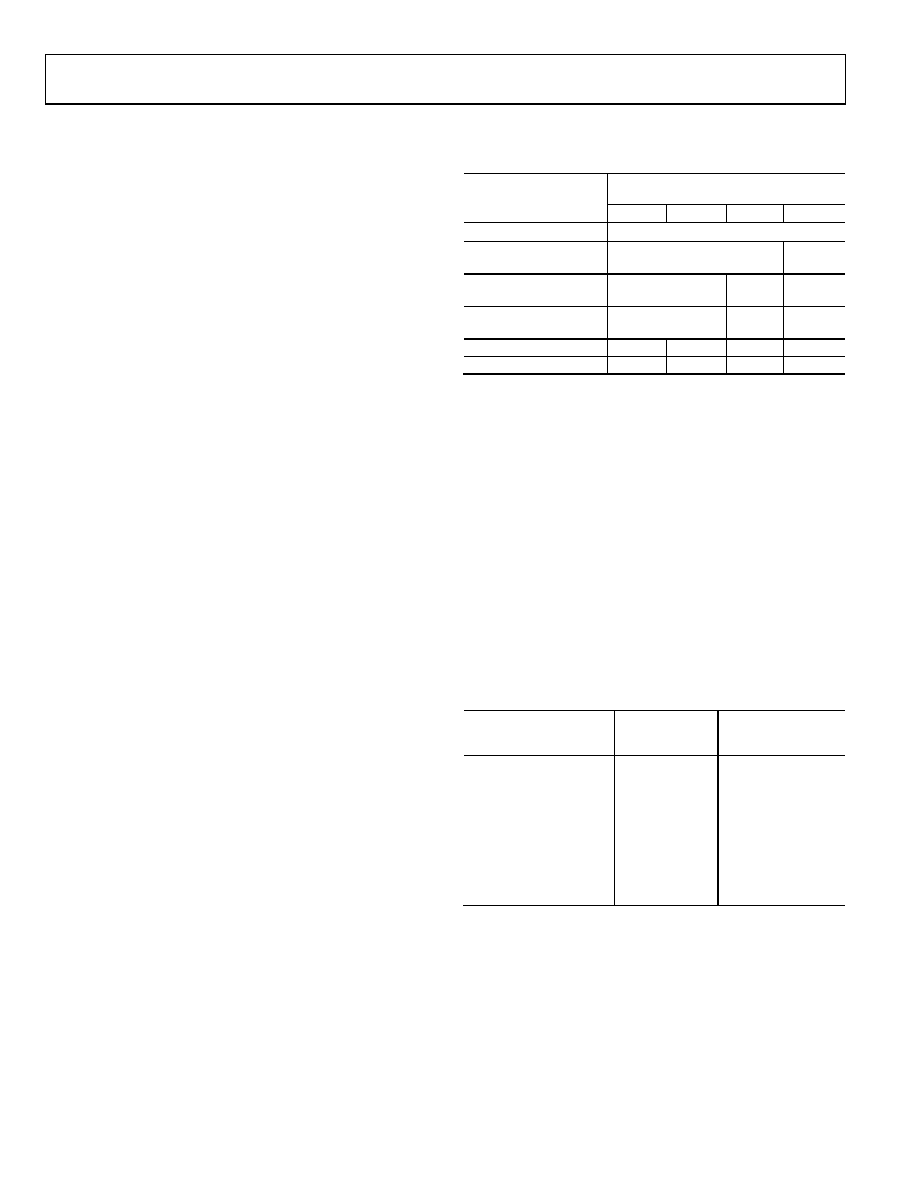

Table 14. Fast Detect Mode Select Bits Settings

Fast Detect

Mode Select Bits

(Register 0x104 [3:1])

Information Presented on

Fast Detect (FD) Pins of Each ADC1, 2

FD [3]

FD [2]

FD [1]

FD [0]

000

ADC fast magnitude (see

001

ADC fast magnitude

(see

OR

010

ADC fast magnitude

(see

OR

F_LT

011

ADC fast magnitude

(see

C_UT

F_LT

100

OR

C_UT

F_UT

F_LT

101

OR

F_UT

IG

DG

1 The fast detect pins are FD0A/FD0B to FD9A/FD9B for the CMOS mode

configuration and FD0+/FD0 to FD9+/FD9 for the LVDS mode

configuration.

2 See the ADC Overrange (OR) and Gain Switching sections for more

information about OR, C_UT, F_UT, F_LT, IG, and DG.

ADC FAST MAGNITUDE

When the fast detect output pins are configured to output the ADC

fast magnitude (that is, when the fast detect mode select bits are

set to 0b000), the information presented is the ADC level from an

early converter stage with only a two-clock-cycle latency (when

in CMOS output mode). Using the fast detect output pins in

this configuration provides the earliest possible level indication

information. Because this information is provided early in the

datapath, there is a significant uncertainty in the level indicated.

The nominal levels, along with the uncertainty indicated by the

ADC fast magnitude, are shown in Table 15.

Table 15. ADC Fast Magnitude Nominal Levels with

Fast Detect Mode Select Bits = 000

ADC Fast Magnitude on

FD [3:0] Pins

Nominal Input

Magnitude

Below FS (dB)

Nominal Input

Magnitude

Uncertainty (dB)

0000

<24

Minimum to 18.07

0001

24 to 14.5

30.14 to 12.04

0010

14.5 to 10

18.07 to 8.52

0011

10 to 7

12.04 to 6.02

0100

7 to 5

8.52 to 4.08

0101

5 to 3.25

6.02 to 2.5

0110

3.25 to 1.8

4.08 to 1.16

0111

1.8 to 0.56

2.5 to FS

1000

0.56 to 0

1.16 to 0

相关PDF资料 |

PDF描述 |

|---|---|

| AD9608BCPZRL7-125 | IC ADC 10BIT 125MSPS 64LFCSP |

| AD9609BCPZRL7-80 | IC ADC 10BIT SRL/SPI 80M 32LFCSP |

| AD9613BCPZ-170 | IC ADC 12BIT SRL 170MSPS 64LFCSP |

| AD9627ABCPZ-125 | IC ADC 12BIT 1255MSPS 64LFCSP |

| AD9627ABCPZ11-150 | IC ADC 11BIT 150MSPS 64LFCSP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9600BCPZ-105 | 制造商:Analog Devices 功能描述:ADC Dual Pipelined 105Msps 10-bit Parallel/LVDS 64-Pin LFCSP EP |

| AD9600BCPZ-125 | 制造商:Analog Devices 功能描述:ADC Dual Pipelined 125Msps 10-bit Parallel/LVDS 64-Pin LFCSP EP |

| AD9600BCPZ-150 | 制造商:Analog Devices 功能描述: |

| AD9601 | 制造商:AD 制造商全称:Analog Devices 功能描述:10-Bit, 200 MSPS/250 MSPS 1.8 V Analog-to-Digital Converter |

| AD9601-250EBZ | 功能描述:数据转换 IC 开发工具 10-Bit 250 Msps LowPwr CMOS ADC RoHS:否 制造商:Texas Instruments 产品:Demonstration Kits 类型:ADC 工具用于评估:ADS130E08 接口类型:SPI 工作电源电压:- 6 V to + 6 V |

发布紧急采购,3分钟左右您将得到回复。