参数资料

| 型号: | AD9600ABCPZ-150 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 4/72页 |

| 文件大小: | 0K |

| 描述: | IC ADC 10BIT 150MSPS 64LFCSP |

| 标准包装: | 1 |

| 位数: | 10 |

| 采样率(每秒): | 150M |

| 数据接口: | 串行,SPI? |

| 转换器数目: | 2 |

| 功率耗散(最大): | 890mW |

| 电压电源: | 模拟和数字 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 64-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 64-LFCSP-VQ(9x9) |

| 包装: | 托盘 |

| 输入数目和类型: | 4 个单端,单极;2 个差分,单极 |

第1页第2页第3页当前第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页

AD9600

Rev. B | Page 12 of 72

ABSOLUTE MAXIMUM RATINGS

Table 6.

Parameter

Rating

ELECTRICAL

AVDD, DVDD to AGND

0.3 V to +2.0 V

DRVDD to DRGND

0.3 V to +3.9 V

AGND to DRGND

0.3 V to +0.3 V

AVDD to DRVDD

3.9 V to +2.0 V

VIN + A/VIN + B, VIN A/VIN B to

AGND

0.3 V to AVDD + 0.2 V

CLK+, CLK to AGND

0.3 V to +3.9 V

SYNC to AGND

0.3 V to +3.9 V

VREF to AGND

0.3 V to AVDD + 0.2 V

SENSE to AGND

0.3 V to AVDD + 0.2 V

CML to AGND

0.3 V to AVDD + 0.2 V

RBIAS to AGND

0.3 V to AVDD + 0.2 V

CSB to AGND

0.3 V to +3.9 V

SCLK/DFS to DRGND

0.3 V to +3.9 V

SDIO/DCS to DRGND

0.3 V to DRVDD + 0.3 V

SMI SDO/OEB

0.3 V to DRVDD + 0.3 V

SMI SCLK/PDWN

0.3 V to DRVDD + 0.3 V

SMI SDFS

0.3 V to DRVDD + 0.3 V

Output Data Pins to DRGND1

0.3 V to DRVDD + 0.3 V

Fast Detect Output Pins to DRGND2

0.3 V to DRVDD + 0.3 V

Data Clock Output Pins to DRGND3

0.3 V to DRVDD + 0.3 V

ENVIRONMENTAL

Operating Temperature Range

(Ambient)

40°C to +85°C

Maximum Junction Temperature

Under Bias

150°C

Storage Temperature Range

(Ambient)

65°C to +150°C

1 The output data pins are D0A/D0B to D9A/D9B for the CMOS configuration

and D0+/D0 to D9+/D9 for the LVDS configuration.

2 The fast detect output pins are FD0A/FD0B to FD3A/FD3B for the CMOS

configuration and FD0+/FD0 to FD3+/FD3.

3 The data clock output pins are DCOA and DCOB for the CMOS configuration

and DCO+ and DCO for the LVDS configuration.

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

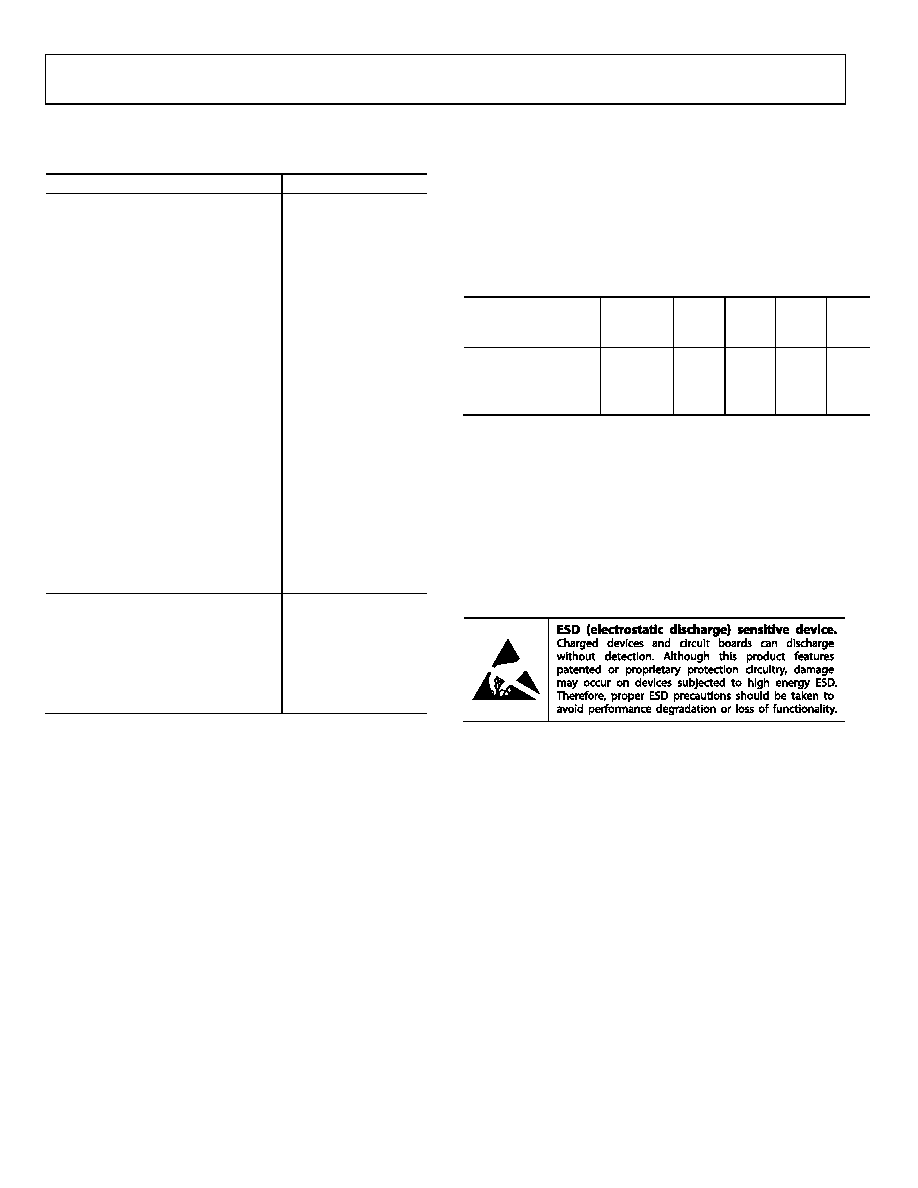

THERMAL CHARACTERISTICS

The exposed paddle must be soldered to the ground plane for

the LFCSP package. Soldering the exposed paddle to the

customer board increases the reliability of the solder joints,

maximizing the thermal capability of the package.

Table 7. Thermal Resistance

Package Type

Airflow

Velocity

(m/s)

θJB1,4

Unit

64-Lead, 9 mm × 9 mm

LFCSP (CP-64-3,

CP-64-6)

0

18.8

0.6

6.0

°C/W

1.0

16.5

°C/W

2.0

15.8

°C/W

1 Per JEDEC 51-7 standard and JEDEC 25-5 2S2P test board.

2 Per JEDEC JESD51-2 (still air) or JEDEC JESD51-6 (moving air).

3 Per MIL-Std 883, Method 1012.1.

4 Per JEDEC JESD51-8 (still air).

Typical θJA and θJC are specified for a 4-layer board in still air.

Airflow increases heat dissipation, effectively reducing θJA. In

addition, metal (such as metal traces through holes, ground,

and power planes) that is in direct contact with the package

leads reduces the θJA.

ESD CAUTION

相关PDF资料 |

PDF描述 |

|---|---|

| AD9608BCPZRL7-125 | IC ADC 10BIT 125MSPS 64LFCSP |

| AD9609BCPZRL7-80 | IC ADC 10BIT SRL/SPI 80M 32LFCSP |

| AD9613BCPZ-170 | IC ADC 12BIT SRL 170MSPS 64LFCSP |

| AD9627ABCPZ-125 | IC ADC 12BIT 1255MSPS 64LFCSP |

| AD9627ABCPZ11-150 | IC ADC 11BIT 150MSPS 64LFCSP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9600BCPZ-105 | 制造商:Analog Devices 功能描述:ADC Dual Pipelined 105Msps 10-bit Parallel/LVDS 64-Pin LFCSP EP |

| AD9600BCPZ-125 | 制造商:Analog Devices 功能描述:ADC Dual Pipelined 125Msps 10-bit Parallel/LVDS 64-Pin LFCSP EP |

| AD9600BCPZ-150 | 制造商:Analog Devices 功能描述: |

| AD9601 | 制造商:AD 制造商全称:Analog Devices 功能描述:10-Bit, 200 MSPS/250 MSPS 1.8 V Analog-to-Digital Converter |

| AD9601-250EBZ | 功能描述:数据转换 IC 开发工具 10-Bit 250 Msps LowPwr CMOS ADC RoHS:否 制造商:Texas Instruments 产品:Demonstration Kits 类型:ADC 工具用于评估:ADS130E08 接口类型:SPI 工作电源电压:- 6 V to + 6 V |

发布紧急采购,3分钟左右您将得到回复。