参数资料

| 型号: | AD9774ASZRL |

| 厂商: | Analog Devices Inc |

| 文件页数: | 21/24页 |

| 文件大小: | 0K |

| 描述: | IC DAC 14BIT 32MSPS 44MQFP |

| 产品变化通告: | Product Discontinuance 27/Oct/2011 |

| 标准包装: | 800 |

| 系列: | TxDAC+® |

| 设置时间: | 35ns |

| 位数: | 14 |

| 数据接口: | 并联 |

| 转换器数目: | 1 |

| 电压电源: | 模拟和数字 |

| 功率耗散(最大): | 1.13W |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 44-QFP |

| 供应商设备封装: | 44-MQFP(10x10) |

| 包装: | 带卷 (TR) |

| 输出数目和类型: | 2 电流,单极;2 电流,双极 |

| 采样率(每秒): | 32M |

AD9774

–6–

REV. B

PIN FUNCTION DESCRIPTIONS

Pin No.

Name

Description

1, 19, 40, 44

DCOM

Digital Common.

2

DB13

Most Significant Data Bit (MSB).

3–14

DB12–DB1

Data Bits 1–12.

15

DB0

Least Significant Data Bit (LSB).

16, 17, 42

NC

No Internal Connection.

18, 41

DVDD

Digital Supply Voltage (+2.7 V to +5.5 V).

20

CLK IN/OUT

Clock Input when PLL Clock Multiplier enabled. Clock Output when PLL Clock Multiplier

disabled. Data latched on rising edge.

21

PLLLOCK

Phase Lock Loop Lock Signal. Active High indicates PLL is locked to input clock.

22

CLK4

×IN

External 4

× Clock Input when PLL is disabled. No Connect when internal PLL is active.

23

PLLDIVIDE

PLL Range Control Pin. Connect to PLLCOM if CLKIN is above 10 MSPS. Connect to

PLLVDD if CLKIN is between 10 MSPS and 5.5 MSPS.

24

VCO IN/EXT

Internal Voltage Controlled Oscillator (VCO) Enable/Disable Pin. Connect to PLLVDD to enable

VCO. Connect to PLLCOM to disable VCO and drive CLK4

×IN with external VCO output.

25

LPF

PLL Loop Filter Node. Connect to external VCO control input if internal VCO disabled.

26

PLLVDD

Phase Lock Loop (PLL) Supply Voltage (+2.7 V to +5.5 V). Must be set to similar voltage as DVDD.

27

PLLCOM

Phase Lock Loop Common.

28

PLLENABLE

Phase Lock Loop Enable. Connect to PLLVDD to enable. Connect to PLLCOM to disable.

29

UNUSED

Factory Test. Leave Open.

30

REFLO

Reference Ground when Internal 1.2 V Reference Used. Connect to AVDD to disable internal

reference.

31

REFIO

Reference Input/Output. Serves as reference input when internal reference disabled (i.e., tie REFLO

to AVDD). Serves as 1.2 V reference output when internal reference activated (i.e., tie REFLO to

ACOM). Requires 0.1

F capacitor to ACOM when internal reference activated.

32

FSADJ

Full-Scale Current Output Adjust.

33

REFCOMP

Noise Reduction Node. Add 0.1

F to AVDD.

34

ACOM

Analog Common.

35

AVDD

Analog Supply Voltage (+2.7 V to +5.5 V).

36

IOUTB

Complementary DAC Current Output. Full-scale current when all data bits are 0s.

37

IOUTA

DAC Current Output. Full-scale current when all data bits are 1s.

38

ICOMP

Internal bias node for switch driver circuitry. Decouple to ACOM with 0.1

F capacitor.

39

SLEEP

Power-Down Control Input. Active High. Connect to DCOM if not used.

43

SNOOZE

SNOOZE Control Input. Deactivates 4

× interpolation filter to reduce digital power consumption

only. Active High. Connect to DCOM if not used.

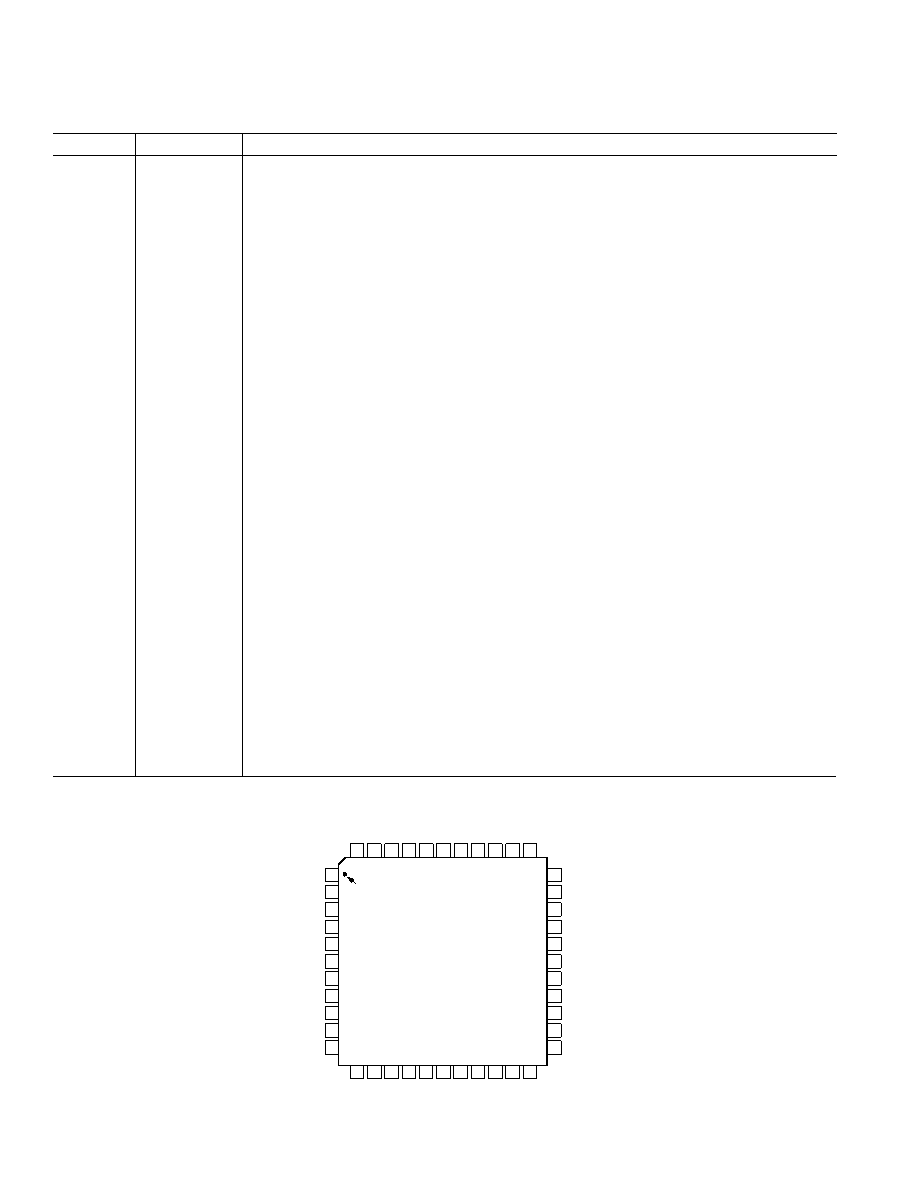

PIN CONFIGURATION

3

4

5

6

7

1

2

10

11

8

9

40 39 38

41

42

43

44

36 35 34

37

29

30

31

32

33

27

28

25

26

23

24

PIN 1

IDENTIFIER

TOP VIEW

(Not to Scale)

12 13 14 15 16 17 18 19 20 21 22

REFCOMP

FSADJ

REFIO

REFLO

UNUSED

PLLENABLE

PLLCOM

AD9774

DCOM

DB13

DB12

DB11

DB10

DB9

DB8

NC = NO CONNECT

DB7

DB6

DB5

DB4

PLLVDD

LPF

VCO IN/EXT

PLLDIVIDE

DB3

DB2

DB1

DB0

NC

DVDD

DCOM

CLK

IN/OUT

PLLLOCK

CLK4

IN

IOUTB

ACOM

DCOM

SNOOZE

DVDD

IOUTA

AVDD

DCOM

SLEEP

ICOMP

NC

相关PDF资料 |

PDF描述 |

|---|---|

| AD9779ABSVZRL | DAC 16BIT 1.0GSPS 100-TQFP |

| AD977ABNZ | IC ADC 16BIT 200KSPS 20DIP |

| AD9781BCPZ | IC DAC 14BT 500MSPS LVDS 72LFCSP |

| AD9877ABSZ | IC PROCESSOR FRONT END 100MQFP |

| AD9878BSTZ | IC FRONT-END MIXED-SGNL 100-LQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9774EB | 制造商:AD 制造商全称:Analog Devices 功能描述:14-Bit, 32 MSPS TxDAC⑩ with 4x Interpolation Filters |

| AD9774-EB | 制造商:Analog Devices 功能描述: |

| AD9774-EBZ | 制造商:Analog Devices 功能描述:14-BIT 32 MSPS TXDAC W/4X INTERPOLATION - Bulk |

| AD9775 | 制造商:AD 制造商全称:Analog Devices 功能描述:14-Bit, 160 MSPS 2X/4X/8X Interpolating Dual TxDAC+ D/A Converter |

| AD9775BSV | 制造商:Analog Devices 功能描述:DAC 2-CH R-2R 14-bit 80-Pin TQFP EP 制造商:Rochester Electronics LLC 功能描述:14BIT 160 MSPS DUAL TXDAC+ D/A CONVERTER - Bulk 制造商:Analog Devices 功能描述:IC 14-BIT DAC |

发布紧急采购,3分钟左右您将得到回复。