参数资料

| 型号: | AD9774ASZRL |

| 厂商: | Analog Devices Inc |

| 文件页数: | 7/24页 |

| 文件大小: | 0K |

| 描述: | IC DAC 14BIT 32MSPS 44MQFP |

| 产品变化通告: | Product Discontinuance 27/Oct/2011 |

| 标准包装: | 800 |

| 系列: | TxDAC+® |

| 设置时间: | 35ns |

| 位数: | 14 |

| 数据接口: | 并联 |

| 转换器数目: | 1 |

| 电压电源: | 模拟和数字 |

| 功率耗散(最大): | 1.13W |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 44-QFP |

| 供应商设备封装: | 44-MQFP(10x10) |

| 包装: | 带卷 (TR) |

| 输出数目和类型: | 2 电流,单极;2 电流,双极 |

| 采样率(每秒): | 32M |

AD9774

–15–

REV. B

DVDD

DIGITAL

INPUT

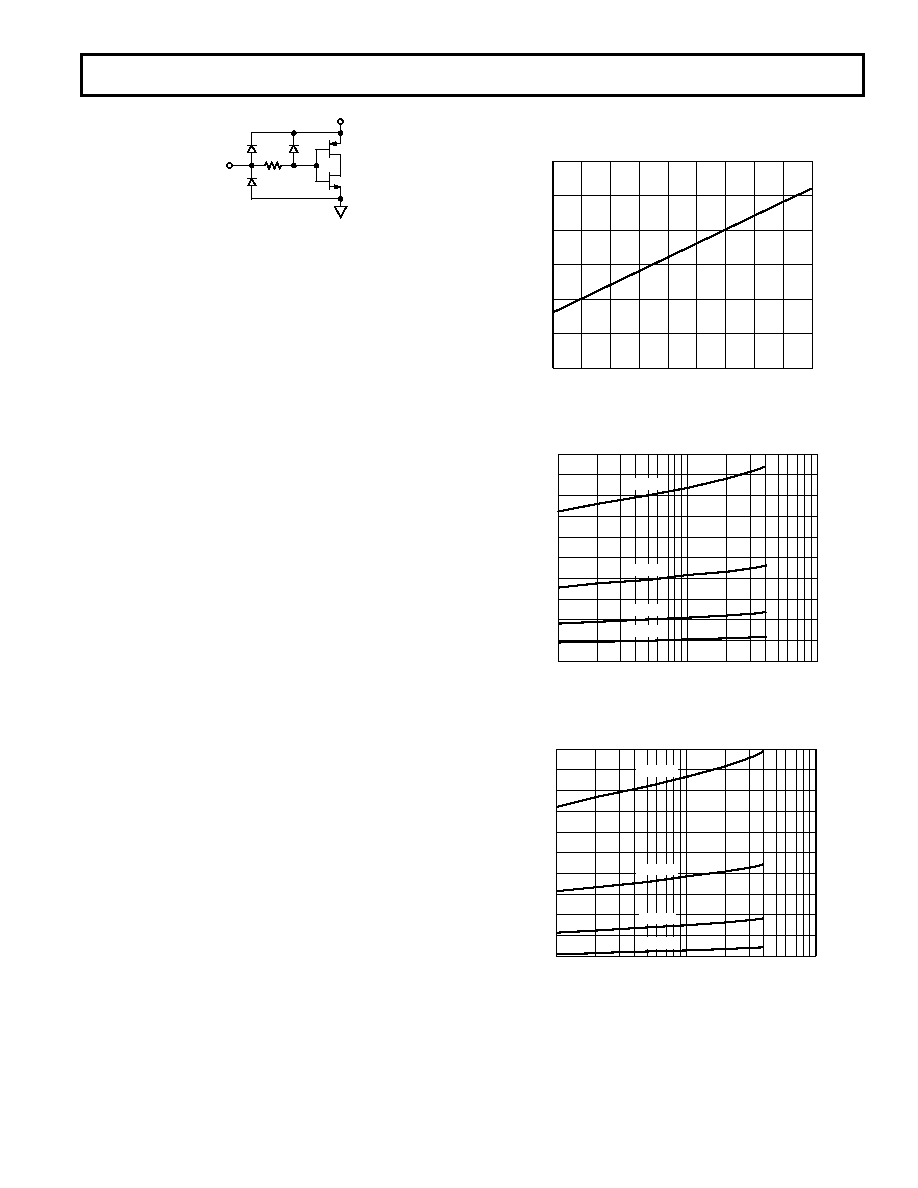

Figure 32. Equivalent Digital Input

Since the AD9774 is capable of being updated up to 32 MSPS,

the quality of the clock and data input signals are important in

achieving the optimum performance. Operating the AD9774

with reduced logic swings and a corresponding digital supply

(DVDD) will result in the lowest data feedthrough and on-chip

digital noise. The drivers of the digital data interface circuitry

should be specified to meet the minimum setup and hold times

of the AD9774 as well as its required min/max input logic level

thresholds.

Digital signal paths should be kept short and run lengths matched

to avoid propagation delay mismatch. The insertion of a low

value resistor network (i.e., 20

to 100 ) between the AD9774

digital inputs and driver outputs may be helpful in reducing any

overshooting and ringing at the digital inputs that contribute to

data feedthrough.

The external clock driver circuitry should provide the AD9774

with a low jitter clock input meeting the min/max logic levels

while providing fast edges. Fast clock edges will help minimize

any jitter that will manifest itself as phase noise on a recon-

structed waveform. Thus, the clock input should be driven by

the fastest logic family suitable for the application.

SLEEP AND SNOOZE MODE OPERATION

The AD9774 has a SLEEP function that turns off the output

current and reduces the supply current to less than 5 mA over

the specified supply range of 2.7 V to 5.5 V and temperature

range. This mode can be activated by applying a logic level “1”

to the SLEEP pin. The AD9774 takes less than 0.1

s to power

down and approximately 6.4

s to power back up.

The SNOOZE mode should be considered as an alternative

power-savings option if the power-up characteristics of the

SLEEP mode are unsuitable. This mode, which is also activated

by applying a logic level “1” to the SNOOZE pin, disables the

AD9774’s digital filters only, resulting in significant power

savings. Both the SLEEP and SNOOZE pins should be tied to

DCOM if power savings is not required.

POWER DISSIPATION

The power dissipation, PD, of the AD9774 is dependent on

several factors, including: (1) AVDD, PLLVDD, and DVDD,

the power supply voltages; (2) IOUTFS, the full-scale current

output; (3) fCLOCK, the update rate; and (4) the reconstructed

digital input waveform. The power dissipation is directly pro-

portional to the analog supply current, IAVDD, and the digital

supply current, IDVDD. IAVDD is directly proportional to IOUTFS,

as shown in Figure 33, and is insensitive to fCLOCK.

Conversely, IDVDD is dependent on both the digital input wave-

form, fCLOCK, and digital supply DVDD. Figures 34 and 35

show IDVDD as a function of full-scale sine wave output ratios

(fOUT/fCLOCK) for various update rates with DVDD = 5 V and

DVDD = 3 V, respectively. Note, how IDVDD is reduced by more

than a factor of 2 when DVDD is reduced from 5 V to 3 V.

IOUTFS – mA

30

0

220

4

6

8

1012

141618

25

20

15

10

5

I AVDD

–

mA

Figure 33. IAVDD vs. IOUTFS

RATIO –

fOUT/fCLOCK

200

180

20

0.01

1.0

0.10

I DVDD

–

mA

100

80

60

40

140

120

160

0

32MSPS

16MSPS

8MSPS

4MSPS

Figure 34. IDVDD vs. Ratio @ DVDD = 5 V

RATIO –

fOUT/fCLOCK

100

0

0.01

1.0

0.10

I DVDD

–

mA

90

50

80

70

60

40

30

20

10

32MSPS

16MSPS

8MSPS

4MSPS

Figure 35. IDVDD vs. Ratio @ DVDD = 3 V

For those applications requiring the AD9774 to operate under the

following conditions: (1) AVDD, PLLVDD and DVDD = +5 V;

(2) fCLOCK > 25 MSPS; and (3) ambient temperatures > 70°C;

proper thermal management via a heatsink or thermal epoxy is

recommended.

相关PDF资料 |

PDF描述 |

|---|---|

| AD9779ABSVZRL | DAC 16BIT 1.0GSPS 100-TQFP |

| AD977ABNZ | IC ADC 16BIT 200KSPS 20DIP |

| AD9781BCPZ | IC DAC 14BT 500MSPS LVDS 72LFCSP |

| AD9877ABSZ | IC PROCESSOR FRONT END 100MQFP |

| AD9878BSTZ | IC FRONT-END MIXED-SGNL 100-LQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9774EB | 制造商:AD 制造商全称:Analog Devices 功能描述:14-Bit, 32 MSPS TxDAC⑩ with 4x Interpolation Filters |

| AD9774-EB | 制造商:Analog Devices 功能描述: |

| AD9774-EBZ | 制造商:Analog Devices 功能描述:14-BIT 32 MSPS TXDAC W/4X INTERPOLATION - Bulk |

| AD9775 | 制造商:AD 制造商全称:Analog Devices 功能描述:14-Bit, 160 MSPS 2X/4X/8X Interpolating Dual TxDAC+ D/A Converter |

| AD9775BSV | 制造商:Analog Devices 功能描述:DAC 2-CH R-2R 14-bit 80-Pin TQFP EP 制造商:Rochester Electronics LLC 功能描述:14BIT 160 MSPS DUAL TXDAC+ D/A CONVERTER - Bulk 制造商:Analog Devices 功能描述:IC 14-BIT DAC |

发布紧急采购,3分钟左右您将得到回复。