- 您现在的位置:买卖IC网 > PDF目录16826 > AD9858/PCBZ (Analog Devices Inc)BOARD EVAL FOR AD9858 PDF资料下载

参数资料

| 型号: | AD9858/PCBZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 28/32页 |

| 文件大小: | 0K |

| 描述: | BOARD EVAL FOR AD9858 |

| 产品培训模块: | Direct Digital Synthesis Tutorial Series (1 of 7): Introduction Direct Digital Synthesizer Tutorial Series (7 of 7): DDS in Action Direct Digital Synthesis Tutorial Series (3 of 7): Angle to Amplitude Converter Direct Digital Synthesis Tutorial Series (6 of 7): SINC Envelope Correction Direct Digital Synthesis Tutorial Series (4 of 7): Digital-to-Analog Converter Direct Digital Synthesis Tutorial Series (2 of 7): The Accumulator |

| 设计资源: | Low Jitter Sampling Clock Generator for High Performance ADCs Using AD9958/9858 and AD9515 (CN0109) |

| 标准包装: | 1 |

| 主要目的: | 计时,直接数字合成(DDS) |

| 已用 IC / 零件: | AD9858/TL |

| 已供物品: | 板 |

| 其它名称: | AD9858/PCB AD9858/PCB-ND |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页当前第28页第29页第30页第31页第32页

AD9858

Rev. C | Page 5 of 32

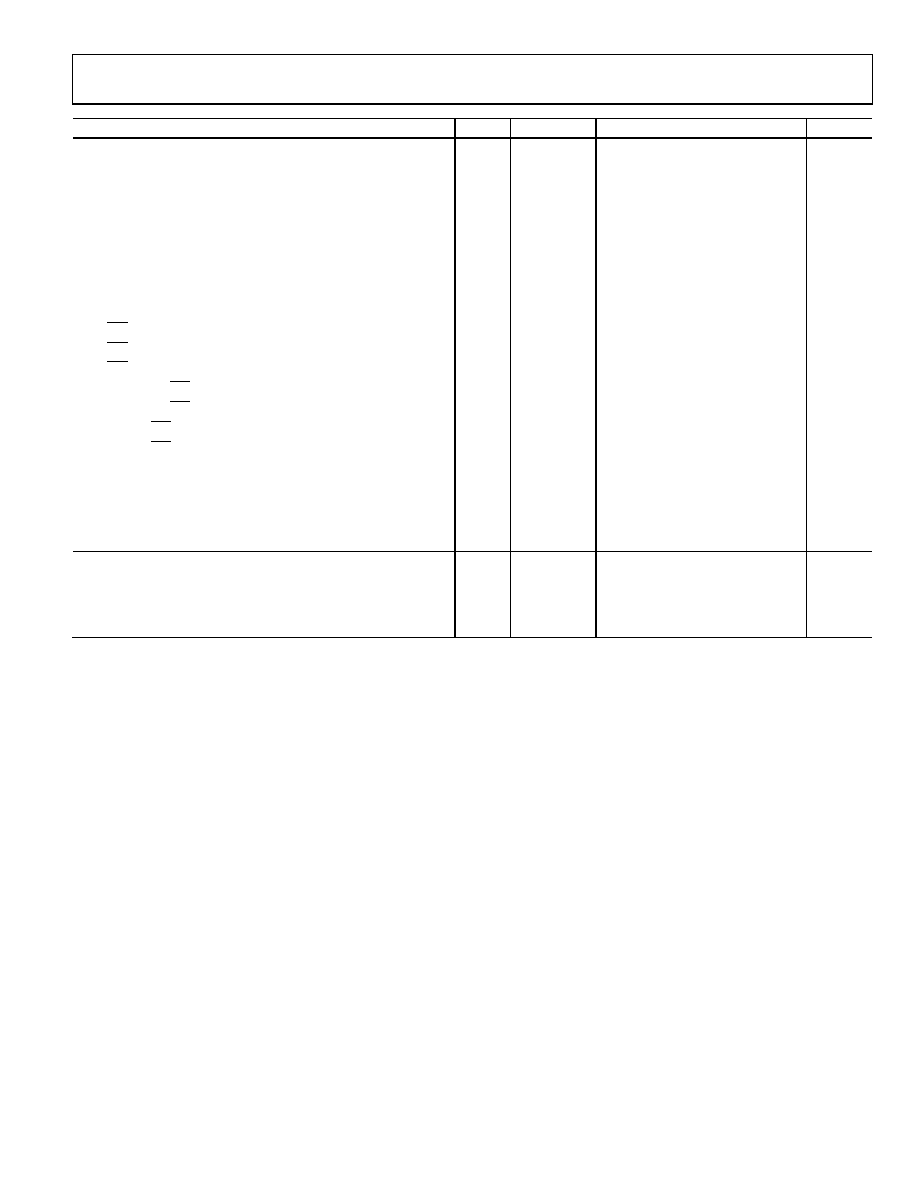

Parameter

Temp

Test Level

Min

Typ

Max

Unit

TIMING CHARACTERISTICS

Serial Control Bus

Maximum Frequency

Full

IV

10

MHz

Minimum Clock Pulse Width Low (tPWL)

Full

IV

5.5

ns

Minimum Clock Pulse Width High (tPWH)

Full

IV

15

ns

Maximum Clock Rise/Fall Time

Full

IV

1

ns

Minimum Data Setup Time (tDS)

Full

IV

7

ns

Minimum Data Hold Time (tDH)

Full

IV

0

ns

Maximum Data Valid Time (tDV)

Full

IV

20

ns

Parallel Control Bus10

WR Minimum Low Time (tWRLOW)

Full

IV

3

ns

WR Minimum High Time (tWRHIGH)

Full

IV

6

ns

WR Minimum Period (tWR)

Full

IV

9

ns

Address to WR Setup (tASU)

Full

IV

3

ns

Address to WR Hold (tAHU)

Full

IV

0

ns

Data to WR Setup (tDSU)

Full

IV

3.5

ns

Data to WR Hold (tDHU)

Full

IV

0

ns

Miscellaneous Timing Specifications

REFCLK to SYNCLK

Full

V

2.5

ns

FUD/PS[1:0] to SYNCLK Setup Time11

Full

IV

4

ns

FUD/PS[1:0] to SYNCLK Hold Time11

Full

IV

0

ns

REFCLK to SYNCLK Delay

Full

IV

2.5

3

ns

DATA LATENCY (PIPELINE DELAY)

FTW/POW to DAC Output

25°C

IV

83

SYSCLK

cycles12

DFTW to DAC Output

25°C

IV

99

SYSCLK

cycles12

1 REFCLK input is internally dc biased. AC coupling should be used.

2 Reference clock frequency is selected to ensure that the second harmonic is out of the bandwidth of interest.

3 PD inputs set at 400 MHz with divide-by-4 enabled.

4 The charge pump current is programmable in eight discrete steps; minimum value assumes current sharing.

5 For 0.75 V < VCP < CPVDD 0.75 V.

6 These differential inputs are internally dc biased. AC coupling should be used.

7 The charge pump supply voltage can range from 4.75 V to 5.25 V.

8 DAC output is differential open collector.

9 For 1 dB output compression; input power measured at 50 Ω.

10 See Figure 35 and Figure 36 for timing diagrams.

11 See Figure 34 for timing diagram.

12 SYSCLK = REFCLK/x, where x is 1 or 2, as set using CFR[6].

相关PDF资料 |

PDF描述 |

|---|---|

| AD9956-VCO/PCBZ | BOARD EVAL 14BIT 1.8V 48LFCSP |

| GEM22DRKF | CONN EDGECARD 44POS DIP .156 SLD |

| 362A024-4/86-0 | BOOT MOLDED |

| AD9956/PCBZ | BOARD EVAL FOR AD9956 |

| 0210391089 | CABLE JUMPER 1MM .203M 37POS |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9858TLPCB | 制造商:AD 制造商全称:Analog Devices 功能描述:1 GSPS Direct Digital Synthesizer |

| AD9858XSV | 制造商:Analog Devices 功能描述: |

| AD9859 | 制造商:AD 制造商全称:Analog Devices 功能描述:400 MSPS, 10-Bit, 1.8 V CMOS Direct Digital Synthesizer |

| AD9859/PCB | 制造商:Analog Devices 功能描述:NCO, 400MSPS 10 BIT, 1.8V CMOS DIRECT DGTL SYNTHESIZER - Bulk |

| AD9859/PCBZ | 功能描述:BOARD EVAL FOR AD9859 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:AgileRF™ 标准包装:1 系列:- 主要目的:电信,线路接口单元(LIU) 嵌入式:- 已用 IC / 零件:IDT82V2081 主要属性:T1/J1/E1 LIU 次要属性:- 已供物品:板,电源,线缆,CD 其它名称:82EBV2081 |

发布紧急采购,3分钟左右您将得到回复。