- 您现在的位置:买卖IC网 > PDF目录1894 > AD9888KSZ-170 (Analog Devices Inc)IC ANALOG INTRFC 170MSPS 128MQFP PDF资料下载

参数资料

| 型号: | AD9888KSZ-170 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 14/36页 |

| 文件大小: | 0K |

| 描述: | IC ANALOG INTRFC 170MSPS 128MQFP |

| 标准包装: | 1 |

| 应用: | 图形卡,VGA 接口 |

| 接口: | 2 线串口 |

| 电源电压: | 3 V ~ 3.6 V |

| 封装/外壳: | 128-BFQFP |

| 供应商设备封装: | 128-MQFP(14x20) |

| 包装: | 托盘 |

| 安装类型: | 表面贴装 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页当前第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页

Data Sheet

AD9888

Rev. C | Page 21 of 36

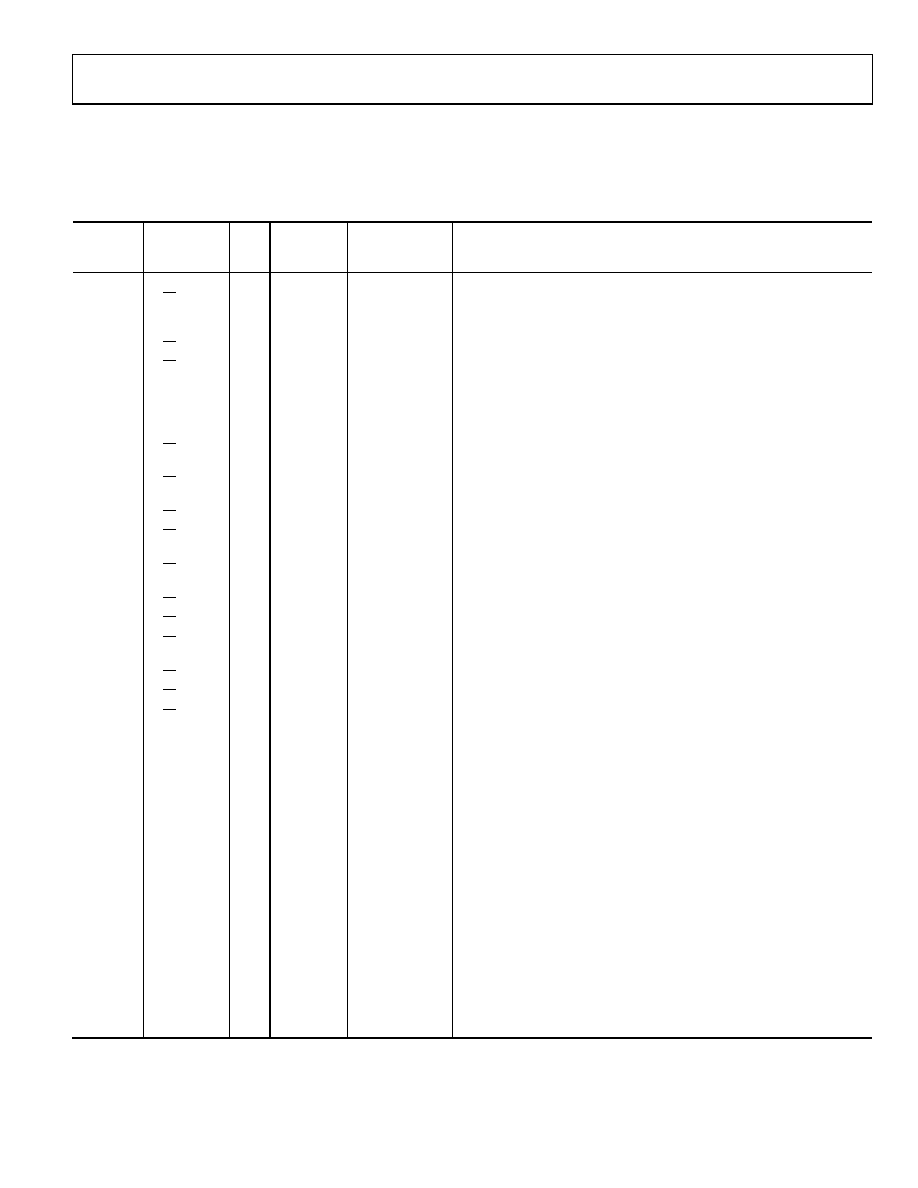

2-WIRE SERIAL REGISTER MAP

The AD9888 is initialized and controlled by a set of registers that determine the operating modes. An external controller is employed to

write and read the control registers through the two-line serial interface port.

Table 8. Control Register Map

Hex

Address

Read and

Write, or

Read Only

Bits

Default

Value

Register Name

Function

0x00

RO

[7:0]

Chip revision

An 8-bit register that represents the silicon revision level.

0x01

R/W

[7:0]

01101001

PLL divider MSB

MSBs (Bits[11:4]) of the PLL divider word. Larger values mean the PLL

operates at a faster rate. This register should be loaded first whenever a

change is needed to allow the PLL more time to lock.1

0x02

R/W

[7:4]

1101****

PLL divider LSB

LSBs of the PLL divider word.1

0x03

R/W

[7:3]

01******

VCO range

select/charge

pump current

Bits[7:6]—VCO range. Selects VCO frequency range. See the Clock

Generation section.

**001***

Bits[5:3]—charge pump current. Varies the current that drives the low-

pass filter. See the Clock Generation section.

0x04

R/W

[7:3]

10000***

Clock Phase

adjust

ADC Clock phase adjustment. Larger values mean more delay.

(1 LSB = t/32)

0x05

R/W

[7:0]

00001000

Clamp

placement

Places the CLAMP signal an integer number of clock periods after the

trailing edge of the HSYNC signal.

0x06

R/W

[7:0]

00010100

Clamp duration

Number of clock periods that the CLAMP signal is actively clamping.

0x07

R/W

[7:0]

00100000

HSYNC output

pulse width

Sets the number of pixel clocks that HSOUT remains active.

0x08

R/W

[7:0]

10000000

Red gain

Controls the ADC input range (contrast) of the red channel. Bigger

values result in less contrast.

0x09

R/W

[7:0]

10000000

Green gain

Same function as the red gain bits, but for the green channel.

0x0A

R/W

[7:0]

10000000

Blue gain

Same function as the red gain bits, but for the blue channel.

0x0B

R/W

[7:1]

1000000*

Red offset

Controls dc offset (brightness) of the red channel. Bigger values

decrease brightness.

0x0C

R/W

[7:1]

1000000*

Green offset

Same function as the red offset bits, but for the green channel.

0x0D

R/W

[7:1]

1000000*

Blue offset

Same function as the red offset bits, but for the blue channel.

0x0E

R/W

[7:0]

0*******

Sync control

Bit 7—HSYNC input polarity override. Logic 0 = polarity determined by

chip; Logic 1 = polarity set by Bit 6 in Register 0x0E.

*1******

Bit 6—HSYNC input polarity. Indicates to the PLL the polarity of the

incoming HSYNC signal. Logic 0 = active low; Logic 1 = active high.

**0*****

Bit 5—HSYNC output polarity. Logic 0 = logic high sync; Logic 1 = logic

low sync.

***0****

Bit 4—active HSYNC override. Logic 1 = the user can select the HSYNC

to be used via Bit 3; Logic 0 = the active interface is selected via Bit 6 in

Register 0x14.

****0***

Bit 3—active HSYNC select. Logic 0 = selects HSYNC as the active sync;

Logic 1 = selects sync-on-green as the active sync. Note that the

indicated HSYNC is used only if Bit 4 is set to Logic 1 or if both syncs are

active (Bit 1 and Bit 7 are set to Logic 1 in Register 0x14).

*****0**

Bit 2—VSYNC output invert. Logic 0 = invert; Logic 1 = no invert.

******0*

Bit 1—active VSYNC override. Logic 1 = the user can select the VSYNC to

be used via Bit 0; Logic 0 = the active interface is selected via Bit 3 in

Register 0x14.

*******0

Bit 0—active VSYNC select. Logic 0 = selects raw VSYNC as the output

VSYNC; Logic 1 = selects sync separated VSYNC as the output VSYNC.

Note that the indicated VSYNC is used only if Bit 1 is set to Logic 1.

相关PDF资料 |

PDF描述 |

|---|---|

| AD9895KBCZRL | IC CCD SIGNAL PROC/GEN 64-CSPBGA |

| AD9910BSVZ-REEL | IC DDS 1GSPS 14BIT PAR 100TQFP |

| AD9911BCPZ-REEL7 | IC DDS 500MSPS DAC 10BIT 56LFCSP |

| AD9912ABCPZ | IC DDS 1GSPS DAC 14BIT 64LFCSP |

| AD9913BCPZ-REEL7 | IC DDS 250MSPS 10BIT ADC 32LFCSP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9888KSZ-170 | 制造商:Analog Devices 功能描述:TV / Video IC |

| AD9888KSZ-205 | 制造商:Analog Devices 功能描述:205MHZ ANALOG GRAPHICS INTERFACE 制造商:Analog Devices 功能描述:IC ANALOG INTERFACE |

| AD9888KSZ-205KL1 | 制造商:Analog Devices 功能描述:- Rail/Tube |

| AD9889 | 制造商:Analog Devices 功能描述:- Bulk |

| AD9889A | 制造商:AD 制造商全称:Analog Devices 功能描述:High Performance HDMI/DVI Transmitter |

发布紧急采购,3分钟左右您将得到回复。