- 您现在的位置:买卖IC网 > PDF目录10979 > AD9959BCPZ (Analog Devices Inc)IC DDS QUAD 10BIT DAC 56LFCSP PDF资料下载

参数资料

| 型号: | AD9959BCPZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 2/44页 |

| 文件大小: | 0K |

| 描述: | IC DDS QUAD 10BIT DAC 56LFCSP |

| 产品培训模块: | Direct Digital Synthesis Tutorial Series (1 of 7): Introduction Direct Digital Synthesizer Tutorial Series (7 of 7): DDS in Action Direct Digital Synthesis Tutorial Series (3 of 7): Angle to Amplitude Converter Direct Digital Synthesis Tutorial Series (6 of 7): SINC Envelope Correction Direct Digital Synthesis Tutorial Series (4 of 7): Digital-to-Analog Converter Direct Digital Synthesis Tutorial Series (2 of 7): The Accumulator |

| 设计资源: | Phase Coherent FSK Modulator (CN0186) |

| 标准包装: | 1 |

| 分辨率(位): | 10 b |

| 主 fclk: | 500MHz |

| 调节字宽(位): | 32 b |

| 电源电压: | 1.71 V ~ 1.96 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 56-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 56-LFCSP-VQ(8x8) |

| 包装: | 托盘 |

| 产品目录页面: | 552 (CN2011-ZH PDF) |

第1页当前第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页

AD9959

Rev. B | Page 10 of 44

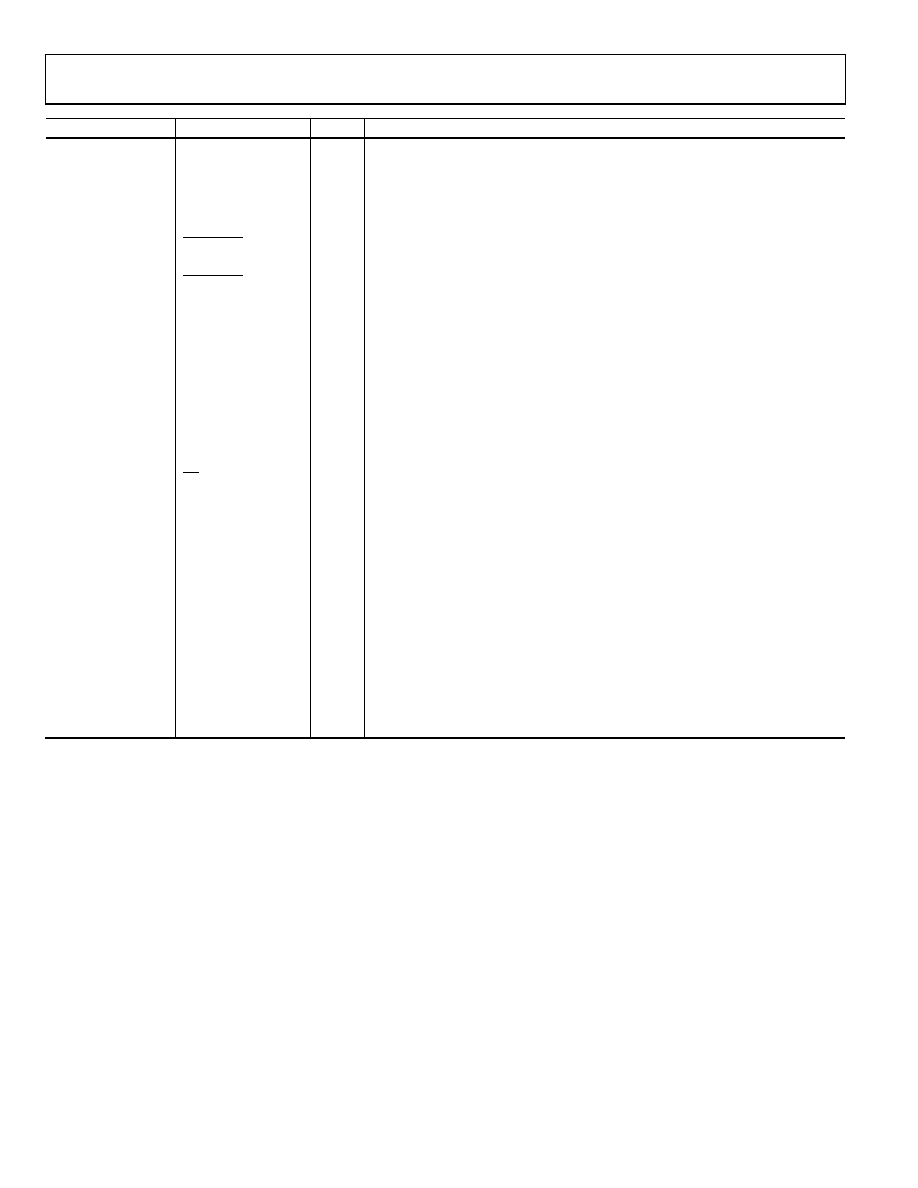

Pin No.

Mnemonic

Description

24

CLK_MODE_SEL

I

Control Pin for the Oscillator Section. Caution: Do not drive this pin beyond 1.8 V.

When high (1.8 V), the oscillator section is enabled to accept a crystal as the

REF_CLK source. When low, the oscillator section is bypassed.

27

LOOP_FILTER

I

Connects to the external zero compensation network of the PLL loop filter.

Typically, the network consists of a 0 Ω resistor in series with a 680 pF capacitor

tied to AVDD.

29

CH0_IOUT

O

Complementary DAC Output. Terminates into AVDD.

30

CH0_IOUT

O

True DAC Output. Terminates into AVDD.

35

CH1_IOUT

O

Complementary DAC Output. Terminates into AVDD.

36

CH1_IOUT

O

True DAC Output. Terminates into AVDD.

40 to 43

P0 to P3

I

Data pins used for modulation (FSK, PSK, ASK), to start/stop the sweep accumulators

or used to ramp up/ramp down the output amplitude. The data is synchronous to

the SYNC_CLK (Pin 54). The data inputs must meet the setup and hold time

requirements of the SYNC_CLK. The functionality of these pins is controlled by the

profile pin configuration (PPC) bits (FR1[14:12]).

46

I/O_UPDATE

I

A rising edge transfers data from the serial I/O port buffer to active registers.

I/O_UPDATE is synchronous to the SYNC_CLK (Pin 54). I/O_UPDATE must meet the

setup and hold time requirements of the SYNC_CLK to guarantee a fixed pipeline

delay of data to the DAC output; otherwise, a ±1 SYNC_CLK period of pipeline

uncertainty exists. The minimum pulse width is one SYNC_CLK period.

47

CS

I

Active Low Chip Select. Allows multiple devices to share a common I/O bus (SPI).

48

SCLK

I

Serial Data Clock for I/O Operations. Data bits are written on the rising edge of

SCLK and read on the falling edge of SCLK.

49

DVDD_I/O

I

3.3 V Digital Power Supply for SPI Port and Digital I/O.

50

SDIO_0

I/O

Data Pin SDIO_0 is dedicated to the serial port I/O only.

51, 52

SDIO_1, SDIO_2

I/O

Data Pin SDIO_1 and Data Pin SDIO_2 can be used for the serial I/O port or used to

initiate a ramp-up/ramp-down (RU/RD) of the DAC output amplitude.

53

SDIO_3

I/O

Data Pin SDIO_3 can be used for the serial I/O port or to initiate a ramp-up/ramp-down

(RU/RD) of the DAC output amplitude. In single-bit or 2-bit modes, SDIO_3 is used

for SYNC_I/O. If the SYNC_I/O function is not used, tie to ground or Logic 0. Do not

let SDIO_3 float in single-bit or 2-bit modes.

54

SYNC_CLK

O

The SYNC_CLK runs at one-fourth the system clock rate; it can be disabled. I/O_UPDATE

or data (Pin 40 to Pin 43) is synchronous to the SYNC_CLK. To guarantee a fixed pipeline

delay of data to DAC output, I/O_UPDATE or data (Pin 40 to Pin 43) must meet the

setup and hold time requirements to the rising edge of SYNC_CLK; otherwise, a ±1

SYNC_CLK period of uncertainty occurs.

1 I = input, O = output.

相关PDF资料 |

PDF描述 |

|---|---|

| VE-2WT-IY-F2 | CONVERTER MOD DC/DC 6.5V 50W |

| VE-2WR-IY-F4 | CONVERTER MOD DC/DC 7.5V 50W |

| VE-2WR-IY-F1 | CONVERTER MOD DC/DC 7.5V 50W |

| VE-2WP-IY-F3 | CONVERTER MOD DC/DC 13.8V 50W |

| VE-2WN-IY-F2 | CONVERTER MOD DC/DC 18.5V 50W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9959BCPZ1 | 制造商:AD 制造商全称:Analog Devices 功能描述:4-Channel, 500 MSPS DDS with 10-Bit DACs |

| AD9959BCPZ-REEL7 | 功能描述:IC DDS QUAD 10BIT DAC 56LFCSP RoHS:是 类别:集成电路 (IC) >> 接口 - 直接数字合成 (DDS) 系列:- 产品变化通告:Product Discontinuance 27/Oct/2011 标准包装:2,500 系列:- 分辨率(位):10 b 主 fclk:25MHz 调节字宽(位):32 b 电源电压:2.97 V ~ 5.5 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:带卷 (TR) |

| AD9959BCPZ-REEL71 | 制造商:AD 制造商全称:Analog Devices 功能描述:4-Channel, 500 MSPS DDS with 10-Bit DACs |

| AD995PCBZ | 制造商:AD 制造商全称:Analog Devices 功能描述:1 GSPS Quadrature Digital Upconverter w/18-Bit IQ Data Path and 14-Bit DAC |

| AD9960BSTZ | 功能描述:RFID应答器 MxFE for RFID Reader Transceiver RoHS:否 制造商:Murata 存储容量:512 bit 工作温度范围:- 40 C to + 85 C 安装风格:SMD/SMT 封装 / 箱体: 封装:Reel |

发布紧急采购,3分钟左右您将得到回复。