- 您现在的位置:买卖IC网 > PDF目录1895 > AD9992BBCZRL (Analog Devices Inc)IC CCD SGNL PROC 12BIT 105CSPBGA PDF资料下载

参数资料

| 型号: | AD9992BBCZRL |

| 厂商: | Analog Devices Inc |

| 文件页数: | 56/92页 |

| 文件大小: | 0K |

| 描述: | IC CCD SGNL PROC 12BIT 105CSPBGA |

| 产品变化通告: | AD9992 Discontinuation 22/Feb/2012 |

| 标准包装: | 2,000 |

| 类型: | CCD 信号处理器,12 位 |

| 输入类型: | 逻辑 |

| 输出类型: | 逻辑 |

| 接口: | 3 线串口 |

| 电流 - 电源: | 27mA |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 105-LFBGA,CSPBGA |

| 供应商设备封装: | 105-CSPBGA(8x8) |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页当前第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页

AD9992

Rev. C | Page 6 of 92

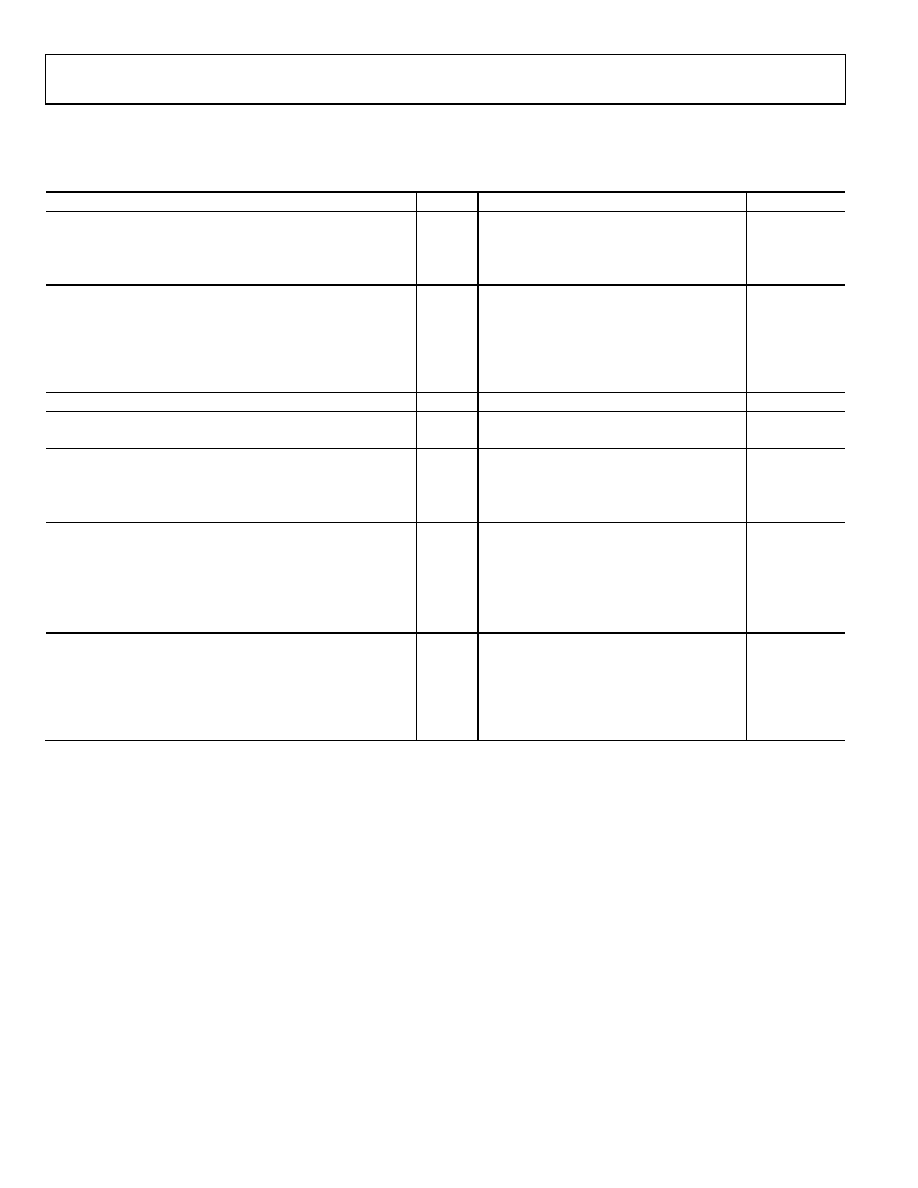

TIMING SPECIFICATIONS

CL = 20 pF, AVDD = DVDD = TCVDD = 1.8 V, DRVDD = 3.0 V, fCLI = 40 MHz, unless otherwise noted.

Table 4.

Parameter

Symbol

Min

Typ

Max

Unit

MASTER CLOCK (See Figure 15)

CLI Clock Period

tCONV

25

ns

CLI High/Low Pulse Width

10

12.5

15

ns

Delay from CLI Rising Edge to Internal Pixel Position 0

tCLIDLY

6

ns

SLAVE MODE SPECIFICATIONS (See Figure 76)

VD Falling Edge to HD Falling Edge in Slave Mode

tVDHD

0

VD period 5 ×

tCONV

ns

HD Edge to CLI Rising Edge (Only Valid if OSC_RSTB = LO)

tHDCLI

3

tCONV 2

ns

HD Edge to CLO Rising Edge (Only Valid if OSC_RSTB = HI)

tHDCLO

3

tCONV 2

ns

Inhibit Region for SHP Edge Location

tSHPINH

48

63

Edge location

2

20

Pixels

SHP Sample Edge to SHD Sample Edge

tS1

11

12.5

ns

Output Delay from DCLK Rising Edge

tOD

1

ns

Inhibited Area for DOUTPHASE Edge Location

tDOUTINH

SHDLOC + 1

SHDLOC + 15

Edge location

Pipeline Delay from SHP/SHD Sampling to DOUT

16

Cycles

SERIAL INTERFACE (See Figure 83)

Maximum SCK Frequency (Must Not Exceed CLI Frequency)

fSCLK

40

MHz

SL to SCK Setup Time

tLS

10

ns

SCK to SL Hold Time

tLH

10

ns

SDATA Valid to SCK Rising Edge Setup

tDS

10

ns

SCK Falling Edge to SDATA Valid Hold

tDH

10

ns

INHIBIT REGION FOR SHP AND SHD WITH RESPECT TO H-CLOCK

EDGE PLACEMENT (see Figure 19) for H*POL = 1

RETIME = 0, MASK = 0

tSHDINH

H*NEGLOC – 15

H*NEGLOC – 0

Edge location

RETIME = 0, MASK = 1

tSHDINH

H*POSLOC – 15

H*POSLOC – 0

Edge location

RETIME = 1, MASK = 0

tSHPINH

H*NEGLOC – 15

H*NEGLOC – 0

Edge location

RETIME = 1, MASK = 1

tSHPINH

H*POSLOC – 15

H*POSLOC – 0

Edge location

1 Parameter is programmable.

2 Minimum CLPOB pulse width is for functional operation only. Wider typical pulses are recommended to achieve good clamp performance.

相关PDF资料 |

PDF描述 |

|---|---|

| AD9995KCPZ | IC CCD SIGNAL PROCESSOR 56-LFCSP |

| ADA4424-6ARUZ | IC FILTR VID6CH SD/ED/HD 38TSSOP |

| ADATE302-02BBCZ | IC DCL ATE 500MHZ DUAL 84CSPBGA |

| ADATE304BBCZ | IC DCL ATE 200MHZ DUAL 84CSPBGA |

| ADATE305BSVZ | IC DCL ATE 250MHZ DUAL 100TQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9993BBCZ | 功能描述:IC MIXED-SIGNAL FRONT END 196BGA 制造商:analog devices inc. 系列:- 包装:托盘 零件状态:在售 类型:ADC,DAC 输入类型:LVDS 输出类型:LVDS 接口:SPI 电流 - 电源:- 工作温度:- 安装类型:表面贴装 封装/外壳:196-LFBGA,CSPBGA 供应商器件封装:196-CSPBGA(12x12) 标准包装:1 |

| AD9993BBCZRL | 功能描述:IC MIXED-SIGNAL FRONT END 196BGA 制造商:analog devices inc. 系列:- 包装:带卷(TR) 零件状态:在售 类型:ADC,DAC 输入类型:LVDS 输出类型:LVDS 接口:SPI 电流 - 电源:- 工作温度:- 安装类型:表面贴装 封装/外壳:196-LFBGA,CSPBGA 供应商器件封装:196-CSPBGA(12x12) 标准包装:1,500 |

| AD9993-EBZ | 功能描述:EVAL BOARD MXFE AD9993 制造商:analog devices inc. 系列:* 零件状态:在售 标准包装:1 |

| AD9994 | 制造商:AD 制造商全称:Analog Devices 功能描述:12-Bit CCD Signal Processor with Precision Timing Generator |

| AD9994BCP | 制造商:Analog Devices 功能描述:AFE GEN PURPOSE 12-BIT 64LFCSP - Bulk |

发布紧急采购,3分钟左右您将得到回复。