- 您现在的位置:买卖IC网 > PDF目录378276 > ADAV801ASTZ-REEL (ANALOG DEVICES INC) Audio Codec for Recordable DVD PDF资料下载

参数资料

| 型号: | ADAV801ASTZ-REEL |

| 厂商: | ANALOG DEVICES INC |

| 元件分类: | 消费家电 |

| 英文描述: | Audio Codec for Recordable DVD |

| 中文描述: | SPECIALTY CONSUMER CIRCUIT, PDSO64 |

| 封装: | ROHS COMPLIANT, MS-026BCD, LQFP-64 |

| 文件页数: | 23/56页 |

| 文件大小: | 1405K |

| 代理商: | ADAV801ASTZ-REEL |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页当前第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页

ADAV801

Rev. 0 | Page 23 of 56

0

PLL1 MCLK

PLL2 MCLK

48kHz

32kHz

44.1kHz

256

384

REG 0x75

BITS 3–2

REG

BIT 0

REG 0x75

BIT 1

0x75

REG 0x77

BIT 0

PLL1

PLLINT1

SYSCLK1

×2

FS1

÷

2

REG 0x75

BIT 5

REG 0x75

BIT 4

REG 0x77

BITS 2–1

x7

7–6

PLL2

PLLINT2

SYSCLK2

REG 0

BITS

5

REG 0x74

BIT 0

SYSCLK3

48kHz

32kHz

44.1kHz

256

384

×2

FS2

FS3

÷

2

÷

2

256

512

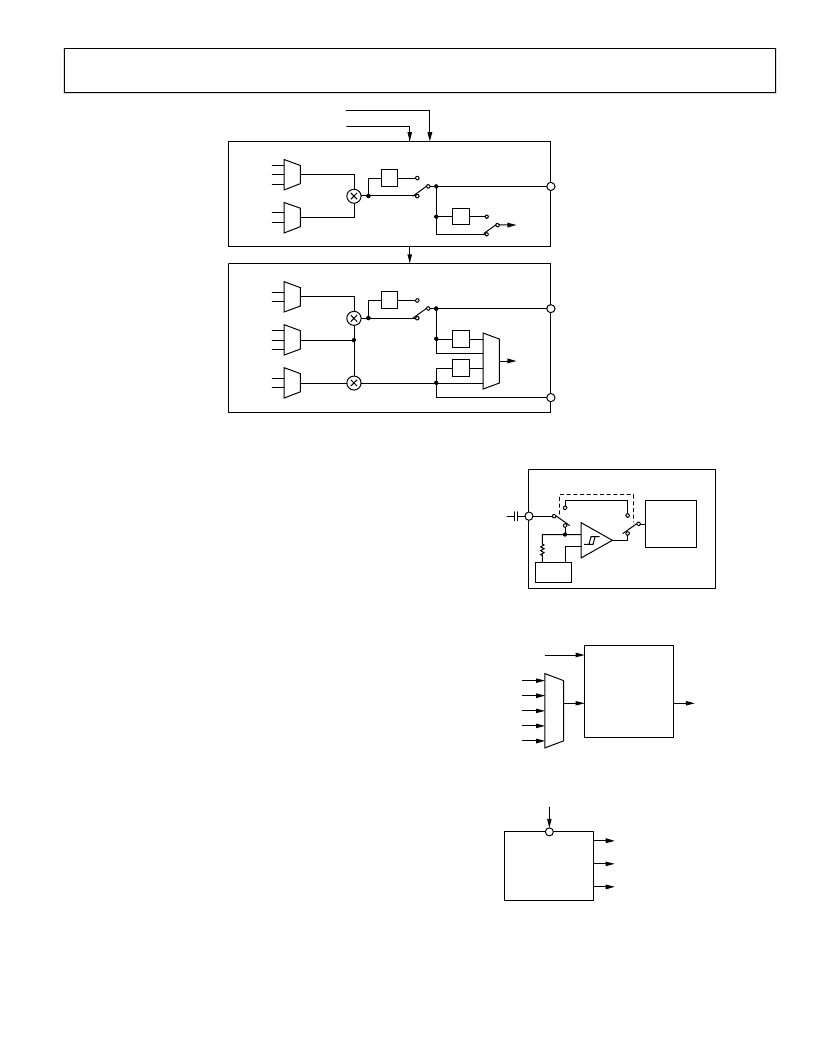

Figure 38. PLL Clocking Scheme

SPDIF TRANSMITTER AND RECEIVER

The ADAV801 contains an integrated SPDIF transmitter and

receiver. The transmitter consists of a single output pin,

DITOUT, on which the biphase encoded data appears. The

SPDIF transmitter source can be selected from the different

blocks making up the ADAV801. Additionally, the clock source

for the SPDIF transmitter can be selected from the various clock

sources available in the ADAV801.

The receiver uses two pins, DIRIN and DIR_LF. DIRIN accepts

the SPDIF input data stream. The DIRIN pin can be configured

to accept a digital input level, as defined in the Specifications

section, or an input signal with a peak-to-peak level of 200 mV

minimum, as defined by the IEC60958-3 specification. DIR_LF

is a loop filter pin, required by the internal PLL, which is used to

recover the clock from the SPDIF data stream.

The components shown in Figure 42 form a loop filter, which

integrates the current pulses from a charge pump and produces

a voltage that is used to tune the VCO of the clock recovery

PLL. The recovered audio data and audio clock can be routed to

the different blocks of the ADAV801, as required. Figure 39

shows a conceptual diagram of the DIRIN block.

C*

0

SPDIF

* EXTERNAL CAPACITOR IS REQUIRED ONLY

FOR VARIABLE LEVEL SPDIF INPUTS.

COMPARATOR

REG 0x74

BIT 4

DIRIN

DC

LEVEL

SPDIF

RECEIVER

Figure 39. DIRIN Block

0

DIT

INPUT

DIT

PLAYBACK

AUXILIARY IN

SRC

REG 0x63

BITS 2–0

ADC

CHANNEL STATUS

AND USER BITS

DIR

DITOUT

Figure 40. Digital Output Transmitter Block Diagram

0

DIR

DIRIN

AUDIO

DATA

RECOVERED

CLOCK

CHANNEL STATUS/

USER BITS

Figure 41. Digital Input Receiver Block Diagram

相关PDF资料 |

PDF描述 |

|---|---|

| ADC0800PCD | ADC0800 8-Bit A/D Converter |

| ADC0800PD | ADC0800 8-Bit A/D Converter |

| ADC0800 | ECONOLINE: REC3-S_DRW(Z)/H* - 3W DIP Package- 1kVDC Isolation- Wide Input 2:1 & 4:1- Regulated Output- 100% Burned In- UL94V-0 Package Material- Continuous Short Circiut Protection- Efficiency to 80% |

| ADC08031 | 8-Bit High-Speed Serial I/O A/D Converters with Multiplexer Options, <BR> Voltage Reference, and Track/Hold Function |

| ADC08031CIN | 8-Bit High-Speed Serial I/O A/D Converters with Multiplexer Options, <BR> Voltage Reference, and Track/Hold Function |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADAV802AST | 制造商:Analog Devices 功能描述:AUDIO CODEC FOR RECORDABLE DVD - Bulk |

| ADAV802ASTZ | 制造商:Analog Devices 功能描述: |

| ADAV803 | 制造商:AD 制造商全称:Analog Devices 功能描述:Audio Codec for Recordable DVD |

| ADAV803AST | 制造商:Analog Devices 功能描述:AUDIO CODEC FOR RECORDABLE DVD - Bulk |

| ADAV803ASTZ | 功能描述:IC CODEC AUDIO R-DVD 3.3V 64LQFP RoHS:是 类别:集成电路 (IC) >> 接口 - 编解码器 系列:- 标准包装:2,500 系列:- 类型:立体声音频 数据接口:串行 分辨率(位):18 b ADC / DAC 数量:2 / 2 三角积分调变:是 S/N 比,标准 ADC / DAC (db):81.5 / 88 动态范围,标准 ADC / DAC (db):82 / 87.5 电压 - 电源,模拟:2.6 V ~ 3.3 V 电压 - 电源,数字:1.7 V ~ 3.3 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-WFQFN 裸露焊盘 供应商设备封装:48-TQFN-EP(7x7) 包装:带卷 (TR) |

发布紧急采购,3分钟左右您将得到回复。