- 您现在的位置:买卖IC网 > PDF目录378276 > ADAV801ASTZ-REEL (ANALOG DEVICES INC) Audio Codec for Recordable DVD PDF资料下载

参数资料

| 型号: | ADAV801ASTZ-REEL |

| 厂商: | ANALOG DEVICES INC |

| 元件分类: | 消费家电 |

| 英文描述: | Audio Codec for Recordable DVD |

| 中文描述: | SPECIALTY CONSUMER CIRCUIT, PDSO64 |

| 封装: | ROHS COMPLIANT, MS-026BCD, LQFP-64 |

| 文件页数: | 25/56页 |

| 文件大小: | 1405K |

| 代理商: | ADAV801ASTZ-REEL |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页当前第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页

ADAV801

Table 10. Professional Audio Standard

Address

7

6

Rev. 0 | Page 25 of 56

Data Bits

5

4

3

2

1

0

N

Sample

Frequency

Lock

Emphasis

Non-

Audio

Pro/

Con

= 1

N + 1

User Bit Management

Alignm

Level

Channel Mode

Use of Auxiliary Mode

Sample Bits

N + 2

ent

Source Word Length

N + 3

Channel Identification

N + 4

f

S

Scal-

ing

Reference

Signal

Sample Frequency (f

S

)

Reserved

Digital Audio

N + 5

N + 6

N + 7

N + 8

N + 9

N + 1

N + 11

N + 12

N + 1

N + 14

N + 15

N + 16

N + 17

N + 18

N + 19

N + 20

N + 21

N + 22

N + 23

N = 0x20 for receiver channel status buffer.

N = 0x38 for transmitter channel status buffer.

Reserved

Alphanumeric Channel Origin Data—First Character

Alphanumeric Channel Origin Data

Alphanumeric Channel Origin Data

el Origin Data—Last Character

Alphanumeric Chann

lp

A hanumeric Channel Destinat

Alphanumeric Channel Destination Data

Alphanumeric Channel Destination Data

Al

phanumeric Channel Destination Data—Last Character

Local Sample Address Code—LSW

Local Sample Address Code

Local Sample Address Code

Local Sample Address Code—MSW

Time of Day Code—LSW

Time of Day Code

Time of Day Code

Time of Day Code—MSW

Reliability Flags

Cyclic Redundancy Check Character (CRCC)

ion Data—First Character

0

3

Reserved

are

organized into 24 bytes and have the interpretations shown in

Table 9 and Table 10.

d

the need for user intervention.

Receiver Section

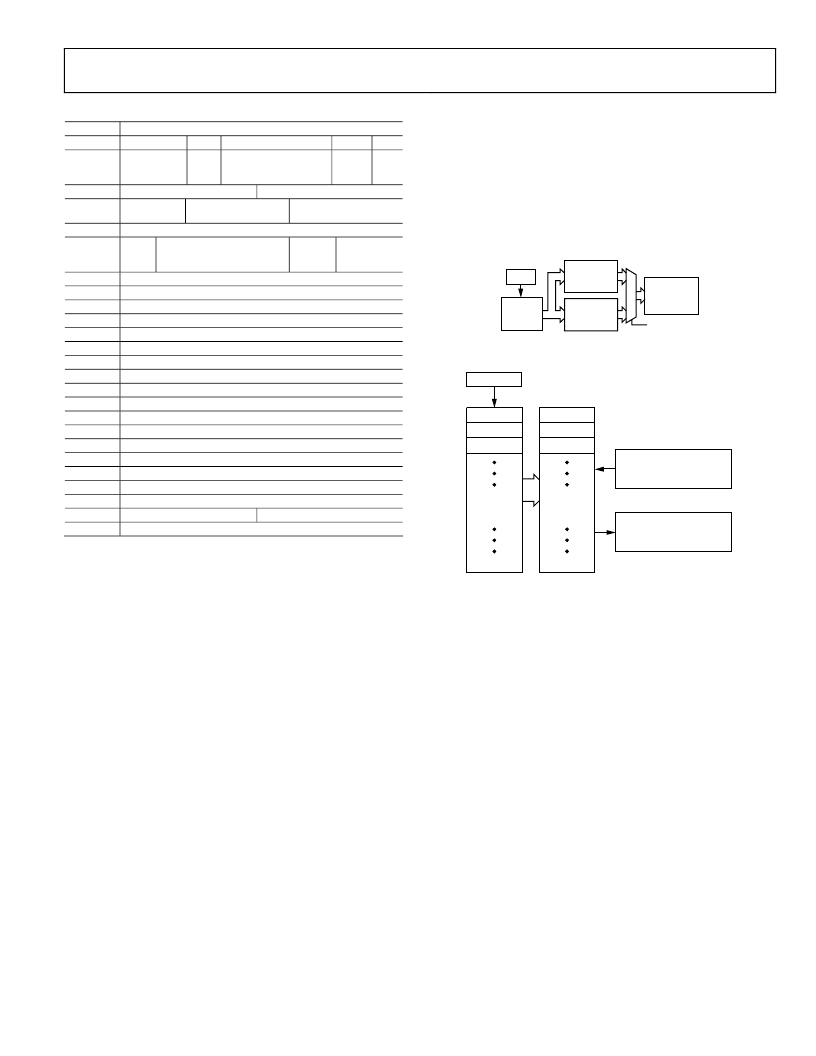

The ADAV801 uses a double-buffering scheme to handle read-

ing channel status and user bit information. The channel status

bits are available as a memory buffer, taking up 24 consecutive

register locations. The user bits are read using an indirect

memory addressing scheme, where the receiver user- bit

indirect-address register is programmed with an offset to the

iver user bit data register can be read

er

read

d

The standards allow the channel status bits in each subframe to

be independent, but ordinarily the channel status bit in the two

subframes of each frame are the same. The channel status bits

are defined differently for the consumer audio standards and

the professional audio standards. The 192 channel status bits

The SPDIF transmitter and receiver have a comprehensive

register set. The registers give the user full access to the

functions of the SPDIF block, such as detecting nonaudio an

validity bits, Q subcodes, preambles, and so on. The channel

status bits as defined by the IEC60958 and AES3 specifications

are stored in register buffers for ease of use. An autobuffering

function allows channel status bits and user bits read by the

receiver to be copied directly to the transmitter block, removing

user bit buffer, and the rece

to determine the user bits at that location. Reading the receiv

user bit data register automatically updates the indirect address

register to the next location in the buffer. Typically, the receiver

user bit indirect-address register is programmed to zero (the

start of the buffer), and the receiver user bit data register is

repeatedly until all the buffer’s data has been read. Figure 46 an

Figure 47 show how receiving the channel status bits and user

bits is implemented.

0

SECONDBUFFER

RECEIVE

CS BUFFER

(0x20–0x37)

CHANNEL

STATUS A

(24 × 8 BITS)

DIRIN

CHANNEL

STATUS B

(24 × 8 BITS)

RxCSSWITCH

SPDIF

RECEIVE

BUFFER

FIRST BUFFER

Figure 46. Channel Status Buffer

0

BUFFER

SPDIFIN

0...7

8...15

16...23

FIRST

0...7

8...15

16...23

USER-BIT

BUFFER

ADDRESS = 0x50

ADDRESS = 0x51

RECEIVER USER BIT

INDIRECT ADDRESS

REGISTER

RECEIVER USER BIT

DATA REGISTER

Figure 47. Receiver User Bit Buffer

The SPDIF receive buffer is updated continuously by the

incoming SPDIF stream. Once all the channel status bits f

block (192 for Channel A and 192 for Channel B) are recei

the bits are copied into the receiver channel status buffer.

buffer stores all 384 bits of channel status information, an

RxCSSWITCH

t i

determ es wh

er the Channel A or the Channel B status bits

are r

red

read. The receive channel status bit buf

24

lon

spans the address range from 0x20 to 0x37.

or the

ved,

This

d the

bi n the channel status switch buffer register

eth

to be

g and

in

equi

bytes

fer is

Because the chan

change, a software

tify th

bits is available or

formation have changed from a previous block. The function

of the RxCSBINT is controlled by the RxBCONF3 bit in the

receiver buffer configuration register.

T, is provided to

ost co

e h

tatus

status

The size of the user bit buffer can be set by programming the

RxBCONF0 bit in the receiver buffer configuration register, as

shown in Table 11.

nel status bits of an SPDIF stream rarely

interrupt/flag bit, RxCSBIN

ntrol that either a new block of channel s

that the first five bytes of channel

no

in

相关PDF资料 |

PDF描述 |

|---|---|

| ADC0800PCD | ADC0800 8-Bit A/D Converter |

| ADC0800PD | ADC0800 8-Bit A/D Converter |

| ADC0800 | ECONOLINE: REC3-S_DRW(Z)/H* - 3W DIP Package- 1kVDC Isolation- Wide Input 2:1 & 4:1- Regulated Output- 100% Burned In- UL94V-0 Package Material- Continuous Short Circiut Protection- Efficiency to 80% |

| ADC08031 | 8-Bit High-Speed Serial I/O A/D Converters with Multiplexer Options, <BR> Voltage Reference, and Track/Hold Function |

| ADC08031CIN | 8-Bit High-Speed Serial I/O A/D Converters with Multiplexer Options, <BR> Voltage Reference, and Track/Hold Function |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADAV802AST | 制造商:Analog Devices 功能描述:AUDIO CODEC FOR RECORDABLE DVD - Bulk |

| ADAV802ASTZ | 制造商:Analog Devices 功能描述: |

| ADAV803 | 制造商:AD 制造商全称:Analog Devices 功能描述:Audio Codec for Recordable DVD |

| ADAV803AST | 制造商:Analog Devices 功能描述:AUDIO CODEC FOR RECORDABLE DVD - Bulk |

| ADAV803ASTZ | 功能描述:IC CODEC AUDIO R-DVD 3.3V 64LQFP RoHS:是 类别:集成电路 (IC) >> 接口 - 编解码器 系列:- 标准包装:2,500 系列:- 类型:立体声音频 数据接口:串行 分辨率(位):18 b ADC / DAC 数量:2 / 2 三角积分调变:是 S/N 比,标准 ADC / DAC (db):81.5 / 88 动态范围,标准 ADC / DAC (db):82 / 87.5 电压 - 电源,模拟:2.6 V ~ 3.3 V 电压 - 电源,数字:1.7 V ~ 3.3 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-WFQFN 裸露焊盘 供应商设备封装:48-TQFN-EP(7x7) 包装:带卷 (TR) |

发布紧急采购,3分钟左右您将得到回复。