- 您现在的位置:买卖IC网 > PDF目录378276 > ADAV801ASTZ-REEL (ANALOG DEVICES INC) Audio Codec for Recordable DVD PDF资料下载

参数资料

| 型号: | ADAV801ASTZ-REEL |

| 厂商: | ANALOG DEVICES INC |

| 元件分类: | 消费家电 |

| 英文描述: | Audio Codec for Recordable DVD |

| 中文描述: | SPECIALTY CONSUMER CIRCUIT, PDSO64 |

| 封装: | ROHS COMPLIANT, MS-026BCD, LQFP-64 |

| 文件页数: | 54/56页 |

| 文件大小: | 1405K |

| 代理商: | ADAV801ASTZ-REEL |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页当前第54页第55页第56页

ADAV801

LAYOUT CONSIDERATIONS

Getting the best performance from the ADAV801 requires a

careful layout of the printed circuit board (PCB). Using separate

analog and digital ground planes is recommended, because

these give the currents a low resistance path back to the power

supplies. The ground planes should be connected in only one

place, usually under the ADAV801, to prevent ground loops.

Rev. 0 | Page 54 of 56

The analog and digital supply pins should be decoupled to their

respective ground pins with a 10 μF to 47 μF tantalum capacitor

and a 0.1 μF ceramic capacitor. These capacitors should be

placed as close as possible to the supply pins.

ADC

The ADC uses a switch capacitor input stage and is, therefore,

particularly sensitive to digital noise. Sources of noise, such as

PLLs or clocks, should not be routed close to the ADC section.

The CAPxN and CAPxP pins form a charge reservoir for the

switched capacitor section of the ADC, so keeping these nodes

electrically quiet is a key factor in ensuring good performance.

The capacitors connected to these pins should be of good

quality, either NPO or COG, and should be placed as close as

possible to CAPxN and CAPxP.

DAC

The DAC requires an analog filter to filter out-of-band noise

from the analog output. A third-order Bessel filter is

recommended, although the filter to use depends on the

f the application.

requirements o

PLL

The PLL can be used to generate digital clocks, either for use

internally or to clock external circuitry. Because every clock is a

potential source of noise, care should be taken when using the

PLL. The ADAV801’s PLL outputs can be enabled or disabled, as

required. If the PLL clocks are not required by external circuitry,

it is recommended that the outputs be disabled. To reduce

cross-coupling between clocks, a digital ground trace can be

routed on either side of the PLL clock signal, if required.

The PLL has its own power supply pins. To get the best

performance from the PLL and from the rest of the ADAV801,

it is recommended that a separate analog supply be used. Where

this is not possible, the user must decide whether to connect the

PLL supply to the analog (AV

DD

) or digital (DV

DD

) supply.

Connecting the PLL supply to AV

DD

gives the best jitter

performance, but can degrade the performance of the ADC and

DAC sections slightly due to the increased digital noise created

on the AV

DD

by the PLL. Connecting the PLL supply to DV

DD

keeps digital noise away from the analog supply, but the jitter

specifications might be reduced depending on the quality of the

digital supply. Using the layout recommendations described in

this section helps to reduce these effects.

RESET AND POWER-DOWN CONSIDERATIONS

When the ADAV801 is held in reset by bringing the RESET

pin low, a number of circuit blocks remain powered up. For

example, the crystal oscillator circuit based around the XIN

and XOUT pins is still active, so that a stable clock source is

available when the ADAV801 is taken out of reset. Also, the

VCO associated with the SPDIF receiver is active so that the

receiver locks to the incoming SPDIF stream in the shortest

possible time. Where power consumption is a concern, the

individual blocks of the ADAV801 can be powered down via

the control registers to gain significant power savings. Table 82

shows typical power savings when using the power-down bits

in the control registers.

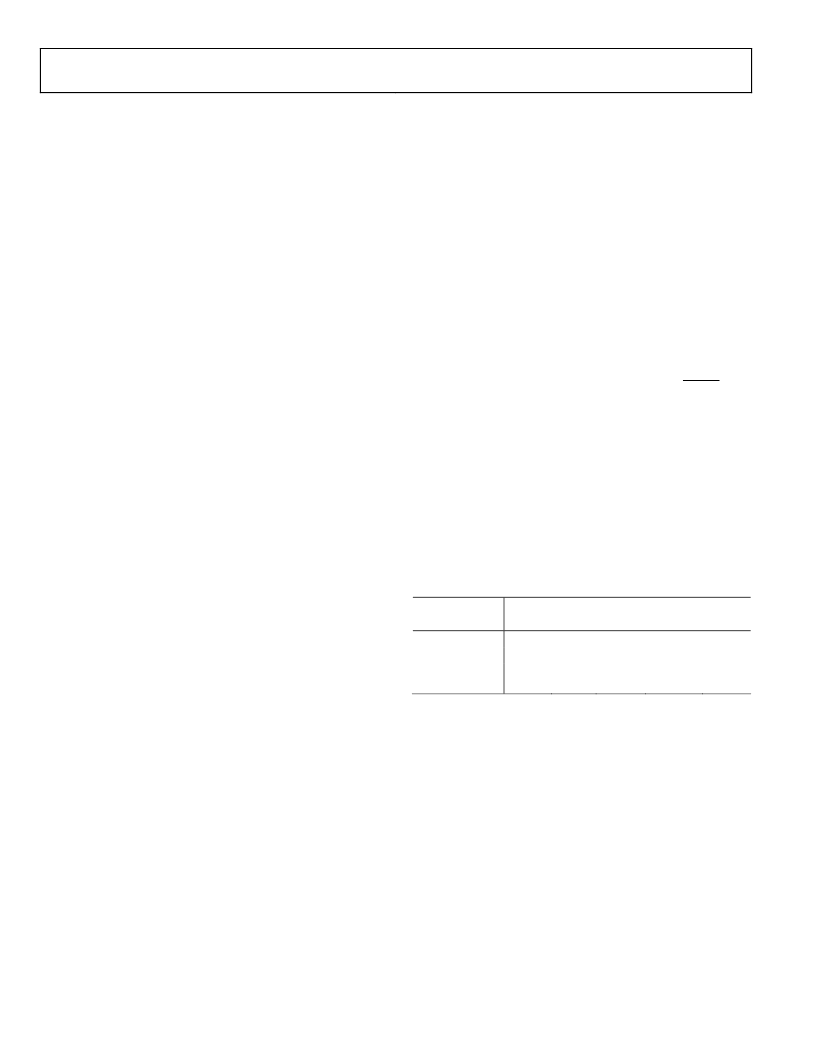

Table 82. Typical Power Requirements

Operating

Mode

(mA)

(mA)

Normal

50

25

Reset low

30

4

Power-down

bits

AV

DD

DV

DD

ODV

DD

(mA)

5

2.5

1.3

DIR_V

DD

(mA)

5

1

0.7

Power

(mW)

280.5

123.75

46.53

12

0.1

相关PDF资料 |

PDF描述 |

|---|---|

| ADC0800PCD | ADC0800 8-Bit A/D Converter |

| ADC0800PD | ADC0800 8-Bit A/D Converter |

| ADC0800 | ECONOLINE: REC3-S_DRW(Z)/H* - 3W DIP Package- 1kVDC Isolation- Wide Input 2:1 & 4:1- Regulated Output- 100% Burned In- UL94V-0 Package Material- Continuous Short Circiut Protection- Efficiency to 80% |

| ADC08031 | 8-Bit High-Speed Serial I/O A/D Converters with Multiplexer Options, <BR> Voltage Reference, and Track/Hold Function |

| ADC08031CIN | 8-Bit High-Speed Serial I/O A/D Converters with Multiplexer Options, <BR> Voltage Reference, and Track/Hold Function |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADAV802AST | 制造商:Analog Devices 功能描述:AUDIO CODEC FOR RECORDABLE DVD - Bulk |

| ADAV802ASTZ | 制造商:Analog Devices 功能描述: |

| ADAV803 | 制造商:AD 制造商全称:Analog Devices 功能描述:Audio Codec for Recordable DVD |

| ADAV803AST | 制造商:Analog Devices 功能描述:AUDIO CODEC FOR RECORDABLE DVD - Bulk |

| ADAV803ASTZ | 功能描述:IC CODEC AUDIO R-DVD 3.3V 64LQFP RoHS:是 类别:集成电路 (IC) >> 接口 - 编解码器 系列:- 标准包装:2,500 系列:- 类型:立体声音频 数据接口:串行 分辨率(位):18 b ADC / DAC 数量:2 / 2 三角积分调变:是 S/N 比,标准 ADC / DAC (db):81.5 / 88 动态范围,标准 ADC / DAC (db):82 / 87.5 电压 - 电源,模拟:2.6 V ~ 3.3 V 电压 - 电源,数字:1.7 V ~ 3.3 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-WFQFN 裸露焊盘 供应商设备封装:48-TQFN-EP(7x7) 包装:带卷 (TR) |

发布紧急采购,3分钟左右您将得到回复。