- 您现在的位置:买卖IC网 > PDF目录10950 > ADAV801ASTZ (Analog Devices Inc)IC CODEC AUDIO R-DVD 3.3V 64LQFP PDF资料下载

参数资料

| 型号: | ADAV801ASTZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 13/60页 |

| 文件大小: | 0K |

| 描述: | IC CODEC AUDIO R-DVD 3.3V 64LQFP |

| 标准包装: | 1 |

| 类型: | 音频编解码器 |

| 数据接口: | 串行 |

| 分辨率(位): | 24 b |

| ADC / DAC 数量: | 2 / 2 |

| 三角积分调变: | 无 |

| 动态范围,标准 ADC / DAC (db): | 102 / 101 |

| 电压 - 电源,模拟: | 3 V ~ 3.6 V |

| 电压 - 电源,数字: | 3 V ~ 3.6 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 64-LQFP |

| 供应商设备封装: | 64-LQFP(10x10) |

| 包装: | 托盘 |

| 配用: | EVAL-ADAV801EBZ-ND - BOARD EVALUATION FOR ADAV801 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页当前第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页

ADAV801

Rev. A | Page 20 of 60

The worst-case images can be computed from the zero-order

hold frequency response:

Maximum Image = sin(π × F/fS_INTERP)/(π × F/fS_INTERP)

where:

F is the frequency of the worst-case image that would be

220 × fS_IN ± fS_IN/2.

fS_INTERP = fS_IN × 220.

The following worst-case images would appear for fS_IN equal to

192 kHz:

Image at fS_INTERP 96 kHz = 125.1 dB

Image at fS_INTERP + 96 kHz = 125.1 dB

Hardware Model

The output rate of the low-pass filter in Figure 30 is the

interpolation rate:

220 × 192,000 kHz = 201.3 GHz

Sampling at a rate of 201.3 GHz is clearly impractical, in

addition to the number of taps required to calculate each

interpolated sample. However, because interpolation by 220

involves zero-stuffing 220 1 samples between each fS_IN sample,

most of the multiplies in the low-pass FIR filter are by zero. A

further reduction can be realized because only one interpolated

sample is taken at the output at the fS_OUT rate, so only one

convolution needs to be performed per fS_OUT period instead of

220 convolutions. A 64-tap FIR filter for each fS_OUT sample is

sufficient to suppress the images caused by the interpolation.

One difficulty with the preceding approach is that the correct

interpolated sample must be selected upon the arrival of fS_OUT.

Because there are 220 possible convolutions per fS_OUT period, the

arrival of the fS_OUT clock must be measured with an accuracy of

1/201.3 GHz = 4.96 ps. Measuring the fS_OUT period with a clock

of 201.3 GHz frequency is clearly impossible; instead, several

coarse measurements of the fS_OUT clock period are made and

averaged over time.

Another difficulty with the preceding approach is the number

of coefficients required. Because there are 220 possible convolu-

tions with a 64-tap FIR filter, there must be 220 polyphase

coefficients for each tap, which requires a total of 226 coeffi-

cients. To reduce the number of coefficients in ROM, the SRC

stores a small subset of coefficients and performs a high order

interpolation between the stored coefficients.

The preceding approach works when fS_OUT > fS_IN. However,

when the output sample rate, fS_OUT, is less than the input sample

rate, fS_IN, the ROM starting address, input data, and length of

the convolution must be scaled. As the input sample rate rises

over the output sample rate, the antialiasing filter’s cutoff

frequency must be lowered because the Nyquist frequency of

the output samples is less than the Nyquist frequency of the

input samples. To move the cutoff frequency of the antialiasing

filter, the coefficients are dynamically altered and the length of

the convolution is increased by a factor of (fS_IN/fS_OUT).

This technique is supported by the Fourier transform property

that, if f(t) is F(ω), then f(k × t) is F(ω/k). Thus, the range of

decimation is limited by the size of the RAM.

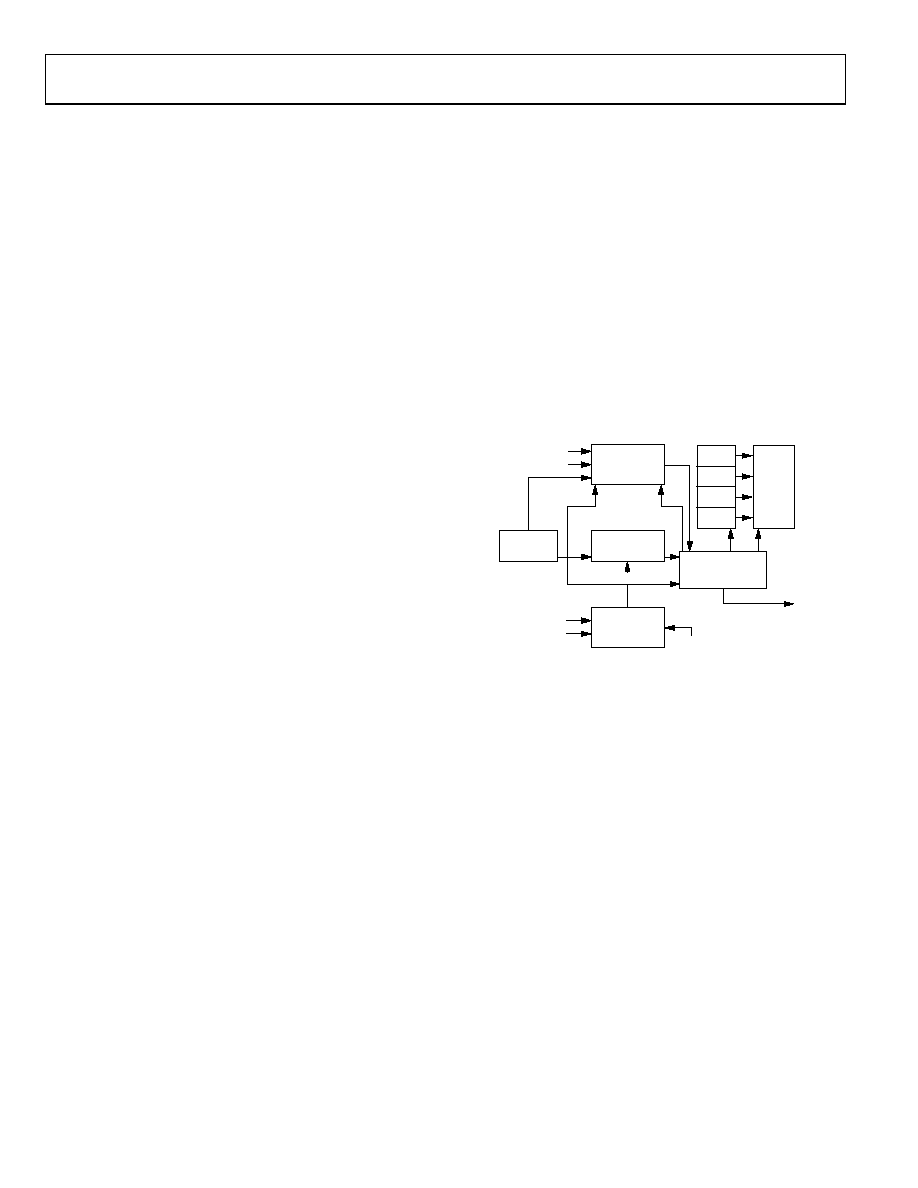

SRC Architecture

The architecture of the sample rate converter is shown in

Figure 32. The sample rate converter’s FIFO block adjusts the

left and right input samples and stores them for the FIR filter’s

convolution cycle. The fS_IN counter provides the write address

to the FIFO block and the ramp input to the digital servo loop.

The ROM stores the coefficients for the FIR filter convolution

and performs a high order interpolation between the stored

coefficients. The sample rate ratio block measures the sample

rate for dynamically altering the ROM coefficients and scaling

of the FIR filter length as well as the input data. The digital

servo loop automatically tracks the fS_IN and fS_OUT sample rates

and provides the RAM and ROM start addresses for the start of

the FIR filter convolution.

04

57

7-

0

12

RIGHT DATA IN

LEFT DATA IN

FIFO

DIGITAL

SERVO LOOP

fS_IN

COUNTER

ROM A

ROM B

ROM C

ROM D

fS_IN

fS_OUT

SAMPLE RATE RATIO

SAMPLE

RATE RATIO

EXTERNAL

RATIO

HIGH

ORDER

INTERP

FIR FILTER

L/R DATA OUT

Figure 32. Architecture of the Sample Rate Converter

The FIFO receives the left and right input data and adjusts the

amplitude of the data for both the soft muting of the sample rate

converter and the scaling of the input data by the sample rate

ratio before storing the samples in the RAM. The input data is

scaled by the sample rate ratio because, as the FIR filter length

of the convolution increases, so does the amplitude of the

convolution output. To keep the output of the FIR filter from

saturating, the input data is scaled down by multiplying it by

(fS_OUT/fS_IN) when fS_OUT < fS_IN. The FIFO also scales the input

data for muting and unmuting of the SRC.

The RAM in the FIFO is 512 words deep for both left and right

channels. An offset to the write address provided by the fS_IN

counter is added to prevent the RAM read pointer from

overlapping the write address. The minimum offset on the SRC

is 16 samples. However, the group delay and mute-in register

can be used to increase this offset.

The number of input samples added to the write pointer of the

FIFO on the SRC is 16 plus Bit 6 to Bit 0 of the group delay

register. This feature is useful in varispeed applications to

prevent the read pointer to the FIFO from running ahead of the

write pointer. When set, Bit 7 of the group delay and mute-in

register soft-mutes the sample rate. Increasing the offset of the

相关PDF资料 |

PDF描述 |

|---|---|

| MCIMX27LVOP4AR2 | IC LOW END I.MX27 404-MAPBGA |

| AD1938YSTZ | IC CODEC 24BIT 4ADC/8DAC 48LQFP |

| MC56F8335MFGE | IC DIGITAL SIGNAL CTLR 128-LQFP |

| MC9S12XHZ512CAG | IC MCU 16BIT 512 FLASH 144-LQFP |

| MC9S12C96MPBE | IC MCU 96K FLASH 4K RAM 52-LQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADAV801ASTZ-REEL | 功能描述:IC CODEC AUDIO R-DVD 3.3V 64LQFP RoHS:是 类别:集成电路 (IC) >> 接口 - 编解码器 系列:- 标准包装:2,500 系列:- 类型:立体声音频 数据接口:串行 分辨率(位):18 b ADC / DAC 数量:2 / 2 三角积分调变:是 S/N 比,标准 ADC / DAC (db):81.5 / 88 动态范围,标准 ADC / DAC (db):82 / 87.5 电压 - 电源,模拟:2.6 V ~ 3.3 V 电压 - 电源,数字:1.7 V ~ 3.3 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-WFQFN 裸露焊盘 供应商设备封装:48-TQFN-EP(7x7) 包装:带卷 (TR) |

| ADAV802AST | 制造商:Analog Devices 功能描述:AUDIO CODEC FOR RECORDABLE DVD - Bulk |

| ADAV802ASTZ | 制造商:Analog Devices 功能描述: |

| ADAV803 | 制造商:AD 制造商全称:Analog Devices 功能描述:Audio Codec for Recordable DVD |

| ADAV803AST | 制造商:Analog Devices 功能描述:AUDIO CODEC FOR RECORDABLE DVD - Bulk |

发布紧急采购,3分钟左右您将得到回复。