- 您现在的位置:买卖IC网 > PDF目录9218 > ADF4350BCPZ-RL7 (Analog Devices Inc)IC SYNTH PLL VCO FN/IN 32LFCSP PDF资料下载

参数资料

| 型号: | ADF4350BCPZ-RL7 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 3/32页 |

| 文件大小: | 0K |

| 描述: | IC SYNTH PLL VCO FN/IN 32LFCSP |

| 产品变化通告: | ADF4350, ADF4905/6 N-counter Change 05/Mar/2012 |

| 设计资源: | Broadband Low EVM Direct Conversion Transmitter (CN0134) Broadband Low EVM Direct Conversion Transmitter Using LO Divide-by-2 Modulator (CN0144) Using low noise linear drop-out regulators to power wideband PLL & VCO IC's (CN0147) |

| 特色产品: | ADF4350: Wideband PLL Synthesizer with integrated VCO |

| 标准包装: | 1 |

| 类型: | 扇出配送,分数-N,整数-N,时钟/频率合成器(RF) |

| PLL: | 是 |

| 输入: | CMOS |

| 输出: | 时钟 |

| 电路数: | 1 |

| 比率 - 输入:输出: | 1:3 |

| 差分 - 输入:输出: | 无/无 |

| 频率 - 最大: | 4.4GHz |

| 除法器/乘法器: | 是/是 |

| 电源电压: | 3 V ~ 3.6 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 32-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 32-LFCSP-VQ(5x5) |

| 包装: | 标准包装 |

| 产品目录页面: | 551 (CN2011-ZH PDF) |

| 其它名称: | ADF4350BCPZ-RL7DKR |

第1页第2页当前第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页

ADF4350

Rev. A | Page 11 of 32

CIRCUIT DESCRIPTION

REFERENCE INPUT SECTION

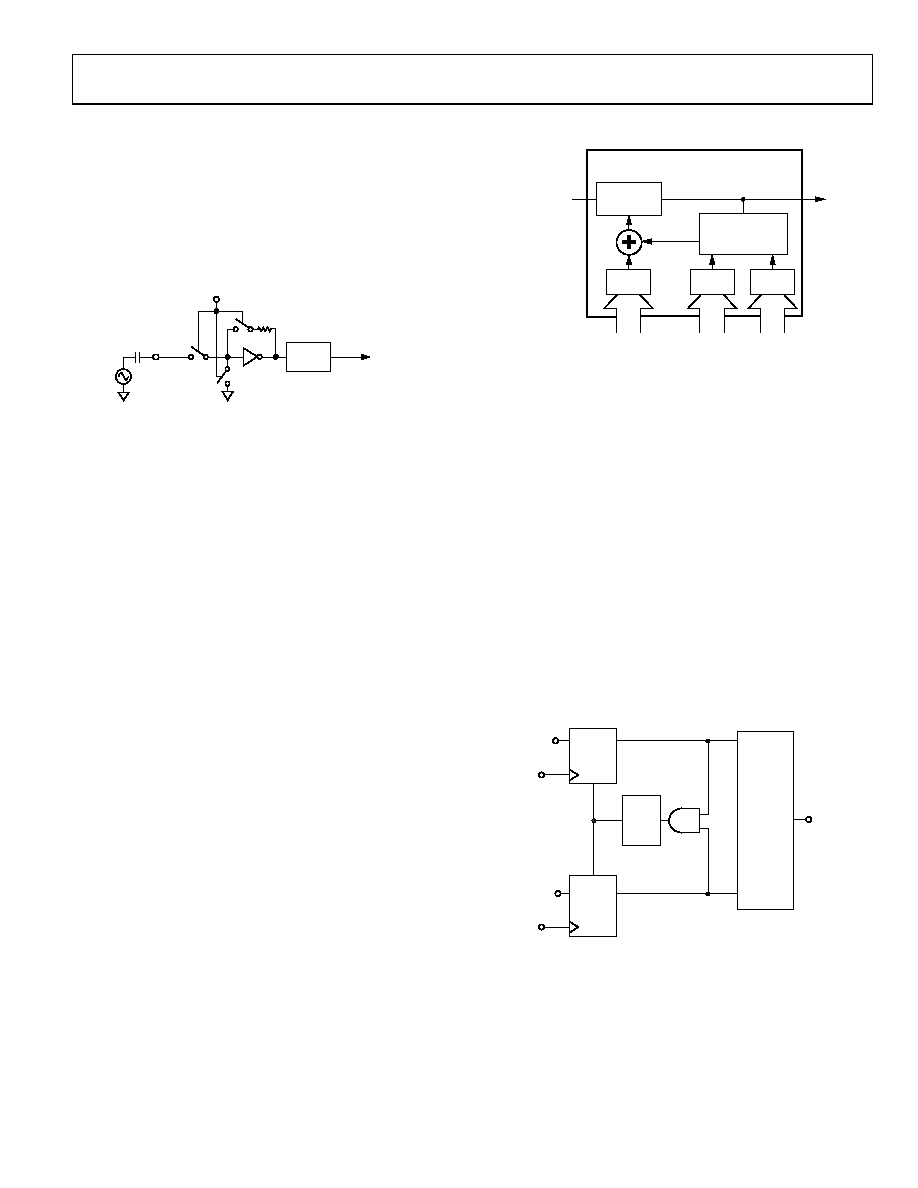

The reference input stage is shown in Figure 16. SW1 and SW2

are normally closed switches. SW3 is normally open. When

power-down is initiated, SW3 is closed, and SW1 and SW2 are

opened. This ensures that there is no loading of the REFIN pin

during power-down.

07

32

5-

0

5

BUFFER

TO R COUNTER

REFIN

100k

NC

SW2

SW3

NO

NC

SW1

POWER-DOWN

CONTROL

Figure 16. Reference Input Stage

RF N DIVIDER

The RF N divider allows a division ratio in the PLL feedback

path. The division ratio is determined by INT, FRAC and MOD

values, which build up this divider.

INT, FRAC, MOD, AND R COUNTER RELATIONSHIP

The INT, FRAC, and MOD values, in conjunction with the

R counter, make it possible to generate output frequencies

that are spaced by fractions of the PFD frequency. See the RF

Synthesizer—A Worked Example section for more information.

The RF VCO frequency (RFOUT) equation is

RFOUT = fPFD × (INT + (FRAC/MOD))

(1)

where RFOUT is the output frequency of external voltage

controlled oscillator (VCO).

INT is the preset divide ratio of the binary 16-bit counter

(23 to 65535 for 4/5 prescaler, 75 to 65,535 for 8/9 prescaler).

MOD is the preset fractional modulus (2 to 4095).

FRAC is the numerator of the fractional division (0 to MOD 1).

fPFD = REFIN × [(1 + D)/(R × (1 + T))]

(2)

where:

REFIN is the reference input frequency.

D is the REFIN doubler bit.

T is the REFIN divide-by-2 bit (0 or 1).

R is the preset divide ratio of the binary 10-bit programmable

reference counter (1 to 1023).

THIRD-ORDER

FRACTIONAL

INTERPOLATOR

FRAC

VALUE

MOD

REG

INT

REG

RF N DIVIDER

N = INT + FRAC/MOD

FROM

VCO OUTPUT/

OUTPUT DIVIDERS

TO PFD

N COUNTER

0

732

5-

0

06

Figure 17. RF INT Divider

INT N MODE

If the FRAC = 0 and DB8 in Register 2 (LDF) is set to 1, the

synthesizer operates in integer-N mode. The DB8 in Register 2

(LDF) should be set to 1 to get integer-N digital lock detect.

R COUNTER

The 10–bit R counter allows the input reference frequency

(REFIN) to be divided down to produce the reference clock

to the PFD. Division ratios from 1 to 1023 are allowed.

PHASE FREQUENCY DETECTOR (PFD) AND

CHARGE PUMP

The phase frequency detector (PFD) takes inputs from the

R counter and N counter and produces an output proportional

to the phase and frequency difference between them. Figure 18

is a simplified schematic of the phase frequency detector. The

PFD includes a fixed delay element that sets the width of the

antibacklash pulse, which is typically 3 ns. This pulse ensures

there is no dead zone in the PFD transfer function, and gives a

consistent reference spur level.

U3

CLR2

Q2

D2

U2

DOWN

UP

HIGH

CP

–IN

N

CHARGE

PUMP

DELAY

CLR1

Q1

D1

U1

07

32

5-

00

7

+I

Figure 18. PFD Simplified Schematic

相关PDF资料 |

PDF描述 |

|---|---|

| SY100E457JZ | IC MUX TRIPLE DIFF 2:1 28-PLCC |

| SY100E164JZ | IC MULTIPLEXER 16:1 28-PLCC |

| X9317US8IZ-2.7 | IC XDCP 100TAP 50K 3-WIRE 8-SOIC |

| SY58030UMG TR | IC MUX DIFF LVPECL 4:1 32-MLF |

| VE-JVY-MZ-S | CONVERTER MOD DC/DC 3.3V 16.5W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADF4350BCPZ-U6 | 制造商:Analog Devices 功能描述: |

| ADF4350EB1Z | 制造商:Analog Devices 功能描述:AD EVAL BOARD - Bulk |

| ADF4351 | 制造商:AD 制造商全称:Analog Devices 功能描述:Wideband Synthesizer |

| ADF4351BCPZ | 功能描述:IC SYNTH PLL VCO 32LFCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:2,000 系列:- 类型:PLL 时钟发生器 PLL:带旁路 输入:LVCMOS,LVPECL 输出:LVCMOS 电路数:1 比率 - 输入:输出:2:11 差分 - 输入:输出:是/无 频率 - 最大:240MHz 除法器/乘法器:是/无 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:32-LQFP 供应商设备封装:32-TQFP(7x7) 包装:带卷 (TR) |

| ADF4351BCPZ-RL7 | 功能描述:IC SYNTH PLL VCO 32LFCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:2,000 系列:- 类型:PLL 时钟发生器 PLL:带旁路 输入:LVCMOS,LVPECL 输出:LVCMOS 电路数:1 比率 - 输入:输出:2:11 差分 - 输入:输出:是/无 频率 - 最大:240MHz 除法器/乘法器:是/无 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:32-LQFP 供应商设备封装:32-TQFP(7x7) 包装:带卷 (TR) |

发布紧急采购,3分钟左右您将得到回复。