- 您现在的位置:买卖IC网 > PDF目录16743 > ADP1043AACPZ-R7 (Analog Devices Inc)IC THERMO COOLER CTLR 32LFCSP PDF资料下载

参数资料

| 型号: | ADP1043AACPZ-R7 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 37/72页 |

| 文件大小: | 0K |

| 描述: | IC THERMO COOLER CTLR 32LFCSP |

| 标准包装: | 1,500 |

| 应用: | 电源 |

| 输入电压: | 0 V ~ 1.55 V |

| 电源电压: | 3.1 V ~ 3.6 V |

| 电流 - 电源: | 20mA |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 32-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 32-LFCSP-VQ(5x5) |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页当前第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页

�� �

�

�

�ADP1043A�

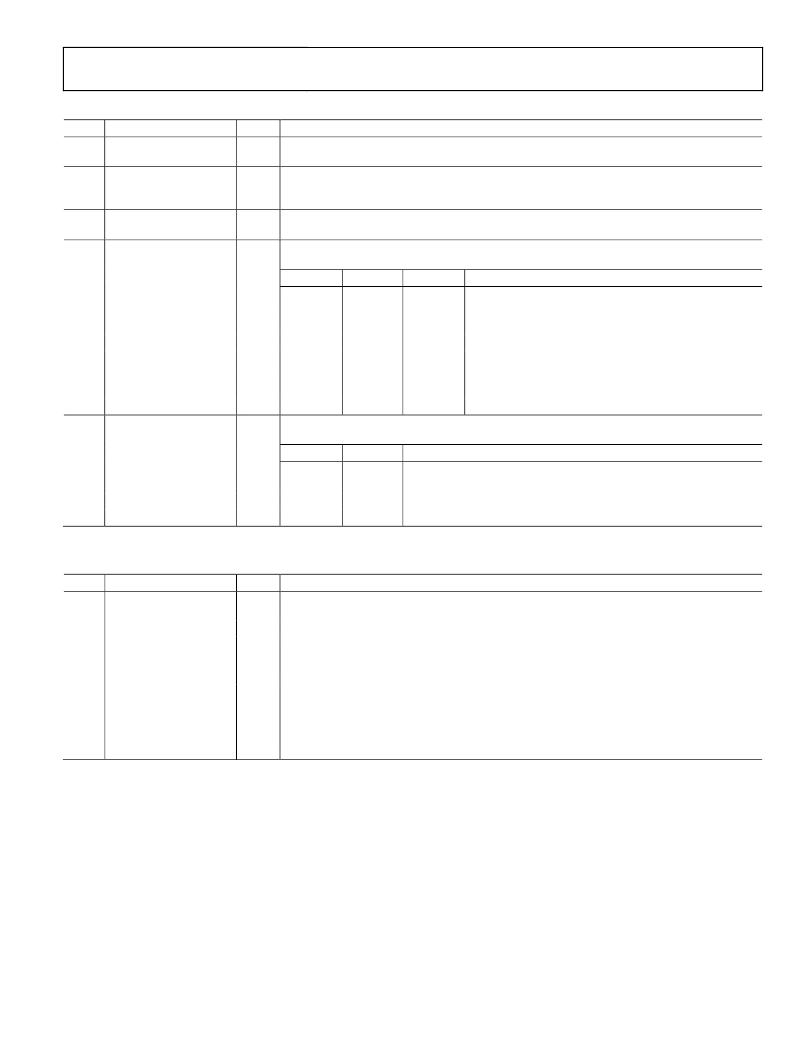

�Table� 14.� Register� 0x0E—Flag� Configuration� Register�

�Bits�

�7�

�Name�

�VDD� OV/VCORE� OV�

�R/W�

�R/W�

�Description�

�Setting� this� bit� means� that� the� VDD� OV� and� VCORE� OV� flags� are� ignored.�

�flags� ignore�

�6�

�VDD� OV/VCORE� OV�

�restart�

�R/W�

�Setting� this� bit� to� 1� means� that� if� the� part� shuts� down,� it� will� download� the� EEPROM� contents�

�again� before� restarting.� Setting� this� bit� to� 0� means� that� if� the� part� shuts� down,� it� will� not�

�download� the� EEPROM� contents� again� before� restarting.�

�5�

�[4:2]�

�VDD� OV/VCORE� OV�

�debounce�

�Accurate� OCP� off� delay�

�for� CS1� and� CS2�

�R/W�

�R/W�

�Setting� this� bit� to� 1� means� that� there� is� a� 500� μs� debounce� before� the� part� shuts� down.� Setting�

�this� bit� to� 0� means� that� there� is� a� 2� μs� debounce� before� the� part� shuts� down.�

�When� an� accurate� OCP� flag� is� set,� there� is� a� delay� before� the� corresponding� action� is� performed.�

�This� delay� is� programmed� using� these� bits.�

�Bit� 4�

�0�

�0�

�0�

�0�

�1�

�1�

�1�

�1�

�Bit� 3�

�0�

�0�

�1�

�1�

�0�

�0�

�1�

�1�

�Bit� 2�

�0�

�1�

�0�

�1�

�0�

�1�

�0�

�1�

�Debounce�

�1.3� ms�

�13� ms�

�130� ms�

�260� ms�

�600� ms�

�1.3� sec�

�2� sec�

�2.6� sec�

�[1:0]�

�Power� supply� reenable�

�time�

�R/W�

�These� bits� specify� the� time� delay� before� restarting� the� power� supply� after� a� shutdown.�

�SR1,� SR2,� and� OrFET� are� reenabled� immediately.�

�Bit� 1�

�Bit� 0�

�Time� (sec)�

�0�

�0�

�0.5�

�0�

�1�

�1�

�1�

�0�

�2�

�1�

�1�

�4�

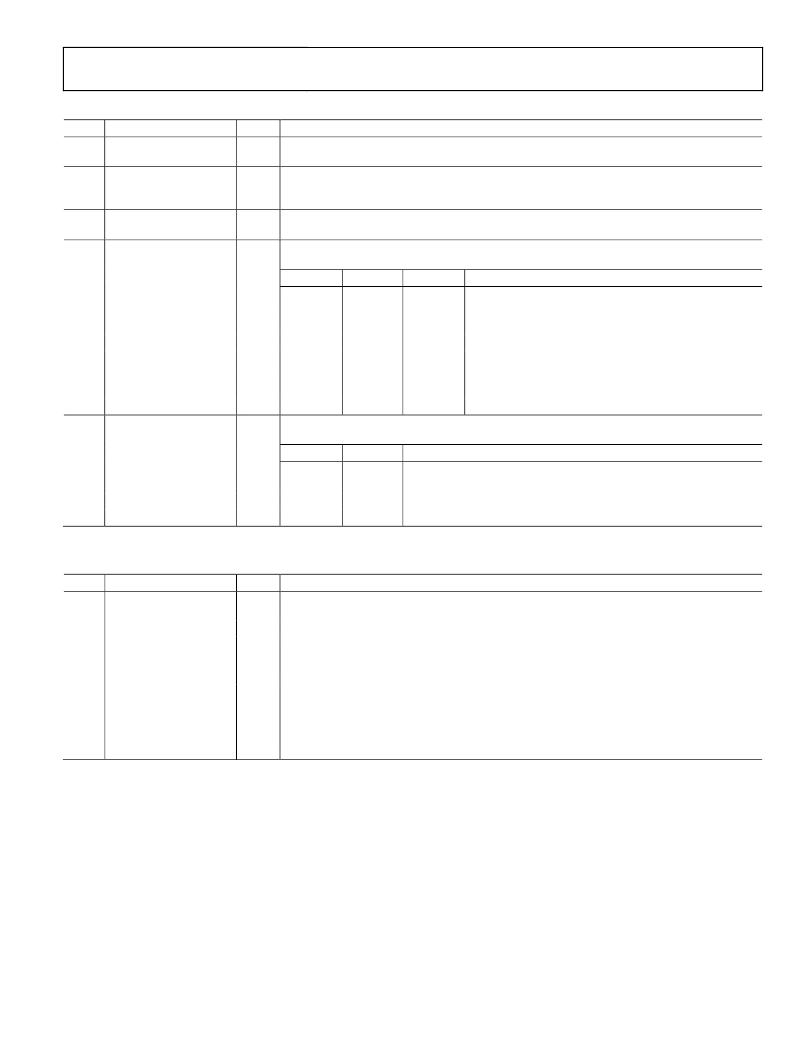

�Table 15. Register 0x0F—Soft Start Blan� k� Fault� Flags� Register�

�Bits�

�7�

�Name�

�Blank� SR�

�R/W�

�R/W�

�Description�

�Setting� this� bit� means� that� the� SR1� and� SR2� PWM� outputs� are� not� enabled� until� the� end� of� the�

�soft� start� ramp� time.�

�6�

�5�

�4�

�3�

�2�

�Blank� OTP�

�Blank� FLAGIN�

�Blank� local� OVP�

�Blank� load� OVP�

�Blank� CS2� accurate� OCP�

�R/W�

�R/W�

�R/W�

�R/W�

�R/W�

�Setting� this� bit� means� that� the� OTP� flag� is� ignored� until� the� end� of� the� soft� start� ramp� time.�

�Setting� this� bit� means� that� the� FLAGIN� flag� is� ignored� until� the� end� of� the� soft� start� ramp� time.�

�Setting� this� bit� means� that� the� local� OVP� flag� is� ignored� until� the� end� of� the� soft� start� ramp� time.�

�Setting� this� bit� means� that� the� load� OVP� flag� is� ignored� until� the� end� of� the� soft� start� ramp� time.�

�Setting� this� bit� means� that� the� CS2� accurate� OCP� flag� is� ignored� until� the� end� of� the� soft� start�

�ramp� time.�

�1�

�Blank� CS1� accurate� OCP�

�R/W�

�Setting� this� bit� means� that� the� CS1� accurate� OCP� flag� is� ignored� until� the� end� of� the� soft� start�

�ramp� time.�

�0�

�Blank� CS1� fast� OCP�

�R/W�

�Setting� this� bit� means� that� the� CS1� fast� OCP� flag� is� ignored� until� the� end� of� the� soft� start� ramp� time.�

�Rev.� 0� |� Page� 37� of� 72�

�相关PDF资料 |

PDF描述 |

|---|---|

| RBC13DRTH-S93 | CONN EDGECARD 26POS .100 EXTEND |

| H6PPH-2406M | DIP CABLE - HDP24H/AE24M/HDP24H |

| GBC18DRTS-S93 | CONN EDGECARD 36POS DIP .100 SLD |

| 6.3TZV220M6.3X6.1 | CAP ALUM 220UF 6.3V 20% SMD |

| H0PPS-2418G | DIP CABLE - HDP24S/AE24G/HDP24S |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADP1043AACPZ-RL | 功能描述:IC SECONDARY SIDE CTRLR 32LFCSP RoHS:是 类别:集成电路 (IC) >> PMIC - 电源控制器,监视器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 应用:多相控制器 输入电压:- 电源电压:9 V ~ 14 V 电流 - 电源:- 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:40-WFQFN 裸露焊盘 供应商设备封装:40-TQFN-EP(5x5) 包装:带卷 (TR) |

| ADP1043ACPZ | 制造商:Analog Devices 功能描述:DC DC CNTRLR QUINT-OUT W/PWM 3.3V 32LFCSP EP - Trays |

| ADP1043ACPZ-RL | 制造商:Analog Devices 功能描述:DC DC CNTRLR QUINT-OUT W/PWM 3.3V 32LFCSP EP - Tape and Reel |

| ADP1043ADC1-EVALZ | 功能描述:BOARD EVAL ADP1043A DAUGHTERCARD RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 标准包装:1 系列:- 主要目的:电信,线路接口单元(LIU) 嵌入式:- 已用 IC / 零件:IDT82V2081 主要属性:T1/J1/E1 LIU 次要属性:- 已供物品:板,电源,线缆,CD 其它名称:82EBV2081 |

| ADP1043AFB100EVALZ | 功能描述:BOARD EVALUATION ADP1043A 100W RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 标准包装:1 系列:- 主要目的:电信,线路接口单元(LIU) 嵌入式:- 已用 IC / 零件:IDT82V2081 主要属性:T1/J1/E1 LIU 次要属性:- 已供物品:板,电源,线缆,CD 其它名称:82EBV2081 |

发布紧急采购,3分钟左右您将得到回复。