- 您现在的位置:买卖IC网 > PDF目录1776 > ADP1740ACPZ-1.1-R7 (Analog Devices Inc)IC REG LDO 1.1V 2A 16LFCSP PDF资料下载

参数资料

| 型号: | ADP1740ACPZ-1.1-R7 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 4/20页 |

| 文件大小: | 0K |

| 描述: | IC REG LDO 1.1V 2A 16LFCSP |

| 标准包装: | 1 |

| 稳压器拓扑结构: | 正,固定式 |

| 输出电压: | 1.1V |

| 输入电压: | 1.6 V ~ 3.6 V |

| 稳压器数量: | 1 |

| 电流 - 输出: | 2A(最小值) |

| 电流 - 限制(最小): | 2.4A |

| 工作温度: | -40°C ~ 125°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 16-VQFN 裸露焊盘,CSP |

| 供应商设备封装: | 16-LFCSP-VQ EP(4x4) |

| 包装: | 标准包装 |

| 产品目录页面: | 794 (CN2011-ZH PDF) |

| 其它名称: | ADP1740ACPZ-1.1-R7DKR |

�� �

�

�

�ADP1740/ADP1741�

�Data� Sheet�

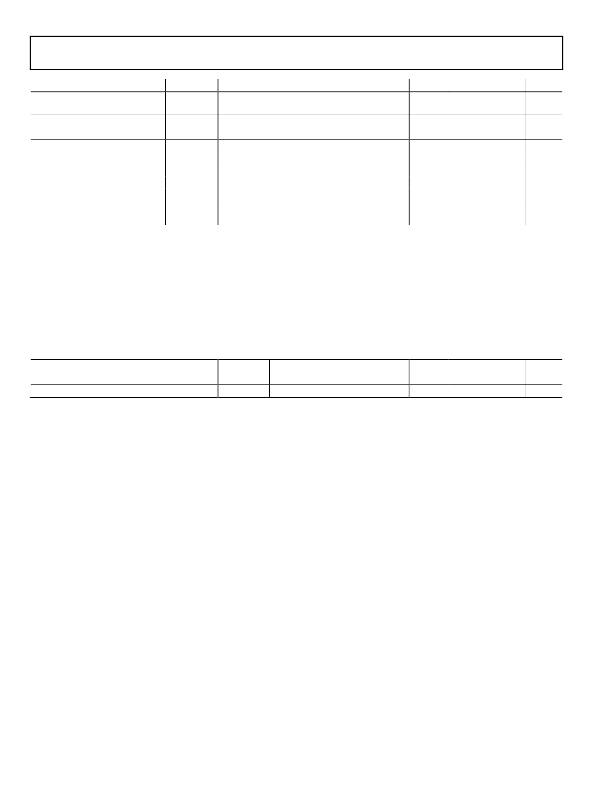

�Parameter�

�SENSE� INPUT� BIAS� CURRENT�

�Symbol�

�SNS� I-BIAS�

�Test� Conditions/Comments�

�1.6� V� ≤� V� IN� ≤� 3.6� V�

�Min�

�Typ�

�10�

�Max�

�Unit�

�μA�

�(ADP1740)�

�OUTPUT� NOISE�

�POWER� SUPPLY� REJECTION� RATIO�

�OUT� NOISE�

�PSRR�

�10� Hz� to� 100� kHz,� V� OUT� =� 0.75� V�

�10� Hz� to� 100� kHz,� V� OUT� =� 2.5� V�

�V� IN� =� V� OUT� +� 1� V,� I� OUT� =� 10� mA�

�1� kHz,� V� OUT� =� 0.75� V�

�1� kHz,� V� OUT� =� 2.5� V�

�10� kHz,� V� OUT� =� 0.75� V�

�10� kHz,� V� OUT� =� 2.5� V�

�100� kHz,� V� OUT� =� 0.75� V�

�100� kHz,� V� OUT� =� 2.5� V�

�23�

�65�

�65�

�56�

�65�

�56�

�54�

�51�

�μV� rms�

�μV� rms�

�dB�

�dB�

�dB�

�dB�

�dB�

�dB�

�1�

�2�

�3�

�4�

�5�

�6�

�Minimum� output� load� current� is� 500� μA.�

�Accuracy� when� VOUT� is� connected� directly� to� ADJ.� When� VOUT� voltage� is� set� by� external� feedback� resistors,� absolute� accuracy� in� adjust� mode� depends� on� the� tolerances�

�of� the� resistors� used.�

�Based� on� an� endpoint� calculation� using� 10� mA� and� 2� A� loads.� See� Figure� 6� for� typical� load� regulation� performance.�

�Dropout� voltage� is� defined� as� the� input� to� output� voltage� differential� when� the� input� voltage� is� set� to� the� nominal� output� voltage.� This� applies� only� to� output� voltages�

�above� 1.6� V.�

�Start-up� time� is� defined� as� the� time� between� the� rising� edge� of� EN� to� V� OUT� being� at� 95%� of� its� nominal� value.�

�Current-limit� threshold� is� defined� as� the� current� at� which� the� output� voltage� drops� to� 90%� of� the� specified� typical� value.� For� example,� the� current� limit� for� a� 1.0� V�

�output� voltage� is� defined� as� the� current� that� causes� the� output� voltage� to� drop� to� 90%� of� 1.0� V,� or� 0.9� V.�

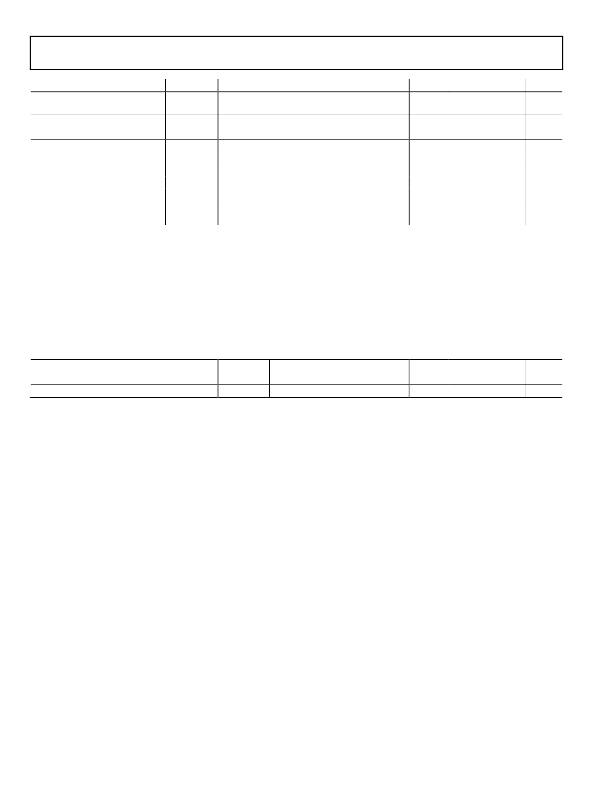

�INPUT� AND� OUTPUT� CAPACITOR,� RECOMMENDED� SPECIFICATIONS�

�Table� 2.�

�Parameter�

�MINIMUM� INPUT� AND� OUTPUT� CAPACITANCE� 1�

�CAPACITOR� ESR�

�Symbol�

�C� MIN�

�R� ESR�

�Test� Conditions/Comments�

�T� A� =� –40°C� to� +125°C�

�T� A� =� –40°C� to� +125°C�

�Min�

�3.3�

�0.001�

�Typ�

�Max�

�0.1�

�Unit�

�μF�

�?�

�1�

�The� minimum� input� and� output� capacitance� should� be� greater� than� 3.3� μF� over� the� full� range� of� operating� conditions.� The� full� range� of� operating� conditions� in� the�

�application� must� be� considered� during� capacitor� selection� to� ensure� that� the� minimum� capacitance� specification� is� met.� X7R� and� X5R� type� capacitors� are� recommended;�

�Y5V� and� Z5U� capacitors� are� not� recommended� for� use� with� this� LDO.�

�Rev.� F� |� Page� 4� of� 20�

�相关PDF资料 |

PDF描述 |

|---|---|

| ADP1752ACPZ-1.8-R7 | IC REG LDO 1.8V .8A 16LFCSP |

| ADP1754ACPZ-1.2-R7 | IC REG LDO 1.2V 1.2A 16LFCSP |

| ADP1821ARQZ-R7 | IC REG CTRLR BUCK PWM VM 16-QSOP |

| ADP1822ARQZ-R7 | IC REG CTRLR BUCK PWM VM 24-QSOP |

| ADP1823ACPZ-R7 | IC REG CTRLR BUCK PWM VM 32LFCSP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADP1740ACPZ-2.5-R7 | 功能描述:IC REG LDO 2.5V 2A 16LFCSP RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - 线性 系列:- 产品培训模块:MIC5365/66 Ultra-small LDO Regulators 标准包装:1 系列:- 稳压器拓扑结构:正,固定式 输出电压:3V 输入电压:最高 5.5V 电压 - 压降(标准):0.155V @ 150mA 稳压器数量:1 电流 - 输出:150mA 电流 - 限制(最小):200mA 工作温度:-40°C ~ 125°C 安装类型:表面贴装 封装/外壳:4-UDFN 裸露焊盘,4-TMLF? 供应商设备封装:4-TMLF?(1x1) 包装:Digi-Reel® 其它名称:576-3192-6 |

| ADP1740-BL1-EVZ | 制造商:Analog Devices 功能描述:Evaluation Board For Low Dropout Linear Regulator 制造商:Analog Devices 功能描述:BLANK ADISIMPOWER EVAL ADP1740 - Boxed Product (Development Kits) |

| ADP1741 | 制造商:AD 制造商全称:Analog Devices 功能描述:2 A, Low Dropout, CMOS Linear Regulator |

| ADP1741ACPZ-R7 | 功能描述:IC REG LDO ADJ 2A 16LFCSP RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - 线性 系列:- 产品培训模块:MIC5365/66 Ultra-small LDO Regulators 标准包装:1 系列:- 稳压器拓扑结构:正,固定式 输出电压:3V 输入电压:最高 5.5V 电压 - 压降(标准):0.155V @ 150mA 稳压器数量:1 电流 - 输出:150mA 电流 - 限制(最小):200mA 工作温度:-40°C ~ 125°C 安装类型:表面贴装 封装/外壳:4-UDFN 裸露焊盘,4-TMLF? 供应商设备封装:4-TMLF?(1x1) 包装:Digi-Reel® 其它名称:576-3192-6 |

| ADP1741-EVALZ | 功能描述:BOARD EVAL 2A ADP1741 RoHS:是 类别:编程器,开发系统 >> 评估板 - 线性稳压器 (LDO) 系列:- 产品变化通告:1Q2012 Discontinuation 30/Mar/2012 设计资源:NCP590MNDPTAGEVB Gerber Files 标准包装:1 系列:- 每 IC 通道数:2 - 双 输出电压:1.8V,2.8V 电流 - 输出:300mA 输入电压:2.1 ~ 5.5 V 稳压器类型:正,固定式 工作温度:-40°C ~ 85°C 板类型:完全填充 已供物品:板 已用 IC / 零件:NCP590MNDP 其它名称:NCP590MNDPTAGEVB-NDNCP590MNDPTAGEVBOS |

发布紧急采购,3分钟左右您将得到回复。