- 您现在的位置:买卖IC网 > PDF目录19395 > ADSP-BF524KBCZ-4 (Analog Devices Inc)IC DSP CTRLR 400MHZ 289CSPBGA PDF资料下载

参数资料

| 型号: | ADSP-BF524KBCZ-4 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 59/88页 |

| 文件大小: | 0K |

| 描述: | IC DSP CTRLR 400MHZ 289CSPBGA |

| 标准包装: | 1 |

| 系列: | Blackfin® |

| 类型: | 定点 |

| 接口: | DMA,I²C,PPI,SPI,SPORT,UART,USB |

| 时钟速率: | 400MHz |

| 非易失内存: | ROM(32 kB) |

| 芯片上RAM: | 132kB |

| 电压 - 输入/输出: | 1.8V,2.5V,3.3V |

| 电压 - 核心: | 1.30V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 289-LFBGA,CSPBGA |

| 供应商设备封装: | 289-CSPBGA(12x12) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页当前第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页

�� �

�

�

�ADSP-BF522/ADSP-BF523/ADSP-BF524/ADSP-BF525/ADSP-BF526/ADSP-BF527�

�Serial� Peripheral� Interface� (SPI)� Port—Slave� Timing�

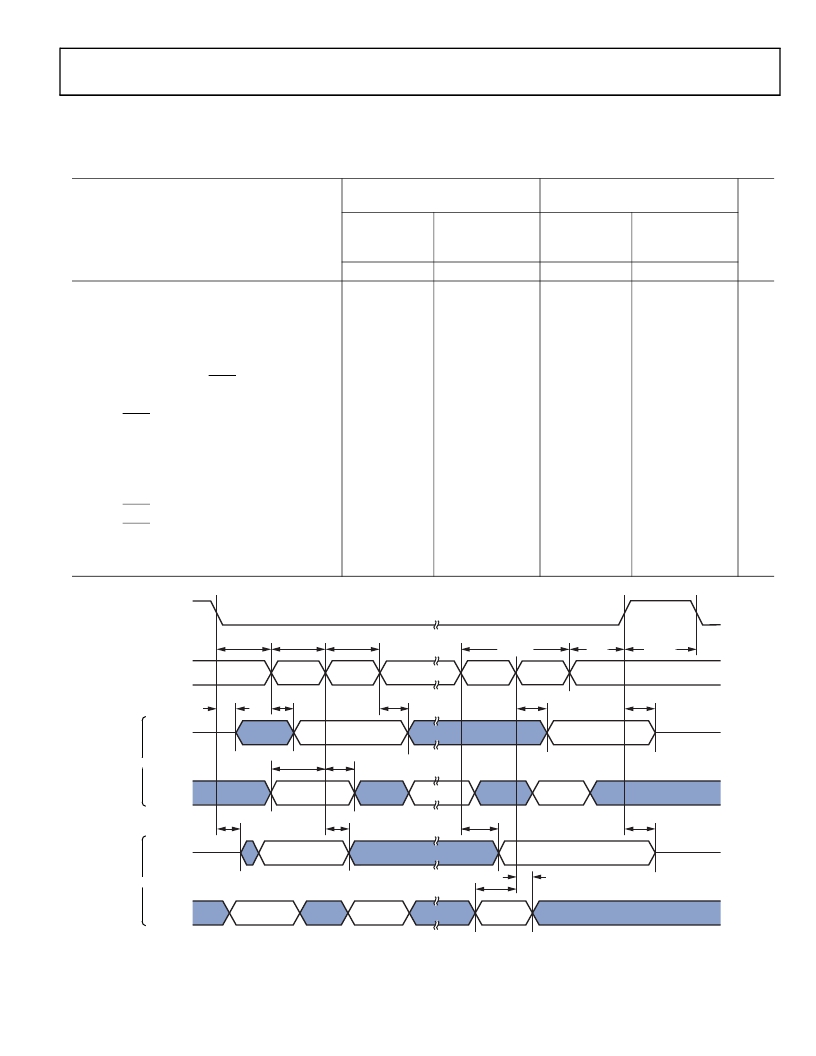

��Table� 49.� Serial� Peripheral� Interface� (SPI)� Port—Slave� Timing�

�ADSP-BF522/ADSP-BF524/�

�ADSP-BF526�

�V� DDEXT�

�ADSP-BF523/ADSP-BF525/�

�ADSP-BF527�

�V� DDEXT�

�V� DDEXT�

�1.8V� Nominal�

�2.5� V� or� 3.3V�

�Nominal�

�V� DDEXT�

�1.8V� Nominal�

�2.5� V� or� 3.3V�

�Nominal�

�Parameter�

�Min�

�Max� Min�

�Max� Min�

�Max� Min�

�Max� Unit�

�Timing� Requirements�

�t� SPICHS�

�t� SPICLS�

�t� SPICLK�

�Serial� Clock� High� Period�

�Serial� Clock� Low� Period�

�Serial� Clock� Period�

�2� ×� t� SCLK� –1.5�

�2� ×� t� SCLK� –1.5�

�4�

�2� ×� t� SCLK� –1.5�

�2� ×� t� SCLK� –1.5�

�4� ×� t� SCLK� –1.5�

�2� ×� t� SCLK� –1.5�

�2� ×� t� SCLK� –1.5�

�4�

�2� ×� t� SCLK� –1.5�

�2� ×� t� SCLK� –1.5�

�4� ×� t� SCLK� –1.5�

�ns�

�ns�

�ns�

�t� SCLK� –1.5�

�t� SCLK� –1.5�

�t� HDS�

�t� SPITDS�

�t� SDSCI�

�t� SSPID�

�Last� SCK� Edge� to� SPISS� Not� Asserted�

�Sequential� Transfer� Delay�

�SPISS� Assertion� to� First� SCK� Edge�

�Data� Input� Valid� to� SCK� Edge� (Data� Input�

�2� ×� t� SCLK� –1.5�

�2� ×� t� SCLK� –1.5�

�2� ×� t� SCLK� –1.5�

�1.6�

�2� ×� t� SCLK� –1.5�

�2� ×� t� SCLK� –1.5�

�2� ×� t� SCLK� –1.5�

�1.6�

�2� ×� t� SCLK� –1.5�

�2� ×� t� SCLK� –1.5�

�2� ×� t� SCLK� –1.5�

�1.6�

�2� ×� t� SCLK� –1.5�

�2� ×� t� SCLK� –1.5�

�2� ×� t� SCLK� –1.5�

�1.6�

�ns�

�ns�

�ns�

�ns�

�Setup)�

�t� HSPID�

�SCK� Sampling� Edge� to� Data� Input� Invalid�

�2.0�

�1.6�

�1.6�

�1.6�

�ns�

�Switching� Characteristics�

�t� DSOE�

�SPISS� Assertion� to� Data� Out� Active�

�0�

�12.0� 0�

�10.3�

�0�

�12.0� 0�

�10.3�

�ns�

�t� DSDHI�

�t� DDSPID�

�SPISS� Deassertion� to� Data� High� Impedance� 0�

�SCK� Edge� to� Data� Out� Valid� (Data� Out� Delay)�

�11.0� 0�

�10�

�8.5�

�10�

�0�

�8.5�

�10�

�0�

�8�

�10�

�ns�

�ns�

�t� HDSPID�

�SCK� Edge� to� Data� Out� Invalid� (Data� Out� Hold)� 0�

�0�

�0�

�0�

�ns�

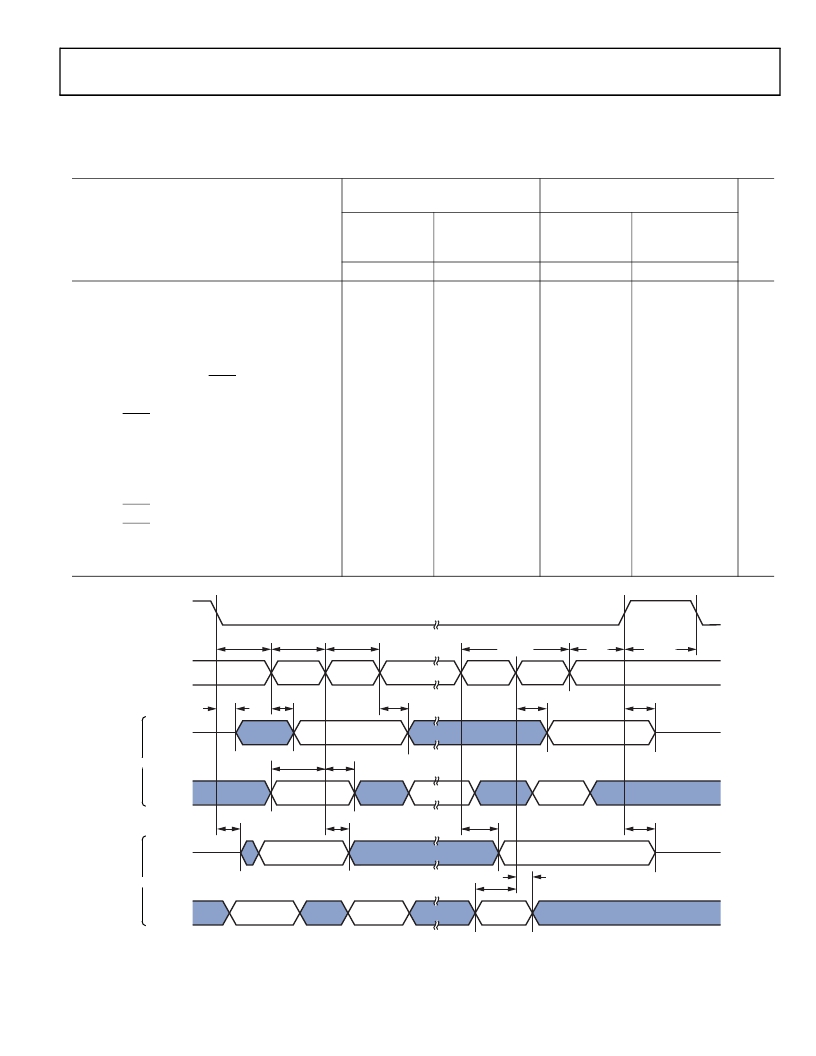

�SPIxSS�

�(INPUT)�

�t� SDSCI�

�t� SPICLS�

�t� SPICHS�

�t� SPICLK�

�t� HDS�

�t� SPITDS�

�SPIxSCK�

�(INPUT)�

�t� DSOE�

�t� DDSPID�

�t� HDSPID�

�t� DDSPID�

�t� DSDHI�

�SPIxMISO�

�(OUTPUT)�

�CPHA� =� 1�

�SPIxMOSI�

�(INPUT)�

�t� SSPID�

�t� HSPID�

�t� DSOE�

�t� HDSPID�

�t� DDSPID�

�t� DSDHI�

�SPIxMISO�

�(OUTPUT)�

�CPHA� =� 0�

�t� SSPID�

�t� HSPID�

�SPIxMOSI�

�(INPUT)�

�Figure� 29.� Serial� Peripheral� Interface� (SPI)� Port—Slave� Timing�

�Rev.� D� |�

�Page� 59� of� 88� |� July� 2013�

�相关PDF资料 |

PDF描述 |

|---|---|

| VI-23R-CY-F3 | CONVERTER MOD DC/DC 7.5V 50W |

| RW2-243.3D/H3 | CONV DC/DC 2W 18-36VIN +/-3.3V |

| VI-23P-CY-F3 | CONVERTER MOD DC/DC 13.8V 50W |

| RW2-243.3D/H2/SMD | CONV DC/DC 2W 18-36VIN +/-3.3V |

| RW2-2415D/H3 | CONV DC/DC 2W 18-36VIN +/-15VOUT |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADSP-BF524KBCZ-4AX | 制造商:Analog Devices 功能描述: |

| ADSP-BF524KBCZ-4C2 | 功能描述:IC DSP CTRLR 400MHZ 289CSPBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:Blackfin® 标准包装:2 系列:StarCore 类型:SC140 内核 接口:DSI,以太网,RS-232 时钟速率:400MHz 非易失内存:外部 芯片上RAM:1.436MB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:431-BFBGA,FCBGA 供应商设备封装:431-FCPBGA(20x20) 包装:托盘 |

| ADSP-BF525 | 制造商:Analog Devices 功能描述: |

| ADSP-BF525ABCZ-5 | 功能描述:数字信号处理器和控制器 - DSP, DSC ADSP-BF525 Processor 533Mhz Ethernet USB RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT |

| ADSP-BF525ABCZ-6 | 功能描述:数字信号处理器和控制器 - DSP, DSC ADSP-BF525 Processor 600Mhz Ethernet USB RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT |

发布紧急采购,3分钟左右您将得到回复。