- 您现在的位置:买卖IC网 > PDF目录19504 > ADSP-BF527KBCZ-6A (Analog Devices Inc)IC DSP 16BIT 600MHZ 208CSPBGA PDF资料下载

参数资料

| 型号: | ADSP-BF527KBCZ-6A |

| 厂商: | Analog Devices Inc |

| 文件页数: | 14/88页 |

| 文件大小: | 0K |

| 描述: | IC DSP 16BIT 600MHZ 208CSPBGA |

| 产品变化通告: | Datasheet Specification Change 14/Dec/2009 |

| 标准包装: | 1 |

| 系列: | Blackfin® |

| 类型: | 定点 |

| 接口: | DMA,以太网,I²C,PPI,SPI,SPORT,UART,USB |

| 时钟速率: | 600MHz |

| 非易失内存: | ROM(32 kB) |

| 芯片上RAM: | 132kB |

| 电压 - 输入/输出: | 1.8V,2.5V,3.3V |

| 电压 - 核心: | 1.10V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 208-LFBGA,CSPBGA |

| 供应商设备封装: | 208-CSPBGA |

| 包装: | 托盘 |

| 配用: | EVAL-SDP-CB1Z-ND - BOARD EVALUATION FOR SDP-CB1 ADZS-BF527-MPSKIT-ND - BOARD EVAL MEDIA PLAYER BF527 ADZS-BF527-EZLITE-ND - BOARD EVAL ADSP-BF527 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页当前第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页

�� �

�

�

�ADSP-BF522/ADSP-BF523/ADSP-BF524/ADSP-BF525/ADSP-BF526/ADSP-BF527�

�Entire� Field� Mode�

�In� this� mode,� the� entire� incoming� bit� stream� is� read� in� through�

�the� PPI.� This� includes� active� video,� control� preamble� sequences,�

�and� ancillary� data� that� may� be� embedded� in� horizontal� and� ver-�

�tical� blanking� intervals.� Data� transfer� starts� immediately� after�

�synchronization� to� Field� 1.� Data� is� transferred� to� or� from� the�

�synchronous� channels� through� eight� DMA� engines� that� work�

�autonomously� from� the� processor� core.�

�USB� ON-THE-GO� DUAL-ROLE� DEVICE� CONTROLLER�

�The� USB� OTG� dual-role� device� controller� (USBDRC)� provides�

�DYNAMIC� POWER� MANAGEMENT�

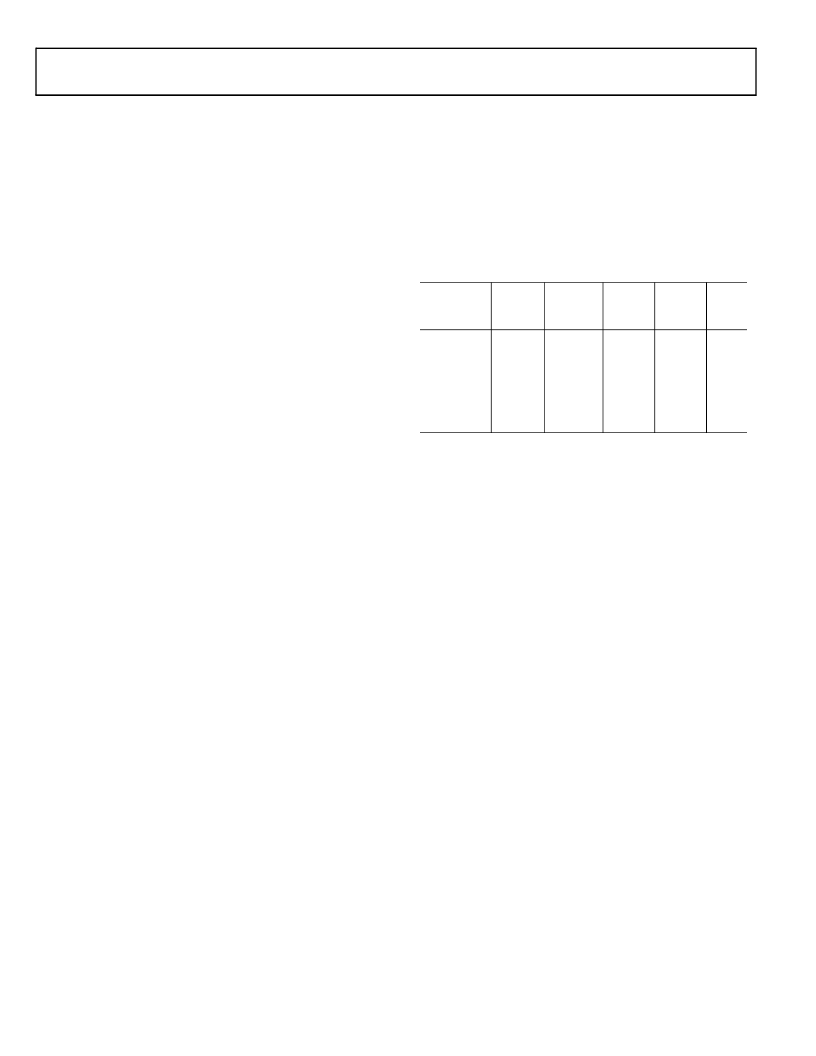

�The� processor� provides� five� operating� modes,� each� with� a� differ-�

�ent� performance/power� profile.� In� addition,� dynamic� power�

�management� provides� the� control� functions� to� dynamically� alter�

�the� processor� core� supply� voltage,� further� reducing� power� dissi-�

�pation.� When� configured� for� a� 0� V� core� supply� voltage,� the�

�processor� enters� the� hibernate� state.� Control� of� clocking� to� each�

�of� the� processor� peripherals� also� reduces� power� consumption.�

�See� Table� 4� for� a� summary� of� the� power� settings� for� each� mode.�

�Table� 4.� Power� Settings�

�a� low-cost� connectivity� solution� for� consumer� mobile� devices�

�such� as� cell� phones,� digital� still� cameras,� and� MP3� players,�

�allowing� these� devices� to� transfer� data� using� a� point-to-point�

�USB� connection� without� the� need� for� a� PC� host.� The� USBDRC�

�Mode/State� PLL�

�PLL�

�Bypassed�

�Core�

�Clock�

�(CCLK)�

�System�

�Clock�

�(SCLK)�

�Core�

�Power�

�module� can� operate� in� a� traditional� USB� peripheral-only� mode�

�as� well� as� the� host� mode� presented� in� the� On-the-Go� (OTG)�

�Full-On� Enabled� No�

�Active� Enabled/� Yes�

�Enabled�

�Enabled�

�Enabled�

�Enabled�

�On�

�On�

�supplement� to� the� USB� 2.0� specification.� In� host� mode,� the� USB�

�Disabled�

�module� supports� transfers� at� high� speed� (480� Mbps),� full� speed�

�(12� Mbps),� and� low� speed� (1.5� Mbps)� rates.� Peripheral-only�

�mode� supports� the� high-� and� full-speed� transfer� rates.�

�The� USB� clock� (USB_XI)� is� provided� through� a� dedicated� exter-�

�Sleep� Enabled� —�

�Deep� Sleep� Disabled� —�

�Hibernate� Disabled� —�

�Disabled� Enabled� On�

�Disabled� Disabled� On�

�Disabled� Disabled� Off�

���related� timing� requirements.� If� using� a� crystal� to� provide� the�

�USB� clock,� use� a� parallel-resonant,� fundamental� mode,� micro-�

�processor-grade� crystal.�

�The� USB� on-the-go� dual-role� device� controller� includes� a� phase�

�locked� loop� with� programmable� multipliers� to� generate� the� nec-�

�essary� internal� clocking� frequency� for� USB.� The� multiplier� value�

�should� be� programmed� based� on� the� USB_XI� frequency� to�

�achieve� the� necessary� 480� MHz� internal� clock� for� USB� high�

�speed� operation.� For� example,� for� a� USB_XI� crystal� frequency� of�

�24� MHz,� the� USB_PLLOSC_CTRL� register� should� be� pro-�

�grammed� with� a� multiplier� value� of� 20� to� generate� a� 480� MHz�

�internal� clock.�

�CODE� SECURITY� WITH� LOCKBOX� SECURE�

�TECHNOLOGY�

�A� security� system� consisting� of� a� blend� of� hardware� and� soft-�

�ware� provides� customers� with� a� flexible� and� rich� set� of� code�

�security� features� with� Lockbox� TM� Secure� Technology.� Key� fea-�

�tures� include:�

�?� OTP� memory�

�?� Unique� chip� ID�

�?� Code� authentication�

�?� Secure� mode� of� operation�

�The� security� scheme� is� based� upon� the� concept� of� authentica-�

�tion� of� digital� signatures� using� standards-based� algorithms� and�

�provides� a� secure� processing� environment� in� which� to� execute�

���Full-On� Operating� Mode—Maximum� Performance�

�In� the� full-on� mode,� the� PLL� is� enabled� and� is� not� bypassed,�

�providing� capability� for� maximum� operational� frequency.� This�

�is� the� power-up� default� execution� state� in� which� maximum� per-�

�formance� can� be� achieved.� The� processor� core� and� all� enabled�

�peripherals� run� at� full� speed.�

�Active� Operating� Mode—Moderate� Dynamic� Power�

�Savings�

�In� the� active� mode,� the� PLL� is� enabled� but� bypassed.� Because� the�

�PLL� is� bypassed,� the� processor’s� core� clock� (CCLK)� and� system�

�clock� (SCLK)� run� at� the� input� clock� (CLKIN)� frequency.� DMA�

�access� is� available� to� appropriately� configured� L1� memories.�

�In� the� active� mode,� it� is� possible� to� disable� the� control� input� to�

�the� PLL� by� setting� the� PLL_OFF� bit� in� the� PLL� control� register.�

�This� register� can� be� accessed� with� a� user-callable� routine� in� the�

�on-chip� ROM� called� bfrom_SysControl().� If� disabled,� the� PLL�

�control� input� must� be� re-enabled� before� transitioning� to� the�

�full-on� or� sleep� modes.�

�For� more� information� about� PLL� controls,� see� the� “Dynamic�

�Power� Management”� chapter� in� the� ADSP-BF52x� Blackfin� Pro-�

�cessor� Hardware� Reference.�

�Sleep� Operating� Mode—High� Dynamic� Power� Savings�

�The� sleep� mode� reduces� dynamic� power� dissipation� by� disabling�

�the� clock� to� the� processor� core� (CCLK).� The� PLL� and� system�

�clock� (SCLK),� however,� continue� to� operate� in� this� mode.� Typi-�

�cally,� an� external� event� or� RTC� activity� wakes� up� the� processor.�

�When� in� the� sleep� mode,� asserting� a� wakeup� enabled� in� the�

�SIC_IWRx� registers� causes� the� processor� to� sense� the� value� of�

�the� BYPASS� bit� in� the� PLL� control� register� (PLL_CTL).� If�

�BYPASS� is� disabled,� the� processor� transitions� to� the� full-on�

�mode.� If� BYPASS� is� enabled,� the� processor� transitions� to� the�

�active� mode.�

�Rev.� D�

�|�

�Page� 14� of� 88� |� July� 2013�

�相关PDF资料 |

PDF描述 |

|---|---|

| TAJB106K020H | CAP TANT 10UF 20V 10% 1210 |

| XC9536XL-7VQ44I | IC CPLD 36MCELL 7.5NS 44VQFP |

| GA355DR7GB223KY02L | CAP CER 0.022UF 250V 10% 2220 |

| ADP3338AKC-2.85-R7 | IC REG LDO 2.85V 1A SOT-223 |

| ADSP-BF525KBCZ-6A | IC DSP 16BIT 600MHZ 208CSPBGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADSP-BF527KBCZ-6AX | 制造商:Analog Devices 功能描述:- Trays |

| ADSP-BF527KBCZ6C1X | 制造商:Analog Devices 功能描述:- Trays |

| ADSP-BF527KBCZ-6C2 | 功能描述:IC DSP 16BIT 600MHZ 289CSPBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:Blackfin® 标准包装:40 系列:TMS320DM64x, DaVinci™ 类型:定点 接口:I²C,McASP,McBSP 时钟速率:400MHz 非易失内存:外部 芯片上RAM:160kB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:0°C ~ 90°C 安装类型:表面贴装 封装/外壳:548-BBGA,FCBGA 供应商设备封装:548-FCBGA(27x27) 包装:托盘 配用:TMDSDMK642-0E-ND - DEVELPER KIT W/NTSC CAMERA296-23038-ND - DSP STARTER KIT FOR TMS320C6416296-23059-ND - FLASHBURN PORTING KIT296-23058-ND - EVAL MODULE FOR DM642TMDSDMK642-ND - DEVELOPER KIT W/NTSC CAMERA |

| ADSP-BF527KBCZ6C2X | 制造商:Analog Devices 功能描述: |

| ADSP-BF527KBCZ-6X | 制造商:Analog Devices 功能描述:DSP 32-Bit 600MHz 208-Pin CSP-BGA 制造商:Analog Devices 功能描述:- Trays |

发布紧急采购,3分钟左右您将得到回复。