参数资料

| 型号: | ADV7391BCPZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 98/108页 |

| 文件大小: | 0K |

| 描述: | IC ENCODER VIDEO W/DAC 32LFCSP |

| 产品变化通告: | ADV734x, ADV739x Feature Improvement |

| 标准包装: | 1 |

| 类型: | 视频编码器 |

| 应用: | 机顶盒,视频播放器,显示器 |

| 电压 - 电源,模拟: | 2.6 V ~ 3.46 V |

| 电压 - 电源,数字: | 1.71 V ~ 1.89 V |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 32-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 32-LFCSP-VQ(5x5) |

| 包装: | 托盘 |

| 配用: | EVAL-ADV7391EBZ-ND - BOARD EVAL FOR ADV7391 ENCODER |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页当前第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页

Data Sheet

ADV7390/ADV7391/ADV7392/ADV7393

Rev. G | Page 9 of 108

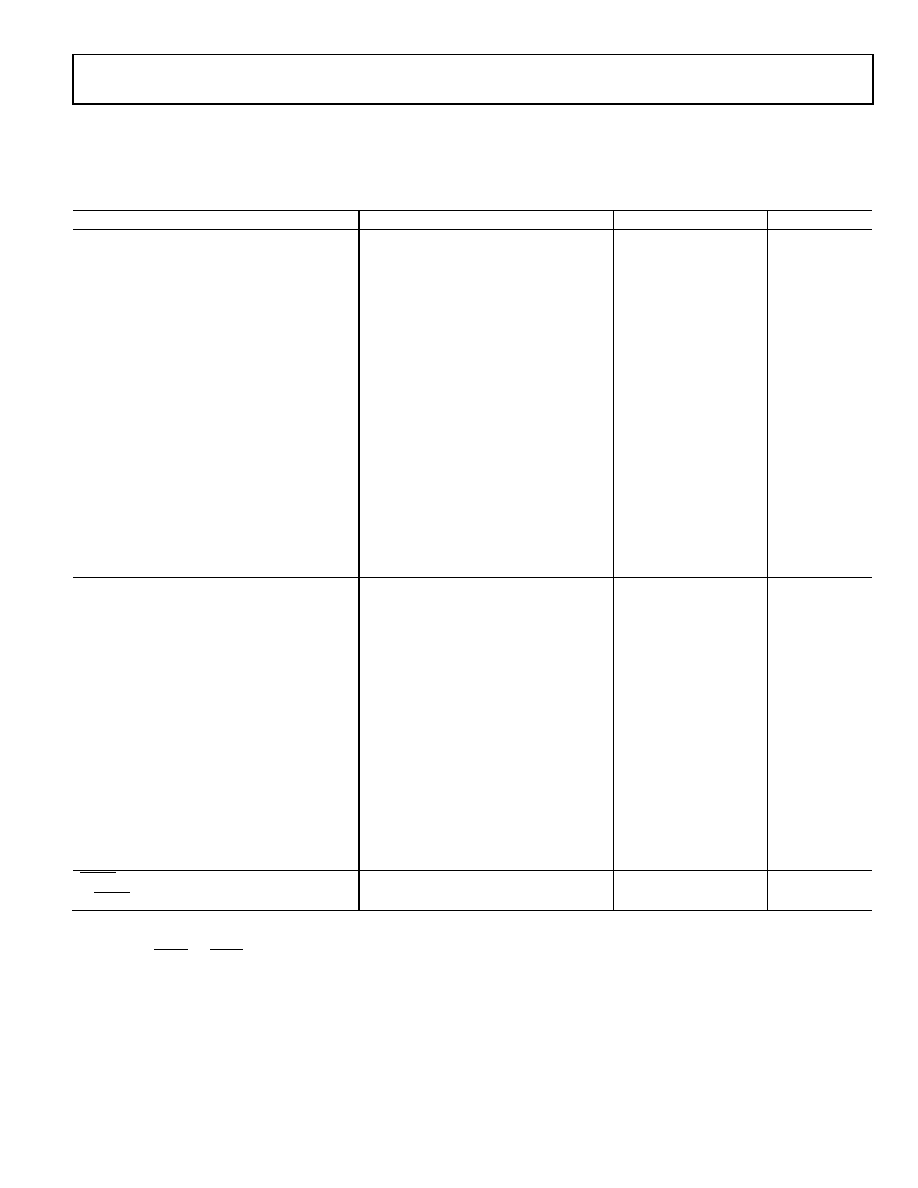

DIGITAL TIMING SPECIFICATIONS—3.3 V

VDD = 1.71 V to 1.89 V, PVDD = 1.71 V to 1.89 V, VAA = 2.6 V to 3.465 V, VDD_IO = 2.97 V to 3.63 V.

All specifications TMIN to TMAX (40°C to +85°C), unless otherwise noted.

Table 9.

Parameter

Min

Typ

Max

Unit

SD

2.1

ns

ED/HD-SDR

2.3

ns

ED/HD-DDR

2.3

ns

ED (at 54 MHz)

1.7

ns

Data Input Hold Time, t124

SD

1.0

ns

ED/HD-SDR

1.1

ns

ED/HD-DDR

1.1

ns

ED (at 54 MHz)

1.0

ns

Control Input Setup Time, t114

SD

2.1

ns

ED/HD-SDR or ED/HD-DDR

2.3

ns

ED (at 54 MHz)

1.7

ns

Control Input Hold Time, t124

SD

1.0

ns

ED/HD-SDR or ED/HD-DDR

1.1

ns

ED (at 54 MHz)

1.0

ns

Control Output Access Time, t134

SD

12

ns

ED/HD-SDR, ED/HD-DDR, or ED (at 54 MHz)

10

ns

Control Output Hold Time, t144

SD

4.0

ns

ED/HD-SDR, ED/HD-DDR, or ED (at 54 MHz)

3.5

ns

CVBS/Y-C Outputs (2×)

SD oversampling disabled

68

Clock cycles

CVBS/Y-C Outputs (8×)

SD oversampling enabled

79

Clock cycles

CVBS/Y-C Outputs (16×)

SD oversampling enabled

67

Clock cycles

Component Outputs (2×)

SD oversampling disabled

78

Clock cycles

Component Outputs (8×)

SD oversampling enabled

69

Clock cycles

Component Outputs (16×)

SD oversampling enabled

84

Clock cycles

Component Outputs (1×)

ED oversampling disabled

41

Clock cycles

Component Outputs (4×)

ED oversampling enabled

49

Clock cycles

Component Outputs (8×)

ED oversampling enabled

46

Clock cycles

Component Outputs (1×)

HD oversampling disabled

40

Clock cycles

Component Outputs (2×)

HD oversampling enabled

42

Clock cycles

Component Outputs (4×)

HD oversampling enabled

44

Clock cycles

RESET CONTROL

RESET Low Time

100

ns

1

SD = standard definition, ED = enhanced definition (525p/625p), HD = high definition, SDR = single data rate, DDR = dual data rate.

2

Video data: P[15:0] for ADV7392/ADV7393 or P[7:0] for ADV7390/ADV7391.

3

Video control: HSYNC and VSYNC.

4

Guaranteed by characterization.

5

Guaranteed by design.

相关PDF资料 |

PDF描述 |

|---|---|

| ADV7511KSTZ | IC XMITTER HDMI 12BIT 100LQFP |

| ADV7511WBSWZ | IC XMITTER HDMI AUTO 64LQFP |

| ADV7622BSTZ-RL | IC TXRX HDMI 4:1 144LQFP |

| ADV7623BSTZ | IC TXRX HDMI 4:1 144LQFP |

| ADW54010Z-0REEL | IC SWITCH DUAL SPDT 10MSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADV7391BCPZ-REEL | 功能描述:IC VIDEO ENCODER SD/HD 32-LFCSP RoHS:是 类别:集成电路 (IC) >> 接口 - 编码器,解码器,转换器 系列:- 产品变化通告:Development Systems Discontinuation 26/Apr/2011 标准包装:1 系列:- 类型:编码器 应用:DVB-S.2 系统 电压 - 电源,模拟:- 电压 - 电源,数字:- 安装类型:- 封装/外壳:模块 供应商设备封装:模块 包装:散装 其它名称:Q4645799 |

| ADV7391EBZ | 制造商:AD 制造商全称:Analog Devices 功能描述:Low Power, Chip Scale 10-Bit SD/HD Video Encoder |

| ADV7391WBCPZ | 制造商:Analog Devices 功能描述: |

| ADV7391WBCPZ-RL | 制造商:Analog Devices 功能描述: |

| ADV7392 | 制造商:AD 制造商全称:Analog Devices 功能描述:Low Power, Chip Scale 10-Bit SD/HD Video Encoder |

发布紧急采购,3分钟左右您将得到回复。