- 您现在的位置:买卖IC网 > PDF目录166215 > AM29F800BB-70SD (SPANSION LLC) Flash Memory IC; Memory Size:8Mbit; Package/Case:44-SOIC; Leaded Process Compatible:Yes; Peak Reflow Compatible (260 C):Yes; Supply Voltage Max:5V; Access Time, Tacc:70ns; Series:AM29 RoHS Compliant: Yes PDF资料下载

参数资料

| 型号: | AM29F800BB-70SD |

| 厂商: | SPANSION LLC |

| 元件分类: | PROM |

| 英文描述: | Flash Memory IC; Memory Size:8Mbit; Package/Case:44-SOIC; Leaded Process Compatible:Yes; Peak Reflow Compatible (260 C):Yes; Supply Voltage Max:5V; Access Time, Tacc:70ns; Series:AM29 RoHS Compliant: Yes |

| 中文描述: | 512K X 16 FLASH 5V PROM, 70 ns, PDSO44 |

| 封装: | LEAD FREE, MO-180AA, SOP-44 |

| 文件页数: | 14/45页 |

| 文件大小: | 1402K |

| 代理商: | AM29F800BB-70SD |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页当前第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页

March 3, 2009 21504E6

Am29F800B

19

D A TA SH EE T

WRITE OPERATION STATUS

The device provides several bits to determine the sta-

tus of a write operation: DQ2, DQ3, DQ5, DQ6, DQ7,

and RY/BY#. Table 6 and the following subsections de-

scribe the functions of these bits. DQ7, RY/BY#, and

DQ6 each offer a method for determining whether a

program or erase operation is complete or in progress.

These three bits are discussed first.

DQ7: Data# Polling

The Data# Polling bit, DQ7, indicates to the host

system whether an Embedded Algor ithm is in

progress or completed, or whether the device is in

Erase Suspend. Data# Polling is valid after the rising

edge of the final WE# pulse in the program or erase

command sequence.

During the Embedded Program algorithm, the device

outputs on DQ7 the complement of the datum pro-

grammed to DQ7. This DQ7 status also applies to pro-

g r am ming dur ing Er ase Suspend. When t he

Embedded Program algorithm is complete, the device

outputs the datum programmed to DQ7. The system

must provide the program address to read valid status

information on DQ7. If a program address falls within a

protected sector, Data# Polling on DQ7 is active for ap-

proximately 2 s, then the device returns to reading

array data.

During the Embedded Erase algorithm, Data# Polling

produces a “0” on DQ7. When the Embedded Erase al-

gorithm is complete, or if the device enters the Erase

Suspend mode, Data# Polling produces a “1” on DQ7.

This is analogous to the complement/true datum output

described for the Embedded Program algorithm: the

erase function changes all the bits in a sector to “1”;

prior to this, the device outputs the “complement,” or

“0.” The system must provide an address within any of

the sectors selected for erasure to read valid status in-

formation on DQ7.

After an erase command sequence is written, if all sec-

tors selected for erasing are protected, Data# Polling

on DQ7 is active for approximately 100 s, then the de-

vice returns to reading array data. If not all selected

sectors are protected, the Embedded Erase algorithm

erases the unprotected sectors, and ignores the se-

lected sectors that are protected.

When the system detects DQ7 has changed from the

complement to true data, it can read valid data at DQ7–

DQ0 on the following read cycles. This is because DQ7

may change asynchronously with DQ0–DQ6 while

Output Enable (OE#) is asserted low. The Data# Poll-

ing Timings (During Embedded Algorithms) figure in

the “AC Characteristics” section illustrates this.

Table 6 shows the outputs for Data# Polling on DQ7.

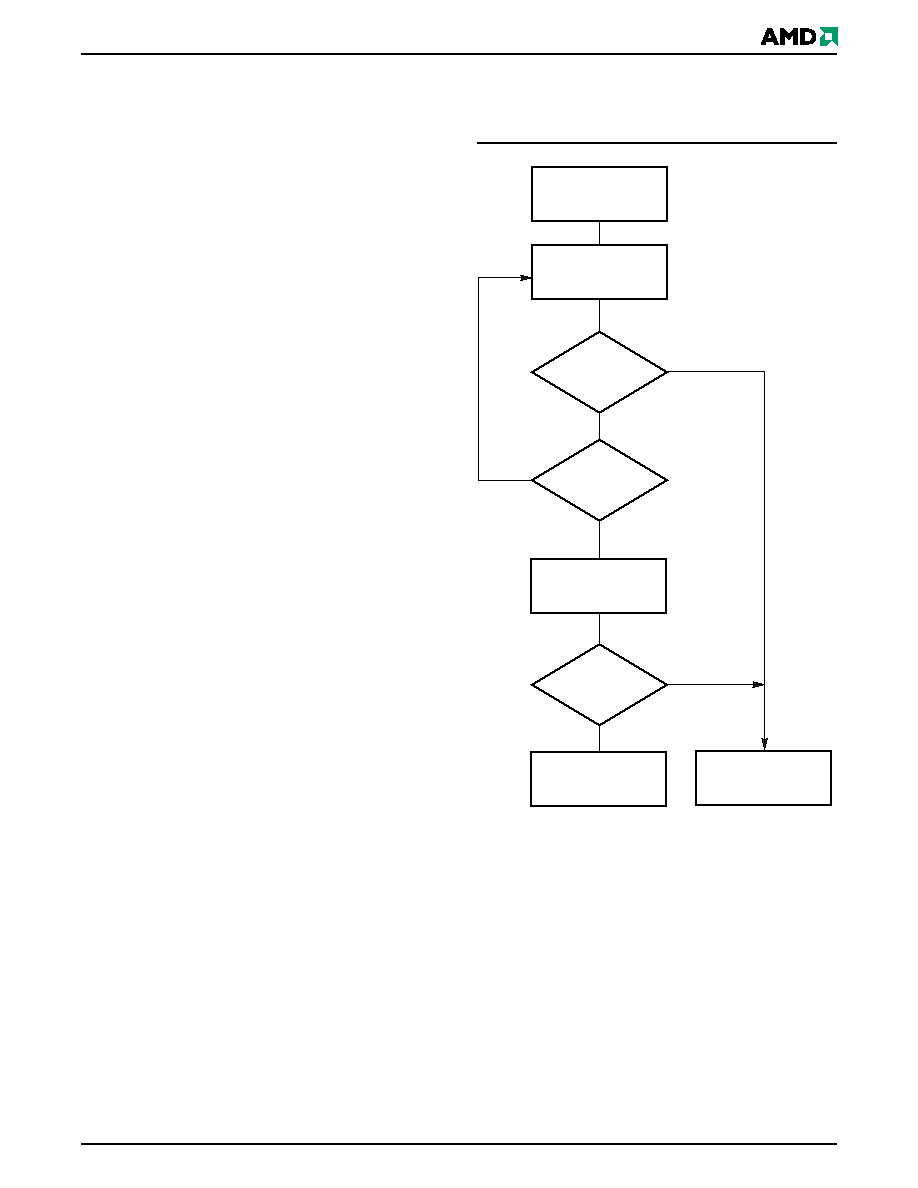

Figure 4 shows the Data# Polling algorithm.

DQ7 = Data?

Yes

No

DQ5 = 1?

No

Yes

FAIL

PASS

Read DQ7–DQ0

Addr = VA

Read DQ7–DQ0

Addr = VA

DQ7 = Data?

START

Notes:

1. VA = Valid address for programming. During a sector

erase operation, a valid address is an address within any

sector selected for erasure. During chip erase, a valid

address is any non-protected sector address.

2. DQ7 should be rechecked even if DQ5 = “1” because

DQ7 may change simultaneously with DQ5.

Figure 4.

Data# Polling Algorithm

相关PDF资料 |

PDF描述 |

|---|---|

| AM29F800BB-90ED | FLASH BOTTOM BLOCK 8MB, SMD, 29F800; Memory type:Bottom Block; Memory size:8Mbit; Memory configuration:1Mx8 or 512Kx16; Time, access:90ns; Voltage, Memory Vcc:5V; Case style:TSOP; Temperature, operating range:0(degree C) to RoHS Compliant: Yes |

| AM29F800BB-90EF | Flash Memory IC; Leaded Process Compatible:Yes; Memory Size:8Mbit; Package/Case:48-TSOP; Peak Reflow Compatible (260 C):Yes; Supply Voltage Max:5V; Access Time, Tacc:90ns; Series:AM29 RoHS Compliant: Yes |

| AM29F800BB-90SC | Flash Memory IC; Access Time, Tacc:90ns; Package/Case:44-SO; Leaded Process Compatible:No; Memory Configuration:512K x 16 / 1M x 8; Memory Size:8Mbit; Peak Reflow Compatible (260 C):No; Supply Voltage Max:5.5V RoHS Compliant: No |

| AM29F800BB-90SD | Flash Memory IC; Memory Size:8Mbit; Package/Case:44-SOIC; Leaded Process Compatible:Yes; Peak Reflow Compatible (260 C):Yes; Supply Voltage Max:5V; Access Time, Tacc:90ns; Series:AM29 RoHS Compliant: Yes |

| AM29F800BB-90SF | Flash Memory IC; Leaded Process Compatible:Yes; Memory Size:8Mbit; Package/Case:44-SOIC; Peak Reflow Compatible (260 C):Yes; Supply Voltage Max:5V; Access Time, Tacc:90ns; Series:AM29 RoHS Compliant: Yes |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AM29F800BB-70SD | 制造商:Spansion 功能描述:FLASH MEMORY IC |

| AM29F800BB-70SE | 制造商:Spansion 功能描述:NOR Flash Parallel 5V 8Mbit 1M/512K x 8bit/16bit 70ns 44-Pin SO |

| AM29F800BB-70SF | 功能描述:闪存 8M (1MX8/512KX16) Parallel NOR Fl 5V RoHS:否 制造商:ON Semiconductor 数据总线宽度:1 bit 存储类型:Flash 存储容量:2 MB 结构:256 K x 8 定时类型: 接口类型:SPI 访问时间: 电源电压-最大:3.6 V 电源电压-最小:2.3 V 最大工作电流:15 mA 工作温度:- 40 C to + 85 C 安装风格:SMD/SMT 封装 / 箱体: 封装:Reel |

| AM29F800BB-70SI | 制造商:Spansion 功能描述:8M CMOS FLASH 5V |

| AM29F800BB-90EC | 制造商:Spansion 功能描述:8M CMOS FLASH 5V |

发布紧急采购,3分钟左右您将得到回复。