- 您现在的位置:买卖IC网 > PDF目录166632 > BU-65743F3-200 (DATA DEVICE CORP) 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP80 PDF资料下载

参数资料

| 型号: | BU-65743F3-200 |

| 厂商: | DATA DEVICE CORP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP80 |

| 封装: | 0.880 INCH, CERAMIC, QFP-80 |

| 文件页数: | 17/75页 |

| 文件大小: | 532K |

| 代理商: | BU-65743F3-200 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页当前第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页

24

Data Device Corporation

www.ddc-web.com

BU-65743/65843/65863/65864

D-06/04-0

Enhanced BC mode; Enhanced CPU Access (note that this bit is

the only configuration bit that is SET after reset), RT Global

Circular Buffer (including buffer size); the RT/MT Interrupt Status

Queue, including valid/invalid message filtering; enabling a soft-

ware-assigned RT address; clock frequency selection; a base

address for the "non-data" portion of Mini-ACE Mark3/Micro-

ACE TE memory; LSB filtering for the Synchronize (with data)

time tag operations; and enabling a watchdog timer for the

Enhanced BC message sequence control engine.

BC CONDITION CODE REGISTER

The BC Condition Code Register is used to enable the host

processor to read the current value of the Enhanced BC

Message Sequence Control Engine's condition flags.

BC GENERAL PURPOSE FLAG REGISTER

The BC General Purpose Flag Register allows the host processor

to be able to set, clear, or toggle any of the Enhanced BC Message

Sequence Control Engine's General Purpose condition flags.

BIT TEST STATUS REGISTER

The BIT Test Status Register is used to provide read-only access

to the status of the RAM built-in self-tests (BIT).

BC GENERAL PURPOSE QUEUE POINTER

The BC General Purpose Queue Pointer provides a means for

initializing the pointer for the General Purpose Queue, for the

Enhanced BC mode. In addition, this register enables the host to

determine the current location of the General Purpose Queue

NOTE: Please see Appendix “F” of the Enhanced Mini-ACE

User’s Guide for important information applicable only to RT

MODE operation, enabling of the interrupt status queue and

use of specific non-message interrupts.

pointer, which is incremented internally by the Enhanced BC

message sequence control engine.

RT/MT INTERRUPT STATUS QUEUE POINTER

The RT/MT Interrupt Status Queue Pointer provides a means for

initializing the pointer for the Interrupt Status Queue, for RT, MT,

and RT/MT modes. In addition, this register enables the host to

determine the current location of the Interrupt Status Queue

pointer, which is incremented by the RT/MT message processor.

BUS CONTROLLER (BC) ARCHITECTURE

The BC functionality for the PCI Mini-ACE Mark3/Micro-ACE TE

includes two separate architectures: (1) the older, non-Enhanced

Mode, which provides complete compatibility with the previous

ACE and Mini-ACE (Plus) generation products; and (2) the

newer, Enhanced BC mode. The Enhanced BC mode offers sev-

eral new powerful architectural features. These include the incor-

poration of a highly autonomous BC message sequence control

engine, which greatly serves to offload the operation of the host

CPU.

The Enhanced BC's message sequence control engine provides

a high degree of flexibility for implementing major and minor

frame scheduling; capabilities for inserting asynchronous mes-

sages in the middle of a frame; to separate 1553 message data

from control/status data for the purpose of implementing double

buffering and performing bulk data transfers; for implementing

message retry schemes, including the capability for automatic

bus channel switchover for failed messages; and for reporting

various conditions to the host processor by means of 4 user-

defined interrupts and a general purpose queue.

In both the non-Enhanced and Enhanced BC modes, the PCI

Mini-ACE Mark3/Micro-ACE TE BC implements all MIL-STD-

1553B message formats. Message format is programmable on a

message-by-message basis by means of the BC Control Word

and the T/R bit of the Command Word for the respective mes-

sage. The BC Control Word allows 1553 message format,

1553A/B type RT, bus channel, self-test, and Status Word mask-

ing to be specified on an individual message basis. In addition,

automatic retries and/or interrupt requests may be enabled or

disabled for individual messages. The BC performs all error

checking required by MIL-STD-1553B. This includes validation of

response time, sync type and sync encoding, Manchester II

encoding, parity, bit count, word count, Status Word RT Address

field, and various RT-to-RT transfer errors. The PCI Mini-ACE

Mark3/Micro-ACE TE BC response timeout value is programma-

ble with choices of 18, 22, 50, and 130 s. The longer response

timeout values allow for operation over long buses and/or the use

of repeaters.

In its non-Enhanced Mode, the PCI Mini-ACE Mark3/Micro-ACE

TE may be programmed to process BC frames of up to 512 mes-

sages with no processor intervention. In the Enhanced BC mode,

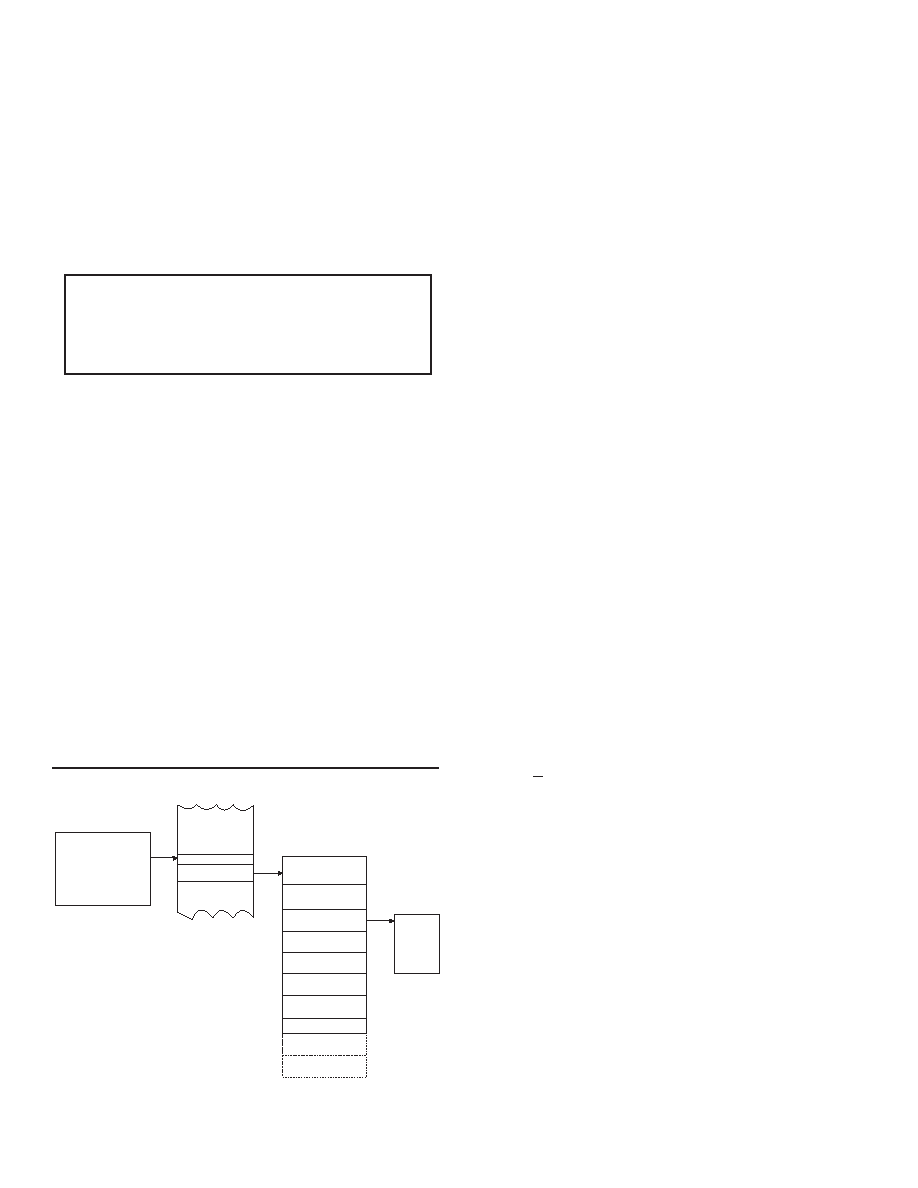

FIGURE 2. BC MESSAGE SEQUENCE CONTROL

OP CODE

DATA BLOCK

MESSAGE

CONTROL/STATUS

PARAMETER

(POINTER)

BLOCK

BC INSTRUCTION

LIST

BC INSTRUCTION

LIST POINTER REGISTER

BC CONTROL

WORD

COMMAND WORD

(Rx Command for

RT-to-RT transfer)

DATA BLOCK POINTER

TIME-TO-NEXT MESSAGE

TIME TAG WORD

BLOCK STATUS WORD

LOOPBACK WORD

RT STATUS WORD

2nd (Tx) COMMAND WORD

(for RT-to-RT transfer)

2nd RT STATUS WORD

(for RT-to-RT transfer)

INITIALIZE BY REGISTER

0D (RD/WR); READ CURRENT

VALUE VIA REGISTER 03

(RD ONLY)

相关PDF资料 |

PDF描述 |

|---|---|

| BU-65863F3-220 | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP80 |

| BU-65843B3-E02 | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, PBGA324 |

| BU-65863B8-E02 | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, PBGA324 |

| BU-65843B8-E02 | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, PBGA324 |

| BU1003 | POWER TRANSISTOR |

相关代理商/技术参数 |

参数描述 |

|---|---|

| BU6574FV | 制造商:ROHM 制造商全称:Rohm 功能描述:Silicon monolithic integrated circuit |

| BU6574FV-E2 | 功能描述:IC ANALOG FRONT END SSOP20 RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模拟前端 (AFE) 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 位数:- 通道数:2 功率(瓦特):- 电压 - 电源,模拟:3 V ~ 3.6 V 电压 - 电源,数字:3 V ~ 3.6 V 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:带卷 (TR) |

| BU6577FV | 制造商:ROHM 制造商全称:Rohm 功能描述:Silicon monolithic integrated circuit |

| BU6577FV-E2 | 制造商:ROHM Semiconductor 功能描述:ANALOG FRONT END - Tape and Reel |

| BU6581KV | 制造商:未知厂家 制造商全称:未知厂家 功能描述:コミュニケーションLSI |

发布紧急采购,3分钟左右您将得到回复。