- 您现在的位置:买卖IC网 > PDF目录166632 > BU-65743F3-200 (DATA DEVICE CORP) 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP80 PDF资料下载

参数资料

| 型号: | BU-65743F3-200 |

| 厂商: | DATA DEVICE CORP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP80 |

| 封装: | 0.880 INCH, CERAMIC, QFP-80 |

| 文件页数: | 29/75页 |

| 文件大小: | 532K |

| 代理商: | BU-65743F3-200 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页当前第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页

35

Data Device Corporation

www.ddc-web.com

BU-65743/65843/65863/65864

D-06/04-0

RT DESCRIPTOR STACK

The descriptor stack provides a chronology of all messages

processed by the PCI Mini-ACE Mark3/Micro-ACE TE RT.

Reference FIGURES 6 and 7. Similar to BC mode, there is a

four-word block descriptor in the Stack for each message

processed. The four entries to each block descriptor are the

Block Status Word, Time Tag Word, the pointer to the start of the

message's data block, and the 16-bit received Command Word.

The RT Block Status Word includes indications of whether a par-

ticular message is ongoing or has been completed, what bus

channel it was received on, indications of illegal commands, and

flags denoting various message error conditions. For the double

buffering, subaddress circular buffering, and global circular

buffering modes, the data block pointer may be used for locating

the data blocks for specific messages. Note that for mode code

commands, there is an option to store the transmitted or

received data word as the third word of the descriptor, in place of

the data block pointer.

The Time Tag Word provides a 16-bit indication of relative time

for individual messages. The resolution of the PCI Mini-ACE

Mark3/Micro-ACE TE's time tag is programmable from among 2,

4, 8, 16, 32, or 64 s/LSB using the internal clock, or it can be

programmed to increment directly from the TAG_CLK input by

writing all ones to the time tag resolution bits. If enabled, there is

a time tag rollover interrupt, which is issued when the value of

the time tag rolls over from FFFF(hex) to 0. Other time tag

options include the capabilities to clear the time tag register fol-

lowing receipt of a Synchronize (without data) mode command

and/or to set the time tag following receipt of a Synchronize (with

data) mode command. For that latter, there is an added option to

filter the "set" capability based on the LSB of the received data

word being equal to logic "0".

RT INTERRUPTS

The PCI Mini-ACE Mark3/Micro-ACE TE offers a great deal of

flexibility in terms of RT interrupt processing. By means of the

Enhanced Mini-ACE/Micro-ACE’s two Interrupt Mask Registers,

the PCI Mini-ACE Mark3/Micro-ACE TE’s RT may be pro-

grammed to issue interrupt requests for the following events/con-

ditions: End-of-(every)Message, Message Error, Selected (trans-

mit or receive) Subaddress, 100% Circular Buffer Rollover, 50%

Circular Buffer Rollover, 100% Descriptor Stack Rollover, 50%

Descriptor Stack Rollover, Selected Mode Code, Transmitter

Timeout, Illegal Command, and Interrupt Status Queue Rollover.

Interrupts for 50% Rollovers of Stacks and Circular

Buffers. The PCI Mini-ACE Mark3/Micro-ACE TE RT and

Monitor are capable of issuing host interrupts when a subad-

dress circular buffer pointer or stack pointer crosses its mid-

point boundary. For RT circular buffers, this is applicable for

both transmit and receive subaddresses. Reference FIGURE 8.

There are four interrupt mask and interrupt status register bits

associated with the 50% rollover function:

(1) RT circular buffer;

(2) RT command (descriptor) stack;

(3) Monitor command (descriptor) stack; and

(4) Monitor data stack.

The 50% rollover interrupt is beneficial for performing bulk data

transfers. For example, when using circular buffering for a partic-

ular receive subaddress, the 50% rollover interrupt will inform the

host processor when the circular buffer is half full. At that time,

the host may proceed to read the received data words in the

upper half of the buffer, while the PCI Mini-ACE Mark3/Micro-

ACE TE RT writes received data words to the lower half of the

circular buffer. Later, when the RT issues a 100% circular buffer

rollover interrupt, the host can proceed to read the received data

from the lower half of the buffer, while the PCI Mini-ACE

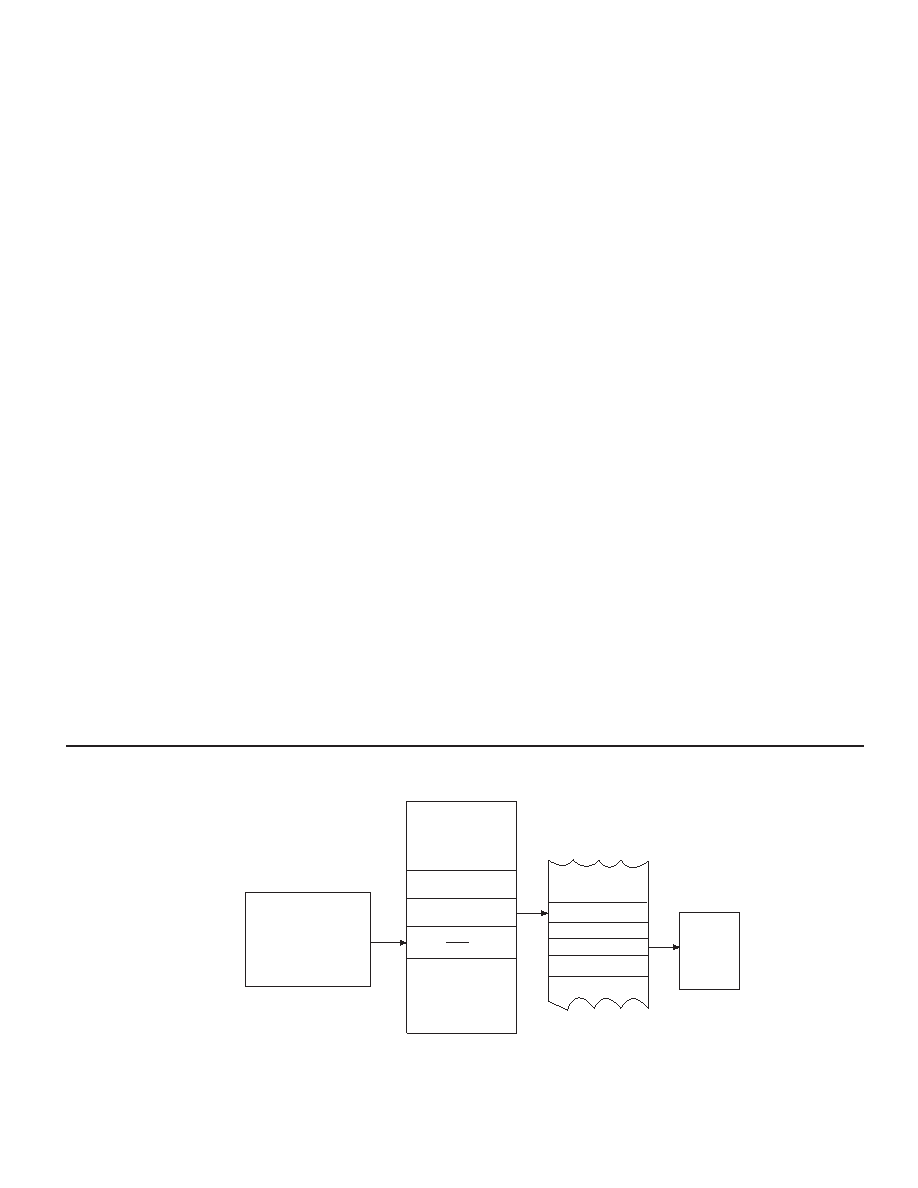

FIGURE 9. RT (and MONITOR) INTERRUPT STATUS QUEUE

(shown for message Interrupt event)

INTERRUPT

VECTOR

DATA WORD

BLOCK

DESCRIPTOR

STACK

PARAMETER

(POINTER)

INTERRUPT STATUS QUEUE

(64 Locations)

INTERRUPT VECTOR

QUEUE POINTER

REGISTER (IF)

BLOCK STATUS WORD

TIME TAG

DATA BLOCK POINTER

RECEIVED COMMAND

NEXT

VECTOR

相关PDF资料 |

PDF描述 |

|---|---|

| BU-65863F3-220 | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP80 |

| BU-65843B3-E02 | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, PBGA324 |

| BU-65863B8-E02 | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, PBGA324 |

| BU-65843B8-E02 | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, PBGA324 |

| BU1003 | POWER TRANSISTOR |

相关代理商/技术参数 |

参数描述 |

|---|---|

| BU6574FV | 制造商:ROHM 制造商全称:Rohm 功能描述:Silicon monolithic integrated circuit |

| BU6574FV-E2 | 功能描述:IC ANALOG FRONT END SSOP20 RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模拟前端 (AFE) 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 位数:- 通道数:2 功率(瓦特):- 电压 - 电源,模拟:3 V ~ 3.6 V 电压 - 电源,数字:3 V ~ 3.6 V 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:带卷 (TR) |

| BU6577FV | 制造商:ROHM 制造商全称:Rohm 功能描述:Silicon monolithic integrated circuit |

| BU6577FV-E2 | 制造商:ROHM Semiconductor 功能描述:ANALOG FRONT END - Tape and Reel |

| BU6581KV | 制造商:未知厂家 制造商全称:未知厂家 功能描述:コミュニケーションLSI |

发布紧急采购,3分钟左右您将得到回复。