- 您现在的位置:买卖IC网 > PDF目录166632 > BU-65743F3-200 (DATA DEVICE CORP) 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP80 PDF资料下载

参数资料

| 型号: | BU-65743F3-200 |

| 厂商: | DATA DEVICE CORP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP80 |

| 封装: | 0.880 INCH, CERAMIC, QFP-80 |

| 文件页数: | 53/75页 |

| 文件大小: | 532K |

| 代理商: | BU-65743F3-200 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页当前第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页

57

Data Device Corporation

www.ddc-web.com

BU-65743/65843/65863/65864

D-06/04-0

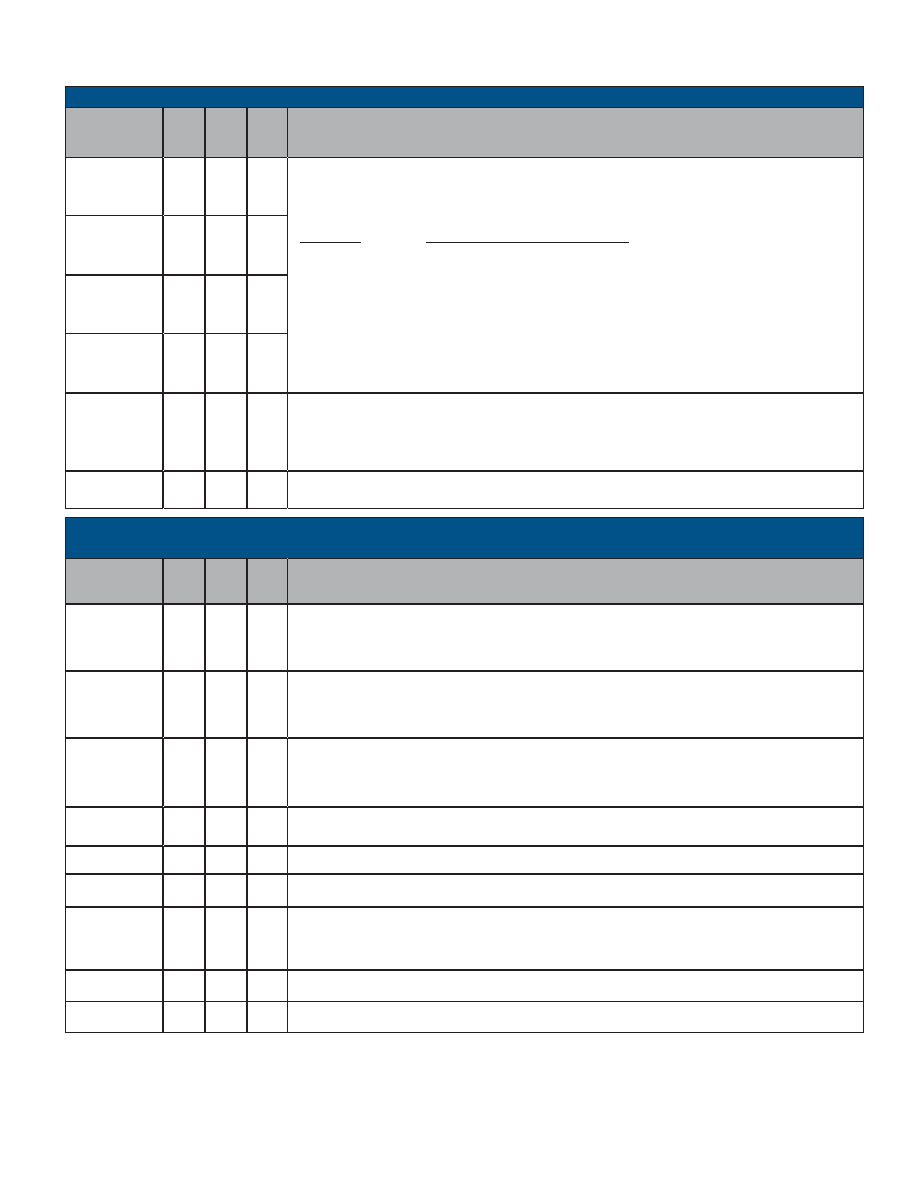

Bus Command and Byte Enables. These signals are multiplexed on the same pins. During the address

phase of a bus operation, these pins identify the bus command, as shown in the table below. During the data

phase of a bus operation, these pins are used as Byte Enables, with C/BE[0]# enabling byte 0 (LSB) and

C/BE[3]# enabling byte 3 (MSB). The PCI Mini-ACE Mark3/Micro-ACE TE responds to the following PCI

commands

C/BE[3:0]#

Description (during address phase)

0

1

0

Memory Read

0

1

Memory Write

1

0

1

0

Configuration Read

1

0

1

Configuration Write

1

0

Memory Read Multiple

1

0

Memory Read Line

1

Memory Write and Invalidate

Note that the last three memory commands are aliased to the basic memory commands: Memory Read

and Memory Write.

C/BE[0]# (I)

66

TABLE 76. PCI BUS ADDRESS AND DATA SIGNALS (CONT)

SIGNAL NAME

DESCRIPTION

PIN

B12

BALL

3V

B12

BALL

5V

C/BE[1]# (I)

58

E17

E15

C/BE[2]# (I)

47

J17

H18

C/BE[3]# (I)

37

R8

J8

PAR (I/O)

57

F16

F15

Parity. This signal is even parity across the entire AD[31:0] field along with the C/BE[3:0]# field. The parity

is stable in the clock following the address phase and is sourced by the Bus Master. During the data phase

for write operations, the Bus Master sources this signal on the clock following IRDY# active. During the data

phase for read operations, this signal is sourced by the Target and is valid on the clock following TRDY#

active. The PAR signal therefore has the same timing as AD[31:0], delayed by one clock.

PCI_CLK (I)

26

T10

M9

Clock input. The rising edge of this signal is the reference upon which all other clock signals are based, with

the exception of RST# and INTA#. The maximum frequency accepted is 33 MHz and the minimum is 0 Hz.

TABLE 77. PCI CONTROL BUS SIGNALS

(NOTE THAT ALL SIGNALS LISTED, EXCEPT INTA#, ARE SAMPLED ON THE RISING EDGE OF PCI_CLK)

SIGNAL NAME

DESCRIPTION

PIN

BALL

3V

BALL

5V

FRAME#(I)

48

G17

G15

STOP#(O)

54

E16

Stop. The Stop signal is sourced by the selected target and conveys a request to the bus master to

stop the current transaction.

DEVSEL# (O)

53

F17

Device Select. This signal is sourced by an active target upon decoding that its address and bus commands

are valid. For bus masters, it indicates whether any device has decoded the current bus cycle.

Frame. This signal is driven by the current bus master and identifies both the beginning and duration of a

bus operation. When FRAME# is first asserted, it indicates that a bus transaction is beginning and that valid

addresses and a corresponding bus command are present on the AD[31:0] and C/BE[3:0] lines, qualified by

PCI _CLK. When FRAME# is deasserted the transaction is in the final data phase or has been completed.

IRDY#(I)

49

H17

G16

Initiator Ready. This signal is sourced by the bus master and indicates that the bus master is able to com-

plete the current data phase of a bus transaction. For write operations, it indicates that valid data is on the

AD[31:0] pins. Wait states occur until both TRDY# and IRDY# are asserted together.

TRDY#(O)

52

G18

F18

Target Ready. This signal is sourced by the selected target and indicates that the target is able to complete

the current data phase of a bus transaction. For read operations, it indicates that the target is providing valid

data on the AD[31:0] pins. Wait states occur until both TRDY# and IRDY# are asserted together.

IDSEL#(I)

38

N18

K16

Initialization Device Select. This pin is used as a chip select during configuration read or write operations.

PERR# (O)

55

F18

E18

Parity Error. This pin is used for reporting parity errors during the data portion of the bus transaction for all

cycles except a Special Cycle. It is sourced by the agent receiving data and driven active two clocks fol-

lowing the detection of an error. This signal is driven inactive (high) two clocks prior to returning to the tri-

state condition.

SERR# (O)

56

F15

E17

System Error. This pin is used for reporting address parity errors, data parity errors on Special Cycle com-

mands, or any other condition having a catastrophic system impact.

INTA# (O)

24

J16

L17

Interrupt A. This pin is a level sensitive, active low interrupt to the host

相关PDF资料 |

PDF描述 |

|---|---|

| BU-65863F3-220 | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP80 |

| BU-65843B3-E02 | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, PBGA324 |

| BU-65863B8-E02 | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, PBGA324 |

| BU-65843B8-E02 | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, PBGA324 |

| BU1003 | POWER TRANSISTOR |

相关代理商/技术参数 |

参数描述 |

|---|---|

| BU6574FV | 制造商:ROHM 制造商全称:Rohm 功能描述:Silicon monolithic integrated circuit |

| BU6574FV-E2 | 功能描述:IC ANALOG FRONT END SSOP20 RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模拟前端 (AFE) 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 位数:- 通道数:2 功率(瓦特):- 电压 - 电源,模拟:3 V ~ 3.6 V 电压 - 电源,数字:3 V ~ 3.6 V 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:带卷 (TR) |

| BU6577FV | 制造商:ROHM 制造商全称:Rohm 功能描述:Silicon monolithic integrated circuit |

| BU6577FV-E2 | 制造商:ROHM Semiconductor 功能描述:ANALOG FRONT END - Tape and Reel |

| BU6581KV | 制造商:未知厂家 制造商全称:未知厂家 功能描述:コミュニケーションLSI |

发布紧急采购,3分钟左右您将得到回复。