- 您现在的位置:买卖IC网 > PDF目录366628 > C9811X2AYB Up to 5A ULDO linear regulator PDF资料下载

参数资料

| 型号: | C9811X2AYB |

| 英文描述: | Up to 5A ULDO linear regulator |

| 中文描述: | CPU系统时钟发生器| SSOP封装| 56PIN |塑料 |

| 文件页数: | 12/17页 |

| 文件大小: | 232K |

| 代理商: | C9811X2AYB |

Low EMI Clock Generator for Intel

810 Chipset Systems

Cypress Semiconductor Corporation

525 Los Coches St.

Milpitas, CA 95035. Tel: 408-263-6300, Fax: 408-263-6571

http://www.cypress.com

Document#: 38-07052 Rev. **

05/03/2001

Page 12 of 17

APPROVED PRODUCT

C9811x2

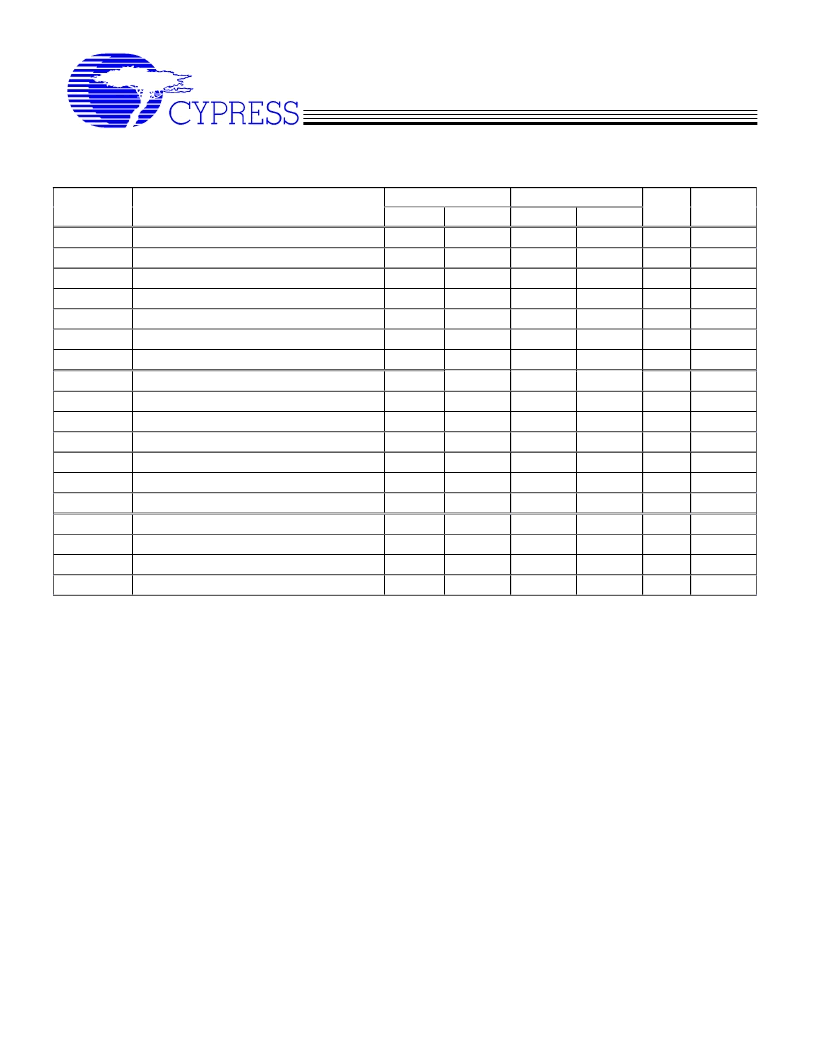

AC Parameters (Cont.)

66 MHz Host

Min

30.00

12.0

12.0

1.0

1.0

0.5

0.5

10.0

3.0

2.8

1.5

1.5

0.4

0.4

-

1.0

1.0

100 MHz Host

Min

30.0

12.0

12.0

1.0

1.0

0.5

0.5

10.0

3.0

2.8

1.5

1.5

0.4

0.4

-

1.0

1.0

Symbol

Parameter

Max

-

-

-

4.0

4.0

2.0

2.0

10.5

-

-

4.0

4.0

1.6

1.6

500

10.0

10.0

3

Max

-

-

-

4.0

4.0

2.0

2.0

10.5

-

-

4.0

4.0

1.6

1.6

500

10.0

10.00

3

Units

Notes

Tperiod

THigh

TLow

Edge Rate

Edge Rate

T Rise

T Fall

Tperiod

THigh

TLow

Edge Rate

Edge Rate

T Rise

T Fall

Tjc-c

tpZL,tpZH

tpLZ,tpZH

tstable

Notes:

1. Output drivers must have monotonic rise/fall times through the specified VOL/VOH levels.

2. Period, jitter, offset and skew measured on rising edge @ 1.25V for 2.5V clocks and @ 1.5V for 3.3V clocks.

3. THigh is measured at 2.0V for 2.5V outputs, 2.4V for 3.3V outputs.

4. TLow is measured at 0.4V for all outputs.

5. The time specified is measured from when Vddq achieves its nominal operating level (typical condition Vddq = 3.3V)

the frequency output is stable and operating within specification.

6. Trise and Tfall are measured as a transition through the threshold region Vol = 0.4V and Voh = 2.0V

7. The average period over any 1 uS period of time must be greater than the minimum specified period.

PCI CLK period (and 33 MHz IOAPIC)

PCI CLK high time (& 33 MHz IOAPIC)

PCI CLK low time (& 33 MHz IOAPIC)

Rising edge rate

Failing edge rate

PCI CLK rise time (& 33 MHz IOAPIC)

PCI CLK fall time (& 33 MHz IOAPIC)

SDRAM CLK period

SDRAM CLK high time

SDRAM CLK low time

Rising edge rate

Failing edge rate

SDRAM CLK rise time

SDRAM CLK fall time

48 MHz Clock Cycle to Cycle Jitter

Output enable delay (all outputs)

Output disable delay (all outputs)

All clock Stabilization from power-up

nS

nS

nS

V/nS

V/nS

nS

nS

nS

nS

nS

V/nS

V/nS

nS

nS

pS

nS

nS

mS

2,7

3

4

1

1

2,7

3

4

1

1

2

5

相关PDF资料 |

PDF描述 |

|---|---|

| C9812DYB | Up to 5A ULDO linear regulator |

| C9815DY | Up to 5A ULDO linear regulator |

| C9821GQ | Up to 5A ULDO linear regulator |

| C9822EQ | Up to 5A ULDO linear regulator |

| C9827JT | Up to 5A ULDO linear regulator |

相关代理商/技术参数 |

参数描述 |

|---|---|

| C9812 | 制造商:CYPRESS 制造商全称:Cypress Semiconductor 功能描述:Low EMI Clock Generator for Intel 810E Chipset Systems |

| C9812DYB | 制造商:未知厂家 制造商全称:未知厂家 功能描述:CPU SYSTEM CLOCK GENERATOR|SSOP|56PIN|PLASTIC |

| C98130-A1231-C30 | 制造商:Siemens 功能描述: |

| C9815DY | 制造商:未知厂家 制造商全称:未知厂家 功能描述:CPU SYSTEM CLOCK GENERATOR|SSOP|56PIN|PLASTIC |

| C981FFN-CTN | 制造商:Thomas & Betts 功能描述:1" FSC 1-GANG WP BOX 18 CU IN-CAN |

发布紧急采购,3分钟左右您将得到回复。