- 您现在的位置:买卖IC网 > PDF目录17028 > CORE1553-SA (Microsemi SoC)HARDWARE FOR IP CORE1553 PDF资料下载

参数资料

| 型号: | CORE1553-SA |

| 厂商: | Microsemi SoC |

| 文件页数: | 13/30页 |

| 文件大小: | 0K |

| 描述: | HARDWARE FOR IP CORE1553 |

| 标准包装: | 1 |

| 类型: | FPGA |

| 适用于相关产品: | Core1553 |

| 所含物品: | 板 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页当前第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页

�� �

�

�

�Core1553BBC� MIL-STD-1553B� Bus� Controller�

�Bus� Controller� Operation�

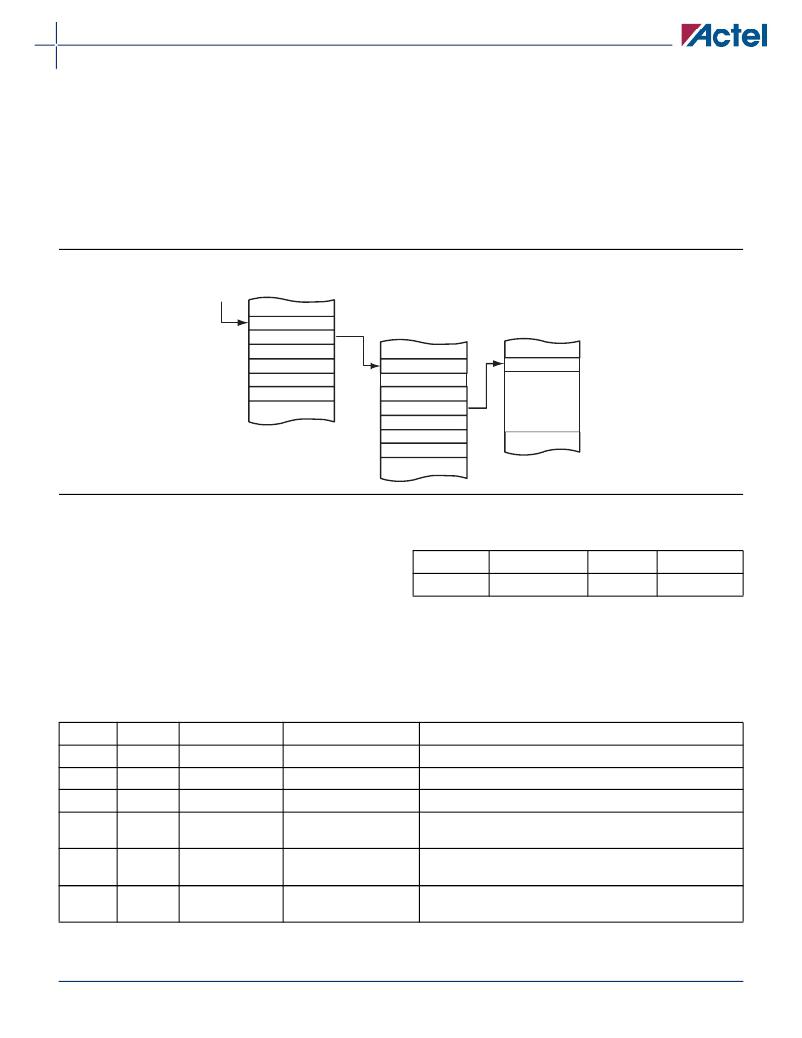

�After� power-up,� the� bus� controller� waits� while� the� CPU�

�sets� up� the� bus� controller� memory� and� registers.� The�

�memory� contains� an� instruction� list,� message� blocks,� and�

�data� blocks.� Once� the� instruction� list,� message� blocks,�

�and� data� blocks� are� setup,� the� CPU� starts� the� bus�

�controller.� The� bus� controller� works� its� way� through� all�

�the� message� blocks� until� it� reaches� the� end� of� the�

�instruction� list� (� Figure� 6� ).�

�Instruction�

�List�

�The� instruction� list� contains� a� list� of� pointers� to� message�

�blocks.� The� message� block� contains� the� command� words�

�transmitted� on� the� 1553B� bus� and� status� words� received�

�from� the� 1553B� bus.� It� also� contains� a� pointer� to� a� data�

�block.� The� data� block� contains� the� data� transmitted� on�

�the� 1553B� bus,� or� the� data� received� from� the� 1553B� bus.�

�INSTRUCTION�

�PARAMETER�

�INSTRUCTION�

�PARAMETER�

�INSTRUCTION�

�PARAMETER�

�Message�

�Block�

�MSGCMD�

�CW� (RTRT� RX)�

�CW� (RTRT� TX)�

�Data�

�Block�

�32�

�Data� Words�

�DATAPTR�

�SW� (RTRT� TX)�

�SW� (RTRT� RX)�

�TSW�

�Figure� 6� ?� BC� Memory� Usage�

�Instruction� List�

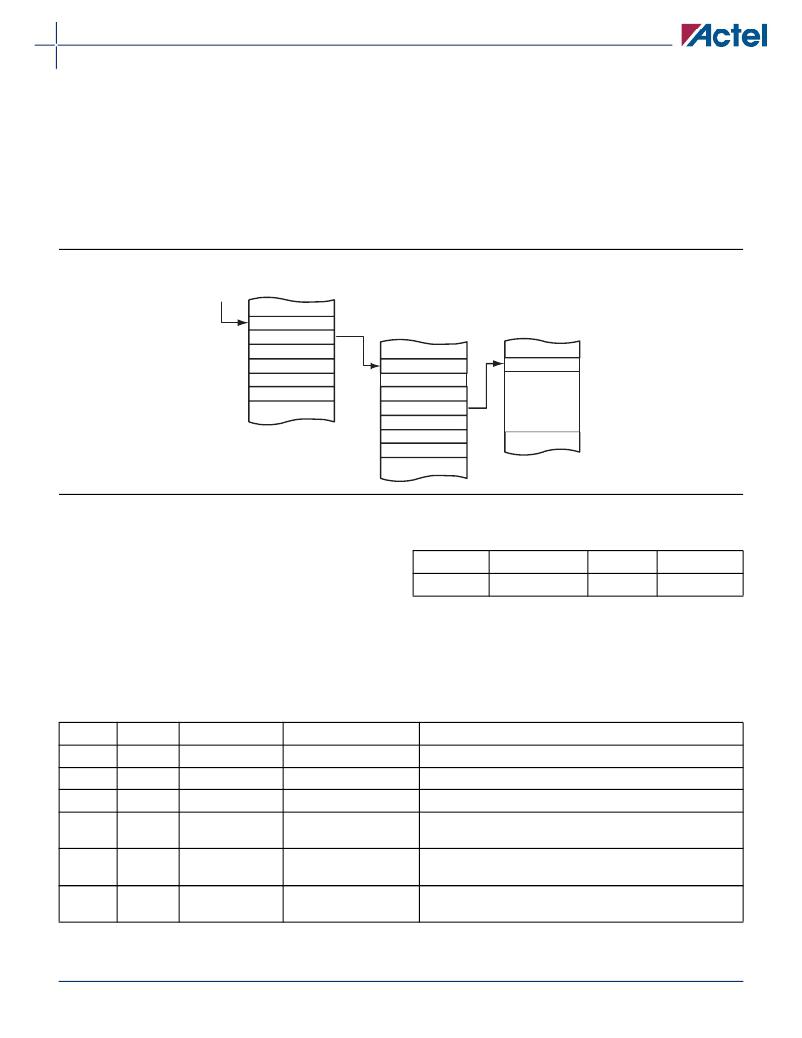

�Table� 13� ?� Instruction� Word�

�The� instruction� list� contains� pairs� of� words:� an� instruction�

�and� a� parameter.� Core1553BBC� supports� a� broad� set� of�

�instructions� allowing� branching� and� sub-routine� calls�

�15:13�

�Reserved�

�12:8�

�CONDCODE�

�7:4�

�Reserved�

�3:0�

�OPCODE�

�with� condition� code� support.� This� allows� complex�

�instruction� lists� to� be� supported.� The� instruction� contains�

��and� Table� 14� ).�

�All� of� the� OPCODES� support� the� condition� code� field.� If�

�the� condition� is� TRUE,� then� the� OPCODE� is� carried� out;�

�otherwise,� the� BC� continues� to� the� next� instruction.� For�

�RT-to-RT� messages,� the� condition� code� will� be� true� if� the�

�bit� is� set� in� either� status� word� or� not� set� in� either� status�

�word� (� Table� 15� on� page� 14� ).�

�Table� 14� ?� Supported� Instructions�

�OPCODE� Function� Condition� Code� Parameter�

�Description�

�0000�

�0001�

�0010�

�0011�

�NOP�

�DOMSG�

�JUMP�

�INTR�

�N/A�

�Yes�

�Yes�

�Yes�

�N/A�

�Message� Block� Address�

�New� Instruction� Address�

�User� interrupt� value�

�No� operation,� jumps� to� next� message�

�Process� the� message� block�

�Jumps� to� the� new� message� list� address�

�Force� a� BC� interrupt�

�(Lower� eight� bits)�

�0100�

�HALT�

�Yes�

�User� interrupt� value�

�Stop� the� BC�

�(Lower� eight� bits)�

�0101�

�DELAY�

�Yes�

�Timer� value�

�Loads� the� timer� with� the� parameter� and� waits� until� the� timer�

�(Lower� eight� bits)�

�v4.0�

�reaches� zero�

�13�

�相关PDF资料 |

PDF描述 |

|---|---|

| EBA28DRMS | CONN EDGECARD 56POS .125 SQ WW |

| AMM03DSEN | CONN EDGECARD 6POS .156 EYELET |

| VE-B50-EY | CONVERTER MOD DC/DC 5V 50W |

| STD17W-G | WIRE & CABLE MARKERS |

| HFI-201209-18NJ | INDUCTOR 2.0X1.2X0.9MM 18NH |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CORE16550-AN | 制造商:Microsemi Corporation 功能描述:CORE16X50 UNIVERSAL ASYNCHRONOUS RECEIVER/TRANSMITTER - Virtual or Non-Physical Inventory (Software & Literature) |

| CORE16550-AR | 制造商:Microsemi Corporation 功能描述:CORE16X50 UNIVERSAL ASYNCHRONOUS RECEIVER/TRANSMITTER - Virtual or Non-Physical Inventory (Software & Literature) |

| CORE16550-RM | 制造商:Microsemi Corporation 功能描述:CORE - Virtual or Non-Physical Inventory (Software & Literature) |

| CORE429-AN | 功能描述:IP MODULE CORE429 RoHS:否 类别:编程器,开发系统 >> 软件 系列:* 标准包装:1 系列:ISE® 设计套件 类型:订阅 适用于相关产品:Xilinx FPGAs 其它名称:Q4986209T1081384 |

| CORE429-AR | 功能描述:IP MODULE CORE429 RoHS:否 类别:编程器,开发系统 >> 软件 系列:* 标准包装:1 系列:ISE® 设计套件 类型:订阅 适用于相关产品:Xilinx FPGAs 其它名称:Q4986209T1081384 |

发布紧急采购,3分钟左右您将得到回复。