- 您现在的位置:买卖IC网 > PDF目录17028 > CORE1553-SA (Microsemi SoC)HARDWARE FOR IP CORE1553 PDF资料下载

参数资料

| 型号: | CORE1553-SA |

| 厂商: | Microsemi SoC |

| 文件页数: | 19/30页 |

| 文件大小: | 0K |

| 描述: | HARDWARE FOR IP CORE1553 |

| 标准包装: | 1 |

| 类型: | FPGA |

| 适用于相关产品: | Core1553 |

| 所含物品: | 板 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页当前第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页

�� �

�

�

�Core1553BBC� MIL-STD-1553B� Bus� Controller�

�Error� Conditions�

�Core1553BBC� monitors� bus� errors� and� in� most� cases� will� perform� automatic� retry� operations� if� recovery� is� possible�

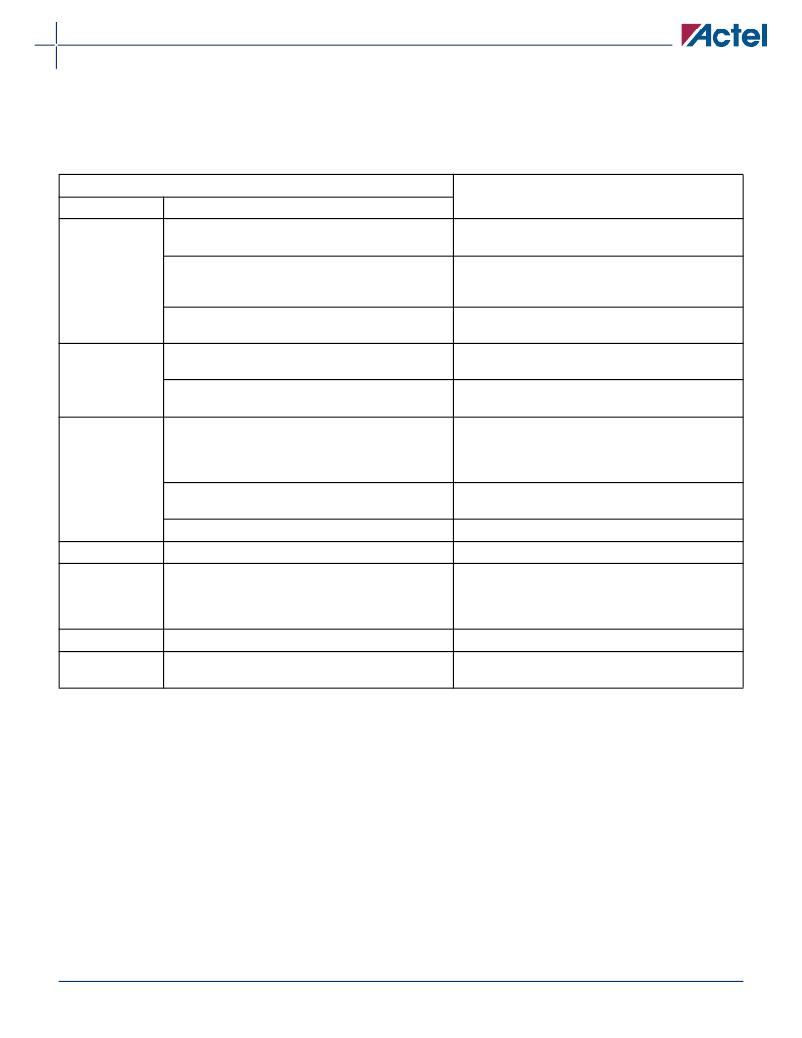

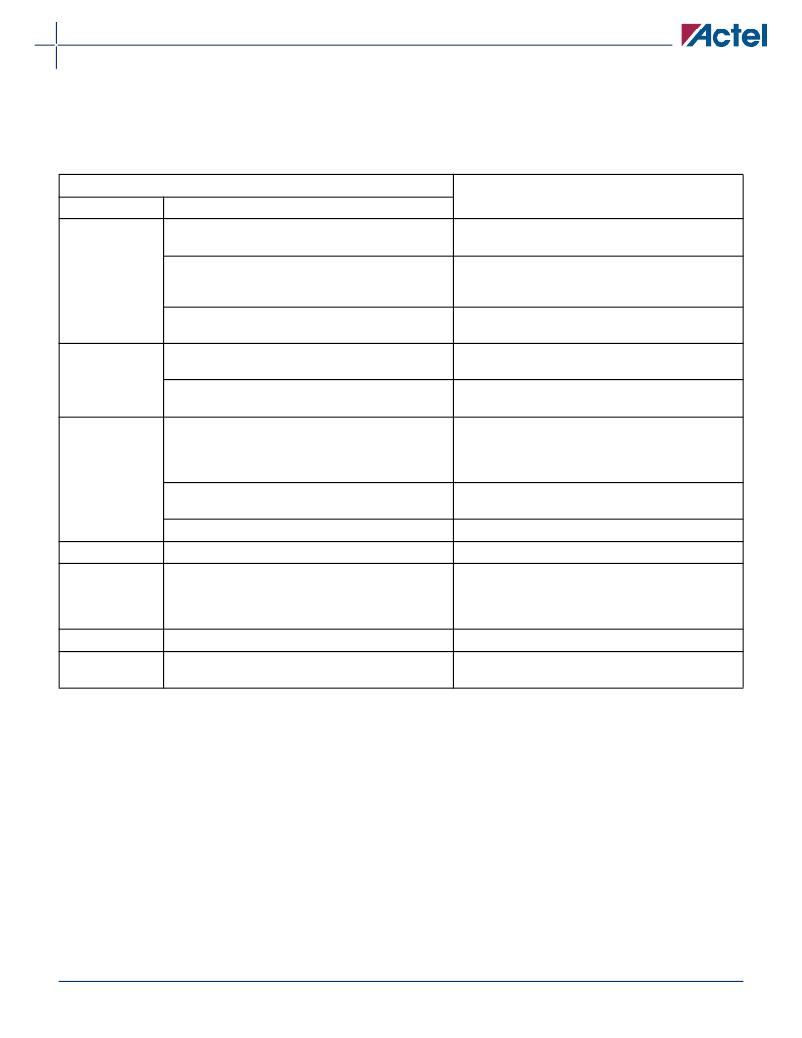

��Table� 18� ?� Error� Conditions�

�Error� Condition�

�Group�

�Signaling�

�Error�

�1553B� signaling� error,� parity,� Manchester� error,� too� Message� is� retried�

�Action�

�many� or� to� few� words,� or� incorrect� SYNC� type�

�1553B� Loopback� Failure.� Can� occur� if� an� RT� responds� Message� is� retried�

�late,� causing� the� RT� response� and� following� command� Loopback� bit� set� in� BC� status�

�word� to� corrupt� each� other� on� the� bus�

�BC� continues� to� process� messages�

�Transmitter� Overrun.� Internal� timer� detects� the� BC� has� BC� controller� aborts� and� asserts� the� transmitter�

�transmitted� for� greater� than� 688� μ� s.�

�shutdown� interrupt�

�Memory�

�Status� Word�

�RT� Response�

�Miscellaneous�

�Retry� Fails�

�Memory� Access� Failure�

�Stack� Overflow� or� Underflow�

�Terminal� Flag� in� SW�

�Sub-system� Flag� in� SW�

�Service� Request� Flag� in� SW�

�Broadcast� bit� is� SW�

�Busy� Flag� in� SW�

�Message� Error� bit� in� SW�

�Other� SW� bit�

�No� or� Late� Response�

�Corrupt� Instruction� List�

�Illegal� OPCODE�

�Message� block� MSGCMD� message� type� bits� [3:0]�

�mismatch� the� provided� command� word�

�Retries� do� not� correct� the� error�

�BC� controller� aborts� and� asserts� the� memory� failure�

�interrupt�

�BC� controller� aborts� and� asserts� the� stack� overflow�

�interrupt�

�Unexpected� bit� in� 1553B� status� bit� set� in� the� TSW.�

�Message� is� not� retried.�

�Message� is� retried�

�Message� is� retried�

�Message� is� retried�

�BC� controller� aborts� and� asserts� the� corrupt� instruction�

�list� interrupt.�

�Message� Okay� bit� in� TSW� not� set�

�CPU� Interface�

�Start� or� second� asynchronous� message� command� issued� Command� is� ignored� and� an� illegal� command� interrupt�

�while� an� asynchronous� message� is� active�

�Loop� Back� Tests�

�The� Core1553BBC� performs� loopback� testing� on� all� of� its�

�transmissions;� the� transmit� data� is� fed� back� into� the�

�receiver� and� each� transmitted� word� is� compared� to� the�

�original.� If� an� error� is� detected,� the� transmitter�

�shutdown� bit� is� set� in� the� BC� status� register.�

�Message� Sequence� Control�

�Core1553BBC� message� sequence� control� enables� it� to�

�automatically� sequence� messages� without� CPU�

�intervention.� It� supports� conditional� jumps� and� sub-�

�routine� calls� as� well� as� time� control� functions.�

�v4.0�

�is� generated.�

�All� instructions� make� use� of� the� condition� codes.� The�

�condition� codes� cover� error� conditions,� 1553B� status�

�word� values,� and� an� external� input.� Core1553BBC�

�supports� CALL� and� RETURN� instructions� with� the� aid� of� a�

�stack� that� allows� for� 255� return� addresses� to� be� stored.�

�The� stack� occupies� the� top� 256� words� of� memory.�

�To� support� message� timing� and� minor/major� frame�

�timing,� Core1553BBC� has� a� built-in� real-time� clock� (16-�

�bit)� and� timer� (8-bit)� that� can� be� used� to� synchronize�

�message� timing.� The� real� time� clock� and� timer� have� a�

�programmable� resolution� of� 1� μ� s,� 4� μ� s,� 8� μ� s,� or� 32� μ� s.�

�Messages� can� be� programmed� to� be� sent� at� an� absolute�

�time� or� relative� to� the� end� of� the� previous� message.�

�19�

�相关PDF资料 |

PDF描述 |

|---|---|

| EBA28DRMS | CONN EDGECARD 56POS .125 SQ WW |

| AMM03DSEN | CONN EDGECARD 6POS .156 EYELET |

| VE-B50-EY | CONVERTER MOD DC/DC 5V 50W |

| STD17W-G | WIRE & CABLE MARKERS |

| HFI-201209-18NJ | INDUCTOR 2.0X1.2X0.9MM 18NH |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CORE16550-AN | 制造商:Microsemi Corporation 功能描述:CORE16X50 UNIVERSAL ASYNCHRONOUS RECEIVER/TRANSMITTER - Virtual or Non-Physical Inventory (Software & Literature) |

| CORE16550-AR | 制造商:Microsemi Corporation 功能描述:CORE16X50 UNIVERSAL ASYNCHRONOUS RECEIVER/TRANSMITTER - Virtual or Non-Physical Inventory (Software & Literature) |

| CORE16550-RM | 制造商:Microsemi Corporation 功能描述:CORE - Virtual or Non-Physical Inventory (Software & Literature) |

| CORE429-AN | 功能描述:IP MODULE CORE429 RoHS:否 类别:编程器,开发系统 >> 软件 系列:* 标准包装:1 系列:ISE® 设计套件 类型:订阅 适用于相关产品:Xilinx FPGAs 其它名称:Q4986209T1081384 |

| CORE429-AR | 功能描述:IP MODULE CORE429 RoHS:否 类别:编程器,开发系统 >> 软件 系列:* 标准包装:1 系列:ISE® 设计套件 类型:订阅 适用于相关产品:Xilinx FPGAs 其它名称:Q4986209T1081384 |

发布紧急采购,3分钟左右您将得到回复。