- 您现在的位置:买卖IC网 > PDF目录379092 > CY7C4225-15JI (CYPRESS SEMICONDUCTOR CORP) 64/256/512/1K/2K/4K x18 Low-Voltage Synchronous FIFOs PDF资料下载

参数资料

| 型号: | CY7C4225-15JI |

| 厂商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分类: | DRAM |

| 英文描述: | 64/256/512/1K/2K/4K x18 Low-Voltage Synchronous FIFOs |

| 中文描述: | 1K X 18 OTHER FIFO, 10 ns, PQCC68 |

| 封装: | PLASTIC, LCC-68 |

| 文件页数: | 11/25页 |

| 文件大小: | 409K |

| 代理商: | CY7C4225-15JI |

CY7C4425/4205/4215

CY7C4225/4235/4245

11

Notes:

23. PAF offset = m. Number of data words written into FIFO already = 64 – m + 1 for the CY7C4425, 256 – m + 1 for the CY7C4205, 512 – m + 1 for the

CY7C4215. 1024 – m + 1 for the CY7C4225, 2048 – m + 1 for the CY7C4235, and 4096 – m + 1 for the CY7C4245.

24. PAF is offset = m.

25. 64 – m words in CY7C4425, 256 – m words inCY7C4205, 512 – m word in CY7C4215. 1024 – m words in CY7C4225, 2048 – m words in CY7C4235, and

4096 – m words in CY7C4245.

26. 64 – m + 1 words in CY7C4425, 256 – m + 1 words in CY7C4205, 512 – m +1 words in CY7C4215, 1024 – m + 1 CY7C4225, 2048 – m + 1 in CY74235,

and 4096 – m + 1 words in CY7C4245.

27. If a write is performed on this rising edge of the write clock, there will be Full – (m – 1) words of the FIFO when PAF goes LOW.

28. PAF offset = m.

29. 64 – m words in CY7C4425, 256 – m words in FIFO for CY7C4205, 512 – m word in CY7C4215. 1024 – m words in CY7C4225, 2048 – m words in CY7C4235,

and 4096 – m words in CY7C4245.

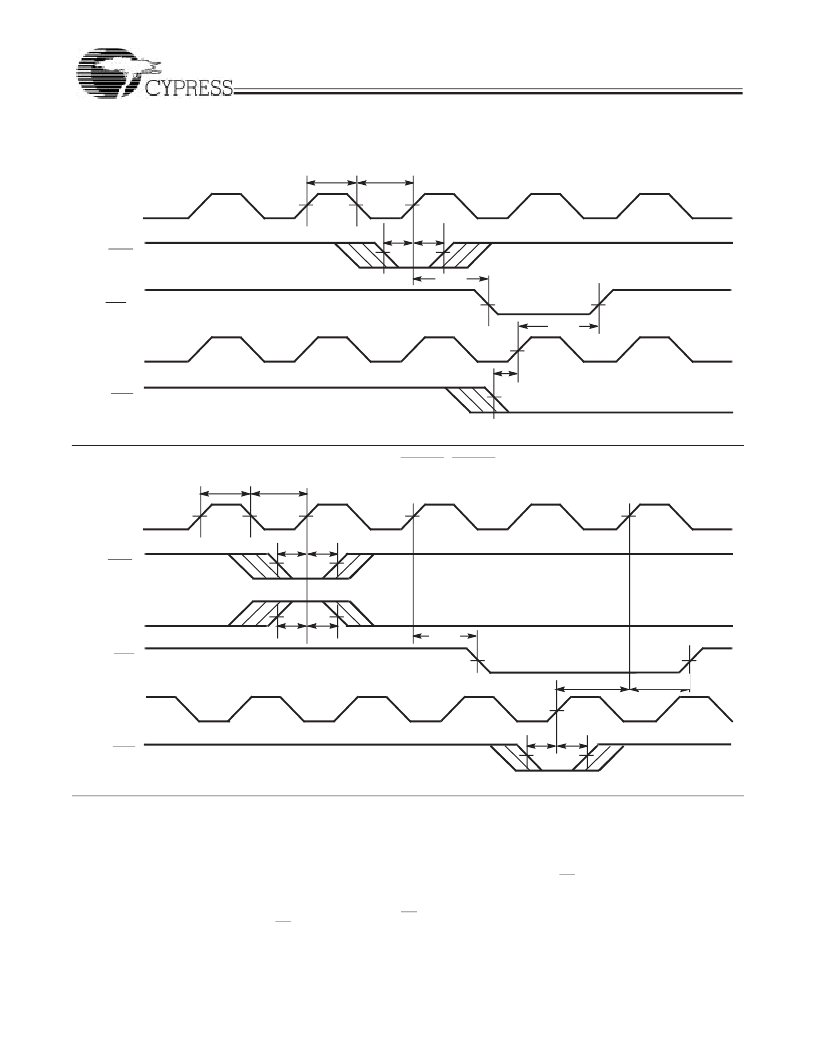

30. t

is the minimum time between a rising RCLK and a rising WCLK edge for PAF to change state during that clock cycle. If the time between the edge of RCLK and the

rising edge of WCLK is less than t

SKEW3

, then PAF may not change state until the next WCLK rising edge.

Switching Waveforms

(continued)

Note

t

ENH

WEN

WCLK

REN

RCLK

t

CLKH

t

PAF

t

ENS

t

CLKL

t

ENS

t

PAF

42X5–15

FULL

M WORDS

IN FIFO

FULL

M + 1 WORDS

IN FIFO

Programmable Almost Full Flag Timing

[26]

PAF

[24]

23

[25]

Note

27

Note

28

t

ENH

WCLK

PAF

RCLK

t

CLKH

t

ENS

FULL

M WORDS

IN FIFO

t

CLKL

t

ENS

FULL-

M+1

ORDS

INFIFO

42X5–16

t

ENH

t

ENS

t

ENH

t

ENS

t

PAF

REN

WEN2

t

SKEW3

t

PAFsynch

[30]

WEN

Programmable Almost Full Flag Timing (applies only in SMODE (SMODE in LOW))

[29]

相关PDF资料 |

PDF描述 |

|---|---|

| CY7C4225-25AC | 64/256/512/1K/2K/4K x18 Low-Voltage Synchronous FIFOs |

| CY7C4225-25AI | 64/256/512/1K/2K/4K x18 Low-Voltage Synchronous FIFOs |

| CY7C4225-25ASC | 64/256/512/1K/2K/4K x18 Low-Voltage Synchronous FIFOs |

| CY7C4225-25ASI | 64/256/512/1K/2K/4K x18 Low-Voltage Synchronous FIFOs |

| CY7C4225-25JC | 64/256/512/1K/2K/4K x18 Low-Voltage Synchronous FIFOs |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CY7C422525AC | 制造商:Cypress Semiconductor 功能描述: |

| CY7C4225-25AC | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| CY7C4225-25JC | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| CY7C4225V-15ASC | 功能描述:IC SYNC FIFO MEM 1KX18 64LQFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:CY7C 标准包装:15 系列:74F 功能:异步 存储容量:256(64 x 4) 数据速率:- 访问时间:- 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:24-DIP(0.300",7.62mm) 供应商设备封装:24-PDIP 包装:管件 其它名称:74F433 |

| CY7C4225V-15ASXC | 功能描述:先进先出 1K X18 LO VLTG SYNC 先进先出 COM RoHS:否 制造商:IDT 电路数量: 数据总线宽度:18 bit 总线定向:Unidirectional 存储容量:4 Mbit 定时类型:Synchronous 组织:256 K x 18 最大时钟频率:100 MHz 访问时间:10 ns 电源电压-最大:3.6 V 电源电压-最小:6 V 最大工作电流:35 mA 最大工作温度:+ 85 C 封装 / 箱体:TQFP-80 封装: |

发布紧急采购,3分钟左右您将得到回复。