- 您现在的位置:买卖IC网 > PDF目录379092 > CY7C4225-15JI (CYPRESS SEMICONDUCTOR CORP) 64/256/512/1K/2K/4K x18 Low-Voltage Synchronous FIFOs PDF资料下载

参数资料

| 型号: | CY7C4225-15JI |

| 厂商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分类: | DRAM |

| 英文描述: | 64/256/512/1K/2K/4K x18 Low-Voltage Synchronous FIFOs |

| 中文描述: | 1K X 18 OTHER FIFO, 10 ns, PQCC68 |

| 封装: | PLASTIC, LCC-68 |

| 文件页数: | 6/25页 |

| 文件大小: | 409K |

| 代理商: | CY7C4225-15JI |

CY7C4425/4205/4215

CY7C4225/4235/4245

6

t

PAFsynch

Clock to Programmable Almost-Full Flag

(Synchronous mode, V

CC

/SMODE tied to V

SS

)

Clock to Programmable Almost-Empty Flag

[12]

(Asynchronous mode, V

CC

/SMODE tied to V

CC

)

Clock to Programmable Almost-Full Flag

(Synchronous mode, V

CC

/SMODE tied to V

SS

)

Clock to Half-Full Flag

Clock to Expansion Out

Expansion in Pulse Width

Expansion in Set-Up Time

Skew Time between Read Clock and Write

Clock for Full Flag

Skew Time between Read Clock and Write

Clock for Empty Flag

Skew Time between Read Clock and Write

Clock for Programmable Almost Empty and Pro-

grammable Almost Full Flags.

8

10

15

20

ns

t

PAEasynch

12

16

20

25

ns

t

PAEsynch

8

10

15

20

ns

t

HF

t

XO

t

XI

t

XIS

t

SKEW1

12

7

16

10

20

15

25

20

ns

ns

ns

ns

ns

3

6.5

5

6

10

10

10

14

15

12

4.5

5

t

SKEW2

5

6

10

12

ns

t

SKEW3

10

15

18

20

ns

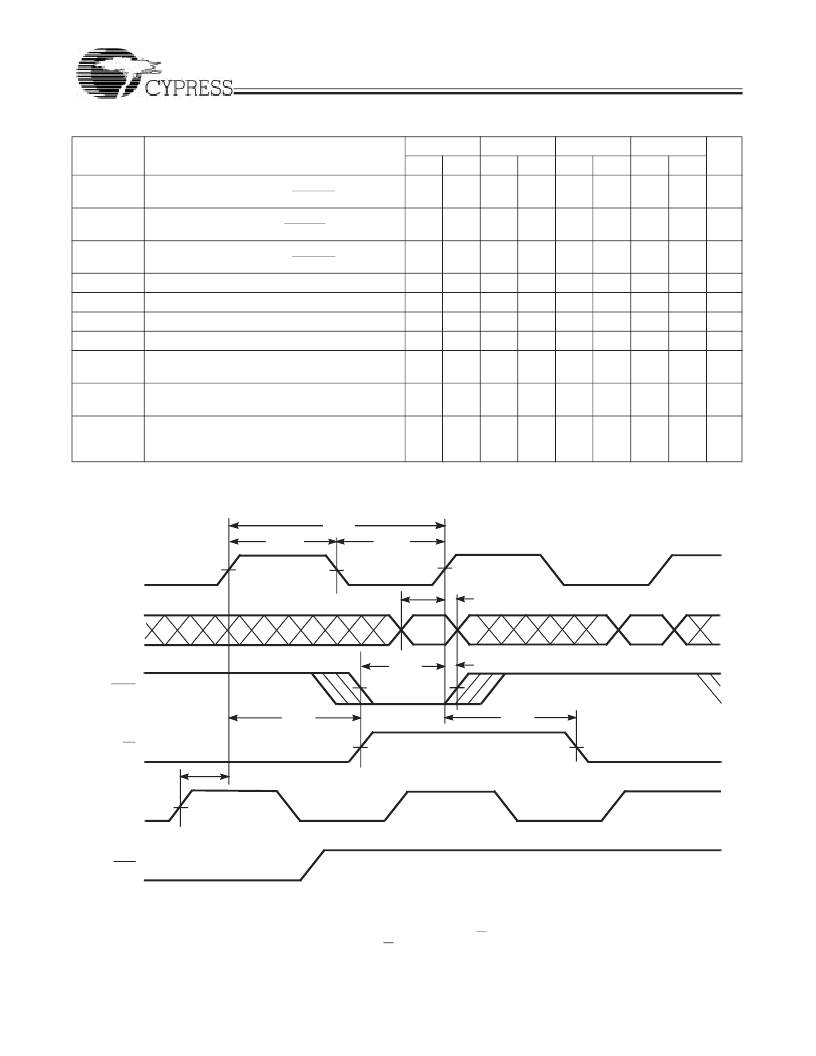

Switching Characteristics

Over the Operating Range (continued)

Parameter

Description

7C42X5-10

Min.

7C42X5-15

Min.

7C42X5-25

Min.

7C42X5-35

Min.

Max.

Max.

Max.

Max.

Unit

Switching Waveforms

Notes:

10. Pulse widths less than minimum values are not allowed.

11.

Values guaranteed by design, not currently tested.

12.

PAFasynch

, t

, after program register write will not be valid until 5 ns + t

.

13. t

is the minimum time between a rising RCLK edge and a rising WCLK edge to guarantee that FF will go HIGH during the current clock cycle. If the time between the

rising edge of RCLK and the rising edge of WCLK is less than t

SKEW1

, then FF may not change state until the next WCLK edge.

Write Cycle Timing

t

CLKH

t

CLKL

NO OPERATION

t

DS

t

SKEW1

t

ENS

WEN

t

CLK

t

DH

t

WFF

t

WFF

t

ENH

WCLK

D

0

–D

17

FF

REN

RCLK

42X5–6

[13]

相关PDF资料 |

PDF描述 |

|---|---|

| CY7C4225-25AC | 64/256/512/1K/2K/4K x18 Low-Voltage Synchronous FIFOs |

| CY7C4225-25AI | 64/256/512/1K/2K/4K x18 Low-Voltage Synchronous FIFOs |

| CY7C4225-25ASC | 64/256/512/1K/2K/4K x18 Low-Voltage Synchronous FIFOs |

| CY7C4225-25ASI | 64/256/512/1K/2K/4K x18 Low-Voltage Synchronous FIFOs |

| CY7C4225-25JC | 64/256/512/1K/2K/4K x18 Low-Voltage Synchronous FIFOs |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CY7C422525AC | 制造商:Cypress Semiconductor 功能描述: |

| CY7C4225-25AC | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| CY7C4225-25JC | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| CY7C4225V-15ASC | 功能描述:IC SYNC FIFO MEM 1KX18 64LQFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:CY7C 标准包装:15 系列:74F 功能:异步 存储容量:256(64 x 4) 数据速率:- 访问时间:- 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:24-DIP(0.300",7.62mm) 供应商设备封装:24-PDIP 包装:管件 其它名称:74F433 |

| CY7C4225V-15ASXC | 功能描述:先进先出 1K X18 LO VLTG SYNC 先进先出 COM RoHS:否 制造商:IDT 电路数量: 数据总线宽度:18 bit 总线定向:Unidirectional 存储容量:4 Mbit 定时类型:Synchronous 组织:256 K x 18 最大时钟频率:100 MHz 访问时间:10 ns 电源电压-最大:3.6 V 电源电压-最小:6 V 最大工作电流:35 mA 最大工作温度:+ 85 C 封装 / 箱体:TQFP-80 封装: |

发布紧急采购,3分钟左右您将得到回复。