- 您现在的位置:买卖IC网 > PDF目录17123 > DK-DEV-4CGX150N (Altera)KIT DEVELOPMENT CYCLONE IV GX PDF资料下载

参数资料

| 型号: | DK-DEV-4CGX150N |

| 厂商: | Altera |

| 文件页数: | 40/42页 |

| 文件大小: | 0K |

| 描述: | KIT DEVELOPMENT CYCLONE IV GX |

| 应用说明: | Cyclone IV Design Guidelines |

| 产品培训模块: | Three Reasons to Use FPGA's in Industrial Designs Cyclone IV FPGA Family Overview |

| 软件下载: | DK-DEV-4CGX150N Kit Install |

| 特色产品: | Cyclone? IV GX FPGA Development Kit |

| 标准包装: | 1 |

| 系列: | CYCLONE® IV GX |

| 类型: | FPGA |

| 适用于相关产品: | Cyclone IV GX |

| 所含物品: | 板,线缆,文档,电源 |

| 其它名称: | 544-2713 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页当前第40页第41页第42页

Chapter 1: Cyclone IV Device Datasheet

1–7

Operating Conditions

December 2013

Altera Corporation

DC Characteristics

This section lists the I/O leakage current, pin capacitance, on-chip termination (OCT)

tolerance, and bus hold specifications for Cyclone IV devices.

Supply Current

The device supply current requirement is the minimum current drawn from the

power supply pins that can be used as a reference for power size planning. Use the

Excel-based early power estimator (EPE) to get the supply current estimates for your

design because these currents vary greatly with the resources used. Table 1–6 lists the

I/O pin leakage current for Cyclone IV devices.

Bus Hold

The bus hold retains the last valid logic state after the source driving it either enters

the high impedance state or is removed. Each I/O pin has an option to enable bus

hold in user mode. Bus hold is always disabled in configuration mode.

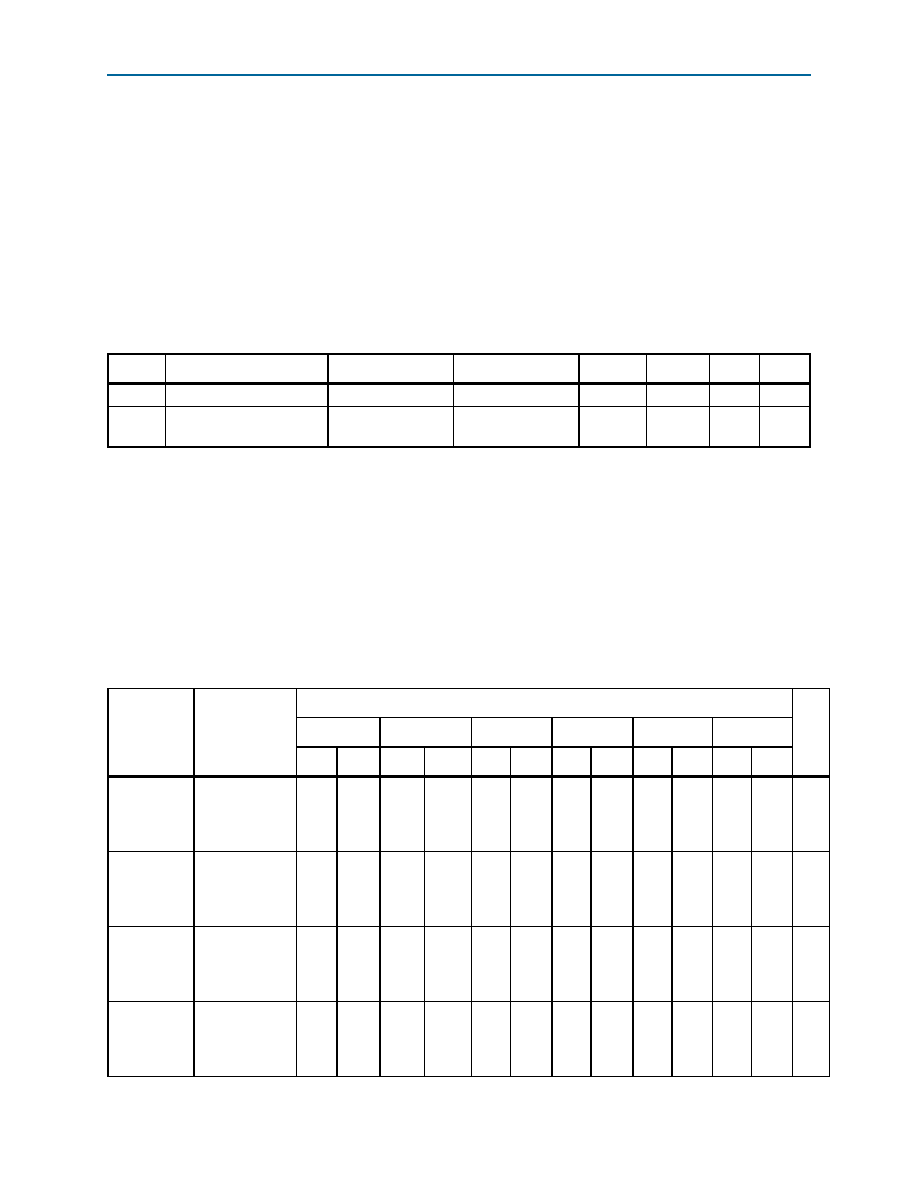

Table 1–7 lists bus hold specifications for Cyclone IV devices.

Symbol

Parameter

Conditions

Device

Min

Typ

Max

Unit

II

Input pin leakage current

VI = 0 V to VCCIOMAX

—

–10

—

10

A

IOZ

Tristated I/O pin leakage

current

VO = 0 V to VCCIOMAX

—

–10

—

10

A

Notes to Table 1–6:

(1) This value is specified for normal device operation. The value varies during device power

-up. This applies for all VCCIO settings (3.3, 3.0, 2.5,

1.8, 1.5, and 1.2 V).

(2) The 10

A I/O leakage current limit is applicable when the internal clamping diode is off. A higher current can be observed when the diode is on.

Table 1–7. Bus Hold Parameter for Cyclone IV Devices (Part 1 of 2) (1)

Parameter

Condition

VCCIO (V)

Unit

1.2

1.5

1.8

2.5

3.0

3.3

Min

Max

Min

Max

Min

Max

Min

Max

Min

Max

Min

Max

Bus hold

low,

sustaining

current

VIN > VIL

(maximum)

8

—

12

—

30—50—70

—

70

—

A

Bus hold

high,

sustaining

current

VIN < VIL

(minimum)

–8

—

–12

—

–30

—

–50

—

–70

—

–70

—

A

Bus hold

low,

overdrive

current

0 V < VIN < VCCIO

—

125

—

175

—

200

—

300

—

500

—

500

A

Bus hold

high,

overdrive

current

0 V < VIN < VCCIO

—

–125

—

–175

—

–200

—

–300

—

–500

—

–500

A

相关PDF资料 |

PDF描述 |

|---|---|

| AIRD-02-2R7K | INDUCTOR PWR DRUM CORE 2.7UH |

| AIRD-02-1R5K | INDUCTOR PWR DRUM CORE 1.5UH |

| ECC30DJCB | CONN EDGECARD 60PS .100 PRESSFIT |

| D-SCE-1K-4.8-50-S1-9 | HEAT SHRINK SLEEVE MARKER |

| SPX1431S-L/TR | IC VREF SHUNT PREC ADJ 8-SOICN |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DK-DEV-4CGX150N | 制造商:Altera Corporation 功能描述:KIT STARTER CYCLONE IV GX ((NS |

| DK-DEV-4S100G5N | 功能描述:可编程逻辑 IC 开发工具 FPGA Development Kit For EP4S100G5F RoHS:否 制造商:Altera Corporation 产品:Development Kits 类型:FPGA 工具用于评估:5CEFA7F3 接口类型: 工作电源电压: |

| DK-DEV-4SE530N | 功能描述:可编程逻辑 IC 开发工具 FPGA Development Kit For EP4SE530H35 RoHS:否 制造商:Altera Corporation 产品:Development Kits 类型:FPGA 工具用于评估:5CEFA7F3 接口类型: 工作电源电压: |

| DK-DEV-4SGX230N | 功能描述:可编程逻辑 IC 开发工具 FPGA Development Kit For EP4SGX230KF40C2N RoHS:否 制造商:Altera Corporation 产品:Development Kits 类型:FPGA 工具用于评估:5CEFA7F3 接口类型: 工作电源电压: |

| DK-DEV-4SGX230N/C2 | 功能描述:EP4SGX230KF40C2N Stratix? IV GX FPGA Evaluation Board 制造商:altera 系列:Stratix? IV GX 零件状态:过期 类型:FPGA 配套使用产品/相关产品:EP4SGX230KF40C2N 内容:板,线缆,电源 标准包装:1 |

发布紧急采购,3分钟左右您将得到回复。