- 您现在的位置:买卖IC网 > PDF目录67672 > GT-48006A (Galileo Technology Services, LLC) Low Cost Two Port 10/100Mbps Ethernet Bridge/Switch Controller(低成本、双端口10/100Mbps以太网桥式/交换式控制器) PDF资料下载

参数资料

| 型号: | GT-48006A |

| 厂商: | Galileo Technology Services, LLC |

| 英文描述: | Low Cost Two Port 10/100Mbps Ethernet Bridge/Switch Controller(低成本、双端口10/100Mbps以太网桥式/交换式控制器) |

| 中文描述: | 低成本双口10/100Mbps以太网桥/开关控制器(低成本,双端口10/100以太网桥式/交换式控制器) |

| 文件页数: | 8/33页 |

| 文件大小: | 352K |

| 代理商: | GT-48006A |

第1页第2页第3页第4页第5页第6页第7页当前第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页

GT-48006A Low Cost Two Port 10/100 Ethernet Bridge/Switch Controller

16

9.5

Data Blinder

The internal data blinder field sets the period of time during which the port does not look at the wire to decide to trans-

mit (inhibit time.) The value is fixed at 32 bit times.

9.6

Inter-Packet Gap (IPG)

IPG is the idle time between any two successive packets from the same port. The value (from the standard) is 9.6uS for

10Mbps Ethernet and 960nsec for 100-Mbps Fast Ethernet.

9.7

10/100 Mbps MII Transmission (Half-Duplex)

When the GT-48006A has a frame ready for transmission, it samples the link activity. If the RxDV signal is inactive (no

activity on the link), and the Inter-packet gap (IPG) counter has expired, frame transmission begins. The data is trans-

mitted via pins TxD[3:0] of the transmitting port, clocked on the rising edge of TxClk. The signal TxEn is asserted at this

same time. In the case of collision, the PHY asserts the CoL signal on the GT-48006A which will then stop transmitting

the frame and transmit a jam sequence onto the link. After the end of a collided transmission, the GT-48006A will back

off and attempt to retransmit once the backoff counter expires.

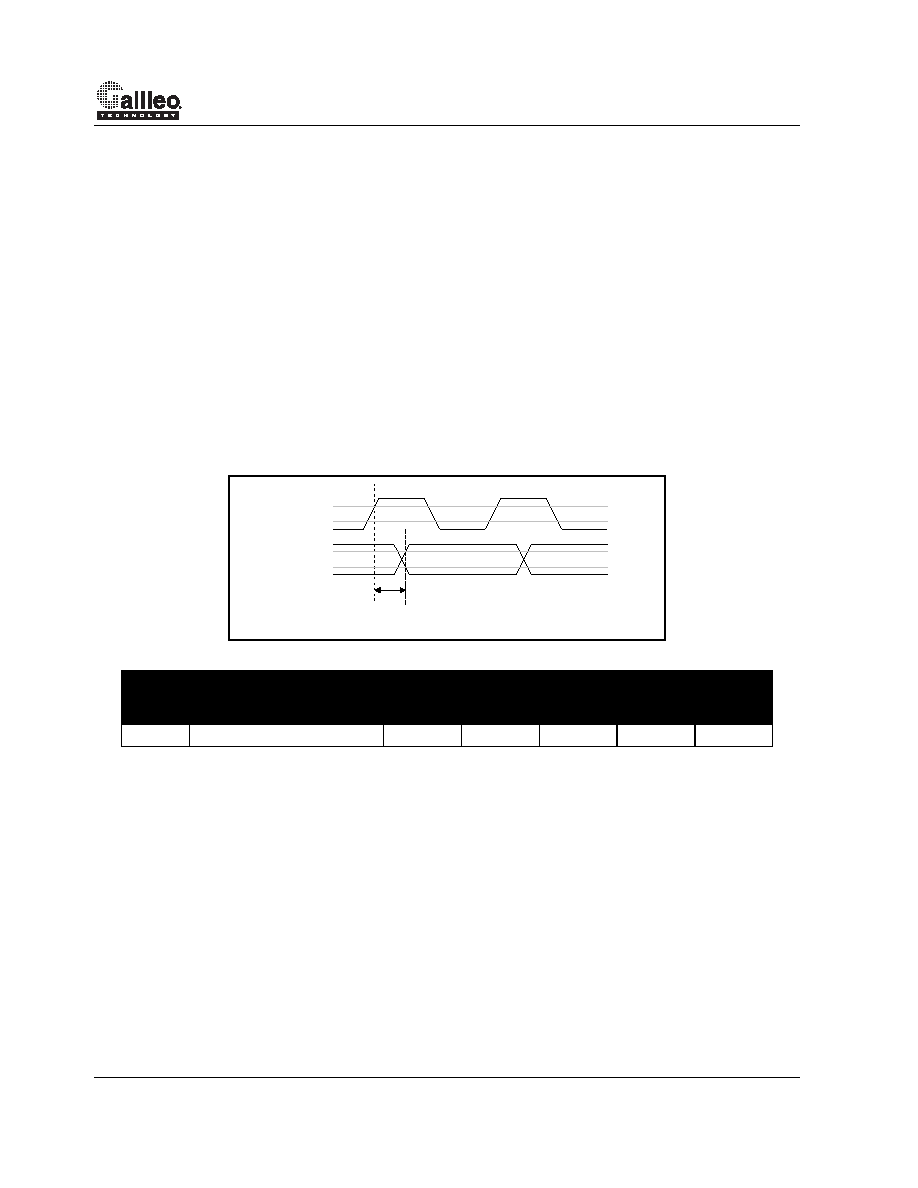

A waveform of the signals which are synchronous to TxClk (TxD0[3:0], TxD1[3:0], TxEn[1:0]) is shown in Figure 2. The

actual delay times of the GT-48006A are tighter than the IEEE 802.3u standard, clause 22.3.1, as shown in Table 3.

Figure 2: MII Transmit Signal Timing

Table 3: MII Signal Timings Synchronous to TxClk

9.8

10/100 Mbps MII Reception (Half-Duplex)

Frame reception starts with the assertion of RxDV (while the GT-48006A is not transmitting) by the PHY. Once RxDV is

asserted, the GT-48006A will begin sampling incoming data on pins RxDV[3:0] on the rising edge of RxClk. Reception

ends when the RxDV is deasserted by the PHY. The last nibble sampled by the GT-48006A is the nibble present on

RxD[3:0] on the last RxClk rising edge in which RxDV is still asserted. During reception, the RxDV is asserted. If, while

RxDV is asserted, the GT-48006A detects the assertion of RxEr, it will designate this packet as corrupted. While no

reception is taking place, RxDV should remain deasserted.

A waveform of the signals which are synchronous to RxClk (RxD0[3:0], RxD1[3:0], RxDV[1:0], RxEr[1:0]) is shown in

Figure 3. The setup and hold times of the GT-48006A are tighter than the IEEE 802.3u standard, clause 22.3.2, as

shown in Table 4.

GT-48006A

I E E E 80 2 . 3u S p ec .

Na m e

Pa ra m e te r

MI N

MAX

MI N

MAX

Un its

vd

Valid Delay after Rising TxClk

2

14

0

25

ns

vd

TxClk

TxD, TxEn

Vih

min

Vil

max

Vih

min

Vil

max

相关PDF资料 |

PDF描述 |

|---|---|

| GT-48207 | Advanced Switched Ethernet Controllers for 10+10/100 BaseX(高级交换式 10+10/100 BaseX以太网控制器) |

| GT-48208 | Advanced Switched Ethernet Controllers for 10+10/100 BaseX(高级交换式 10+10/100 BaseX以太网控制器) |

| GT-48212 | Advanced Switched Ethernet Controllers for 10+10/100 BaseX(高级交换式 10+10/100 BaseX以太网控制器) |

| GT-64010A | System Controller with PCI Interface for R4XXX/ R5000 Family CPUs(带PCI接口用于R4XXX/ R5000 系列 CPUs的系统控制器) |

| GT-64012 | Secondary Cache Controller For the MIPS R4600/4650/4700/5000,(用于MIPS R4600/4650/4700/5000处理器的二级高速缓存控制器) |

相关代理商/技术参数 |

参数描述 |

|---|---|

| GT482 | 制造商:CORNELL DUBILIER ELECTRONICS 功能描述:Cap Ceramic 82pF 3000V SL 5% (12 X 6mm) Radial 9.5mm 85°C |

| GT48212-A6-PBB1C000 | 制造商:Marvell 功能描述: |

| GT48212-A6-PBB-C000 | 制造商:Marvell 功能描述:12 PORT E + 2 PORT FE SWITCH (MANAGED) - Trays |

| GT48300-A1-BBE1C083 | 制造商:Marvell 功能描述:Marvell GT48300-A1-BBE1C083 |

| GT48300-A1-BBE-C000 | 制造商:Marvell 功能描述:Marvell GT48300-A1-BBE-C000 |

发布紧急采购,3分钟左右您将得到回复。