- 您现在的位置:买卖IC网 > PDF目录371807 > HFA3824AIV (INTERSIL CORP) Direct Sequence Spread Spectrum Baseband Processor PDF资料下载

参数资料

| 型号: | HFA3824AIV |

| 厂商: | INTERSIL CORP |

| 元件分类: | 无绳电话/电话 |

| 英文描述: | Direct Sequence Spread Spectrum Baseband Processor |

| 中文描述: | TELECOM, CELLULAR, BASEBAND CIRCUIT, PQFP48 |

| 封装: | 7 X 7 MM, PLASTIC, TQFP-48 |

| 文件页数: | 19/40页 |

| 文件大小: | 271K |

| 代理商: | HFA3824AIV |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页当前第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页

2-117

Acquisition Description

The PRISM baseband processor uses either a dual antenna

mode of operation for compensation against multipath inter-

ference losses or a single antenna mode of operation with

faster acquisition times.

Two Antenna Acquisition

During the 2 antenna (diversity) mode the two antennas are

scanned in order to find the one with the best representation

of the signal. This scanning is stopped once a suitable signal

is found and the best antenna is selected.

A projected worst case time line for the acquisition of a signal in

the two antenna case is shown in Figure 14. The synchroniza-

tion part of the preamble is 128 symbols long followed by a 16-bit

SFD. The receiver must scan the two antennas to determine if a

signal is present on either one and, if so, which has the better

signal. The timeline is broken into 16 symbol blocks (dwells) for

the scanning process. This length of time is necessary to allow

enough integration of the signal to make a good acquisition deci-

sion. This worst case time line example assumes that the signal

is present on antenna A1 only (A2 is blocked). It further assumes

that the signal arrives part way into the first A1 dwell such as to

just barely miss detection. The signal and the scanning process

are asynchronous and the signal could start anywhere. In this

timeline, it is assumed that all 16 symbols are present, but they

were missed due to power amplifier ramp up. Since A2 has

insufficient signal, the first A2 dwell after the start of the pream-

ble also fails detection. The second A1 dwell after signal start is

successful and a symbol timing measurement is achieved.

Meanwhile signal quality and signal frequency measure-

ments are made simultaneous with symbol timing measure-

ments. When the bit sync level, SQ1, and Phase variance

SQ2 are above their user programmable thresholds, the sig-

nal is declared present for the antenna with the best signal.

More details on the Signal Quality estimates and their

programmability are given in the Acquisition Signal Quality

Parameters section of this document.

At the end of each dwell, a decision is made based on the rel-

ative values of the signal qualities of the signals on the two

antennas. In the example, antenna A1 is the one selected, so

the recorded symbol timing and carrier frequency for A1 are

used thereafter for the symbol timing and the PLL of the NCO

to begin carrier de-rotation and demodulation.

Prior to initial acquisition the NCO was inactive and DPSK

demodulation processing was used. Carrier phase measure-

ment are done on a symbol by symbol basis afterward and

coherent DPSK demodulation is in effect. After a brief setup

time as illustrated on the timeline of Figure 14, the signal

begins to emerge from the demodulator.

If the descrambler is used it takes 7 more symbols to seed

the descrambler before valid data is available. This occurs in

time for the SFD to be received. At this time the demodulator

is tracking and in the coherent PSK demodulation mode it

will no longer scan antennas.

One Antenna Acquisition

When only one antenna is being used, the user can delete the

antenna switch and shorten the acquisition sequence. Figure

15 shows the single antenna acquisition timeline. It uses a 78

symbol sequence with 2 more for power ramping of the RF

front of the radio. This scheme deletes the second antenna

dwells but performs the same otherwise. It verifies the signal

after initial detection for lower false alarm probability.

Acquisition Signal Quality Parameters

Two measures of signal quality are used to determine acqui-

sition and drop lock decisions. The first method of determin-

ing signal presence is to measure the correlator output (or

bit sync) amplitude. This measure, however, flattens out in

the range of high BER and is sensitive to signal amplitude.

The second measure is phase noise and in most BER sce-

narios it is a better indication of good signals plus it is insen-

sitive to signal amplitude. The bit sync amplitude and phase

noise are integrated over each block of 16 symbols used in

acquisition or over blocks of 128 symbols in the data demod-

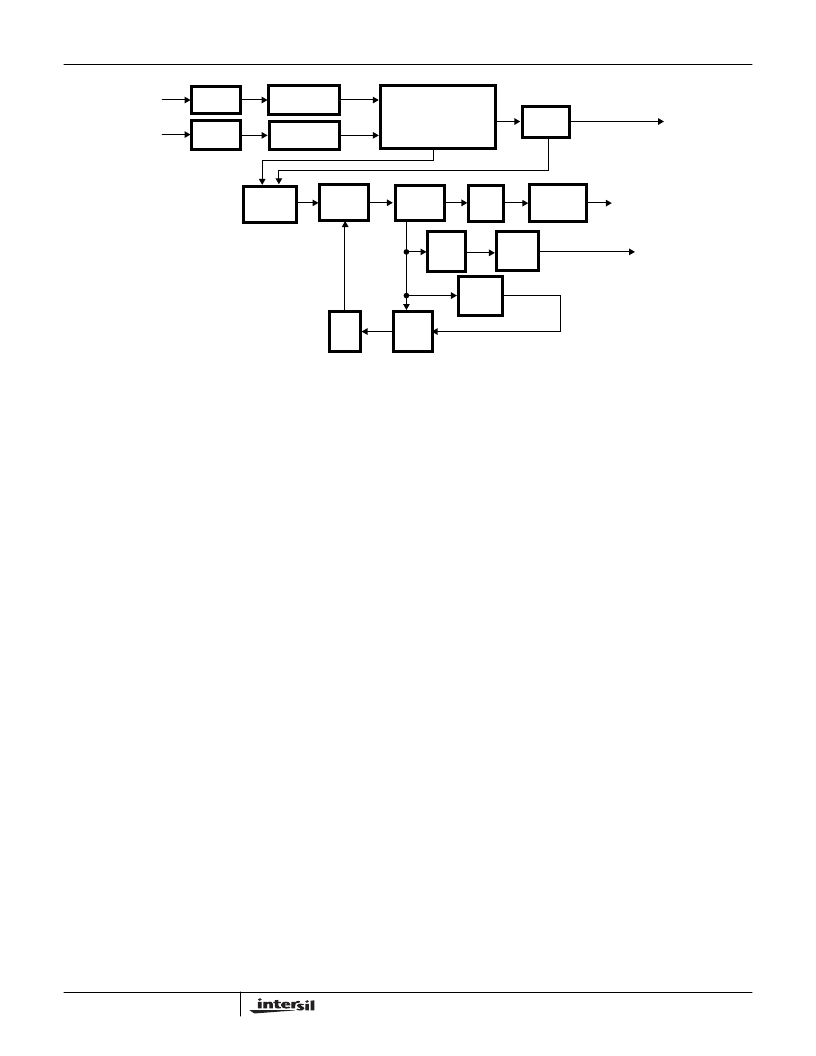

SIGNAL QUALITY 1

CORRELATOR

16TAP

MAGNITUDE AND

PHASE DISTRIBUTION

A/D

SECTION

A/D

SECTION

CORRELATOR

16TAP

DATA

DESCRAM

DIF

DEC

PSK

DEMOD

PHASE

ROTATE

TIMING

CONTROL

AVG

PHASE

FREQ.

AVG

PHASE

ERROR

ABS

PHASE

ERROR

SIGNAL QUALITY 2

SYMBOL TIMING

I

Q

SYMBOL

TIMING

NCO

LEAD

/LAG

FILTER

RXD

FIGURE 13.

DEMODULATOR BLOCK DIAGRAM

HFA3824A

相关PDF资料 |

PDF描述 |

|---|---|

| HFA3824A | Direct Sequence Spread Spectrum Baseband Processor |

| HFA3842B | PCMCIA/USB Wireless LAN Medium Access Controller |

| HFA3842BIN | PCMCIA/USB Wireless LAN Medium Access Controller |

| HFA3842BIN-TK | PCMCIA/USB Wireless LAN Medium Access Controller |

| HFA3842IN96 | Wireless LAN Medium Access Controller |

相关代理商/技术参数 |

参数描述 |

|---|---|

| HFA3824AIV WAF | 制造商:Harris Corporation 功能描述: |

| HFA3824AIV96 | 制造商:Rochester Electronics LLC 功能描述:BASEBAND PROCESSOR - Bulk |

| HFA3824EVAL | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| HFA3824IV | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| HFA3824IV96 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

发布紧急采购,3分钟左右您将得到回复。