- 您现在的位置:买卖IC网 > PDF目录371807 > HFA3824AIV (INTERSIL CORP) Direct Sequence Spread Spectrum Baseband Processor PDF资料下载

参数资料

| 型号: | HFA3824AIV |

| 厂商: | INTERSIL CORP |

| 元件分类: | 无绳电话/电话 |

| 英文描述: | Direct Sequence Spread Spectrum Baseband Processor |

| 中文描述: | TELECOM, CELLULAR, BASEBAND CIRCUIT, PQFP48 |

| 封装: | 7 X 7 MM, PLASTIC, TQFP-48 |

| 文件页数: | 26/40页 |

| 文件大小: | 271K |

| 代理商: | HFA3824AIV |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页当前第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页

2-124

Control Registers

The following tables describe the function of each control register along with the associated bits in each control register.

CONFIGURATION REGISTER 0 ADDRESS (0h) MODEM CONFIGURATION REGISTER A

Bit 7

This bit selects the transmit antenna, controlling the output ANT_SEL pin. It is only used in half duplex mode. (Bit 5 = 0)

Logic 1 = Antenna A.

Logic 0 = Antenna B.

Bit 6

In single antenna operation this bit is used as the receivers choice of antenna, controlling the output ANT_SEL pin. In dual

antenna mode this bit is ignored.

Logic 1 = Antenna A.

Logic 0 = Antenna B.

Bit 5

This selects between full and half duplex operation for the ANT_SEL pin. If set for half duplex the ANT_SEL pin will reflect

the receivers choice of antenna when TX_PE is inactive, and the value of CR0 bit-7 (TX antenna) when TX_PE is high. In

full duplex operation the ANT_SEL always reflects the receivers choice of antenna as defined by CR2 bit-2 (single or dual

antenna mode).

Logic 1 = Full duplex.

Logic 0 = Half duplex.

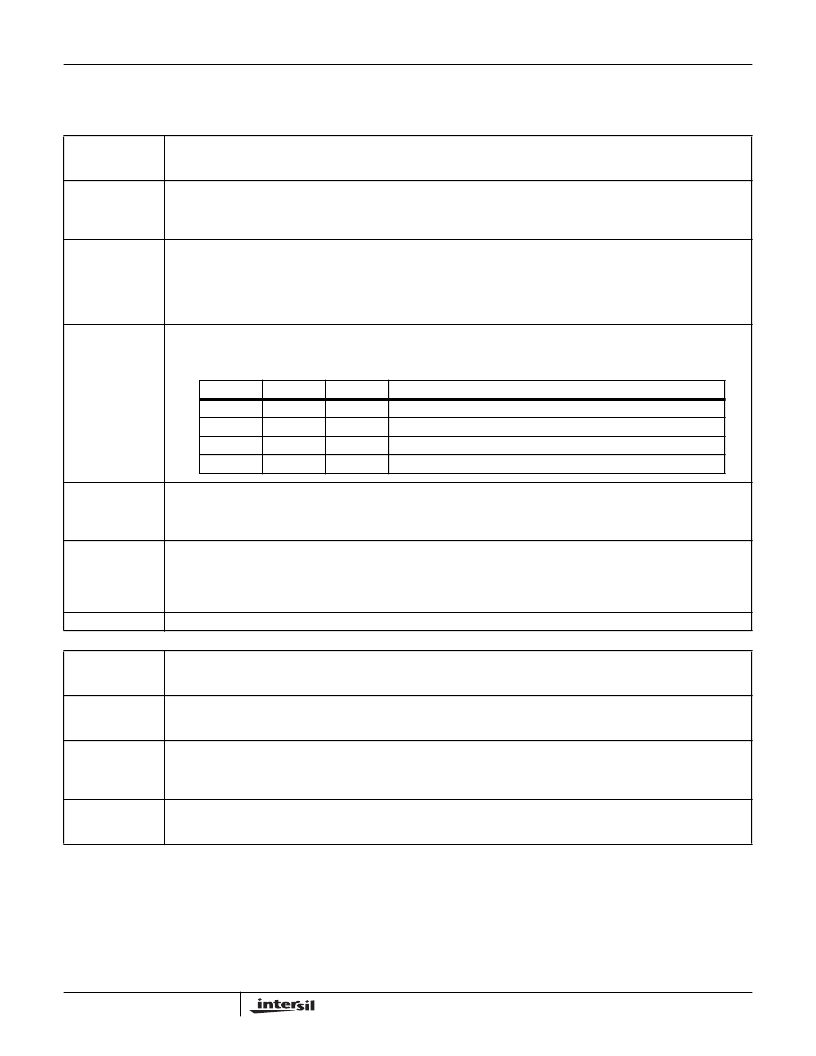

Bit 4, 3

These control bits are used to select one of the four input Preamble Header modes for transmitting data. The preamble and

header are DBPSK for all modes of operation.Mode 0 is followed by DBPSK data. For modes 1-3, the data can beconfigured

as either DBPSK or DQPSK. This is a “don’t care” if the header is generated externally.

Bit 2

This control bit is used to enable the SFD (Start Frame Delimiter) timer. If the time is set and expires before the SFD has

been detected, the HFA3824A will return to its acquisition mode.

Logic 1: Enables the SFD timer to start counting once the PN acquisition has been achieved.

Logic 0: Disables the SFD Timer.

Bit 1

Thisbitallowsthemodemtocountdownthevalueinthelengthfieldembeddedintheheader,andresetthemodemafterthedata

packetiscomplete.MD_RDYandRXCLKwillterminateafterthelastbitisoutput.Thevalueinthelengthfieldisalwaysinterpreted

as the number of bits in the data packet. This bit must be set to a “0” if CR39 Bit 6 has been set to a “1”.

Logic 1 = Enables counter.

Logic 0 = Disables counter.

Bit 0

Unused don’t care.

MODE

BIT 4

BIT 3

MODE DESCRIPTION

0

0

0

Preamble with SFD Field.

1

0

1

Preamble with SFD, and CRC16.

2

1

0

Preamble with SFD, Length, and CRC16.

3

1

1

Full preamble and header.

CONFIGURATION REGISTER 1 ADDRESS (04h) MODEM CONFIGURATION REGISTER B

Bit 7

When active this bit maintains the RXCLK and TXLK rates constant for preamble and data transfers even if the data is mod-

ulated in DQPSK. This bit is used if the external processor can not accommodate rate changes. This is an active high signal.

The rate used is the QPSK rate and the BPSK header bits are double clocked.

Bit 6, 5, 4, 3, 2

These control bits are used to define a binary count (N) from 0 - 31. This count is used to assert TX_RDY N - clocks (TXCLK)

before the beginning of the first data bit. If this is set to zero, then the TX_RDY will be asserted immediately after the last bit

of the Preamble Header.

Bit 1

When active the internal A/D calibration circuit sets the reference to mid-scale. When inactive then the calibration circuit ad-

justs the reference voltage in real time to optimize I, Q levels.

Logic 1 = Reference set at mid-scale (fixed).

Logic 0 = Real time reference adjustment.

Bit 0

When active the A/D calibration circuit is held at its last value.

Logic 1 = Reference held at the most recent value.

Logic 0 = Real time reference level adjustment.

HFA3824A

相关PDF资料 |

PDF描述 |

|---|---|

| HFA3824A | Direct Sequence Spread Spectrum Baseband Processor |

| HFA3842B | PCMCIA/USB Wireless LAN Medium Access Controller |

| HFA3842BIN | PCMCIA/USB Wireless LAN Medium Access Controller |

| HFA3842BIN-TK | PCMCIA/USB Wireless LAN Medium Access Controller |

| HFA3842IN96 | Wireless LAN Medium Access Controller |

相关代理商/技术参数 |

参数描述 |

|---|---|

| HFA3824AIV WAF | 制造商:Harris Corporation 功能描述: |

| HFA3824AIV96 | 制造商:Rochester Electronics LLC 功能描述:BASEBAND PROCESSOR - Bulk |

| HFA3824EVAL | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| HFA3824IV | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| HFA3824IV96 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

发布紧急采购,3分钟左右您将得到回复。