- 您现在的位置:买卖IC网 > PDF目录370740 > HY5R256HC -|2.5V|8K|40|Direct RDRAM - 256M PDF资料下载

参数资料

| 型号: | HY5R256HC |

| 英文描述: | -|2.5V|8K|40|Direct RDRAM - 256M |

| 中文描述: | - |为2.5V | 8K的| 40 |直接RDRAM的- 256M |

| 文件页数: | 7/64页 |

| 文件大小: | 4542K |

| 代理商: | HY5R256HC |

第1页第2页第3页第4页第5页第6页当前第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页

Rev.0.9 / Dec.2000

7

Direct RDRAM

256/288-Mbit (512Kx16/18x32s) Preliminary

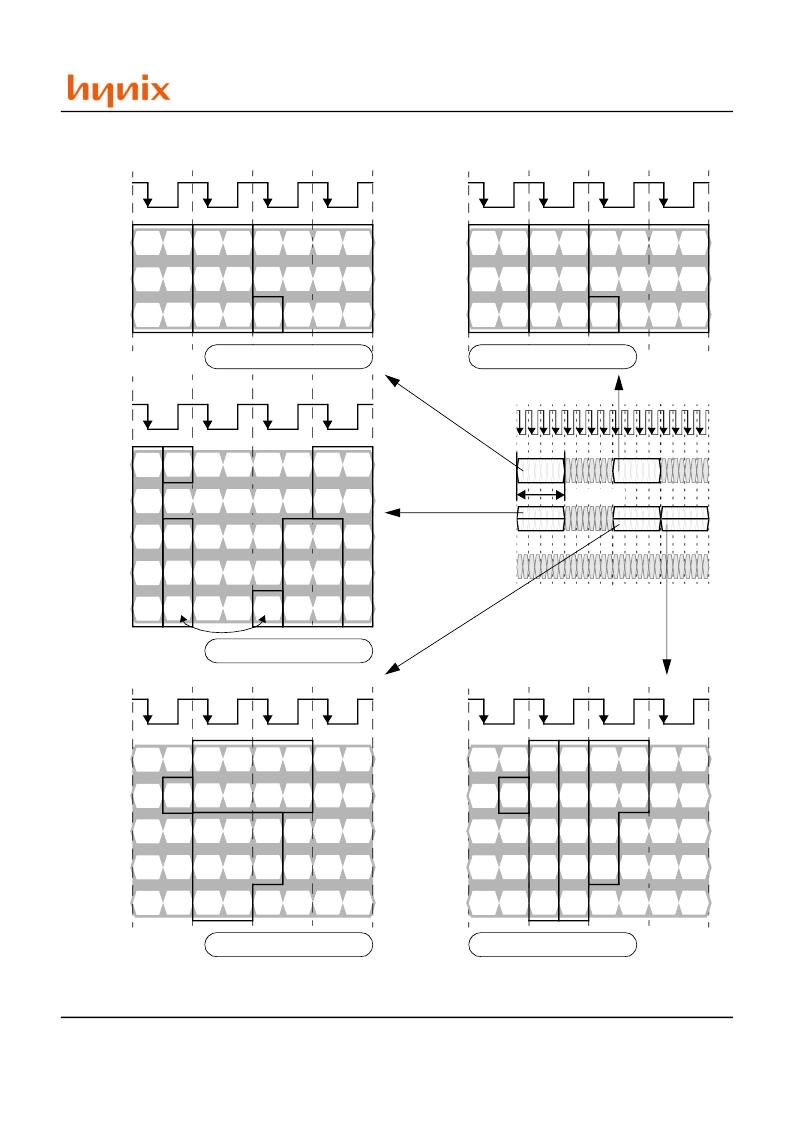

Figure 3: Packet Formats

CTM/CFM

COL4

COL3

COL2

COL1

COL0

T

8

T

9

T

10

T

11

T

12

T

13

T

14

T

15

T

8

T

9

T

10

T

11

T

0

T

1

T

2

T

3

T

0

T

1

T

2

T

3

S=1

a

MA7 MA5 MA3 MA1

M=1 MA6 MA4 MA2 MA0

MB7 MB4 MB1

MB6 MB3 MB0

MB5 MB2

R2

CTM/CFM

ROW2

DR4T DR2

BR0

BR3 RsvR

R8

R5

ROW1

DR4F DR1

BR1

BR4 RsvR

R7

R4

R1

ROW0

DR3 DR0

BR2 RsvB AV=1

R6

R3

R0

ACT a0

PREX d0

MSK (b1)

PRER c0

WR b1

C4

CTM/CFM

COL4

DC4

S=1

C6

COL3

DC3

C5

C3

COL2

DC2 COP1

RsvB BC2

C2

DC1 COP0

BC4

BC1

C1

DC0 COP2

COP3 BC3

BC0

C0

COL1

COL0

CTM/CFM

ROW2

ROW1

ROW0

CTM/CFM

COL4

COL3

COL2

COL1

COL0

ROP2

DR4T DR2

BR0

BR3

ROP10

ROP8ROP5

DR4F DR1

BR1

BR4 ROP9 ROP7ROP4 ROP1

DR3 DR0

BR2 RsvB AV=0 ROP6ROP3 ROP0

S=1

b

DX4 XOP4 RsvB BX1

M=0 DX3 XOP3 BX4

BX0

DX2 XOP2 BX3

DX1 XOP1 BX2

DX0 XOP0

T

0

T

4

T

8

T

12

T

1

T

5

T

9

T

13

T

2

T

6

T

10

T

14

T

3

T

7

T

11

T

15

ROWA Packet

COLM Packet

COLC Packet

COLX Packet

ROWR Packet

CTM/CFM

DQA8..0

DQB8..0

COL4

..COL0

ROW2

..ROW0

t

PACKET

a

The COLM is associated with a

previous COLC, and is aligned

with the present COLC, indicated

by the Start bit (S=1) position.

b

The COLX is aligned

with the present COLC,

indicated by the Start

bit (S=1) position.

相关PDF资料 |

PDF描述 |

|---|---|

| HY5R288HC | -|2.5V|8K|40|Direct RDRAM - 288M |

| HY5V16CF | 1Mx16|3.3V|4K|H|SDR SDRAM - 16M |

| HY5V16CF-H | x16 SDRAM |

| HY5V16CF-S | x16 SDRAM |

| HY6116-10 | x8 SRAM |

相关代理商/技术参数 |

参数描述 |

|---|---|

| HY5S2B6DLF-BE | 制造商:HYNIX 制造商全称:Hynix Semiconductor 功能描述:4Banks x 2M x 16bits Synchronous DRAM |

| HY5S2B6DLFP-BE | 制造商:HYNIX 制造商全称:Hynix Semiconductor 功能描述:4Banks x 2M x 16bits Synchronous DRAM |

| HY5S2B6DLFP-SE | 制造商:HYNIX 制造商全称:Hynix Semiconductor 功能描述:4Banks x 2M x 16bits Synchronous DRAM |

| HY5S2B6DLF-SE | 制造商:HYNIX 制造商全称:Hynix Semiconductor 功能描述:4Banks x 2M x 16bits Synchronous DRAM |

| HY5S5B2BLF-6E | 制造商:HYNIX 制造商全称:Hynix Semiconductor 功能描述:256M (8Mx32bit) Mobile SDRAM |

发布紧急采购,3分钟左右您将得到回复。