- 您现在的位置:买卖IC网 > PDF目录67712 > IDT5T2010BBGI (INTEGRATED DEVICE TECHNOLOGY INC) 5T SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PBGA144 PDF资料下载

参数资料

| 型号: | IDT5T2010BBGI |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟及定时 |

| 英文描述: | 5T SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PBGA144 |

| 封装: | GREEN, PLASTIC, BGA-144 |

| 文件页数: | 19/24页 |

| 文件大小: | 201K |

| 代理商: | IDT5T2010BBGI |

4

INDUSTRIALTEMPERATURERANGE

IDT5T2010

2.5V ZERO DELAY PLL CLOCK DRIVER TERACLOCK

NOTE:

1. Capacitance applies to all inputs except RxS, TxS, nF[2:1], FBF[2:1], and DS[1:0].

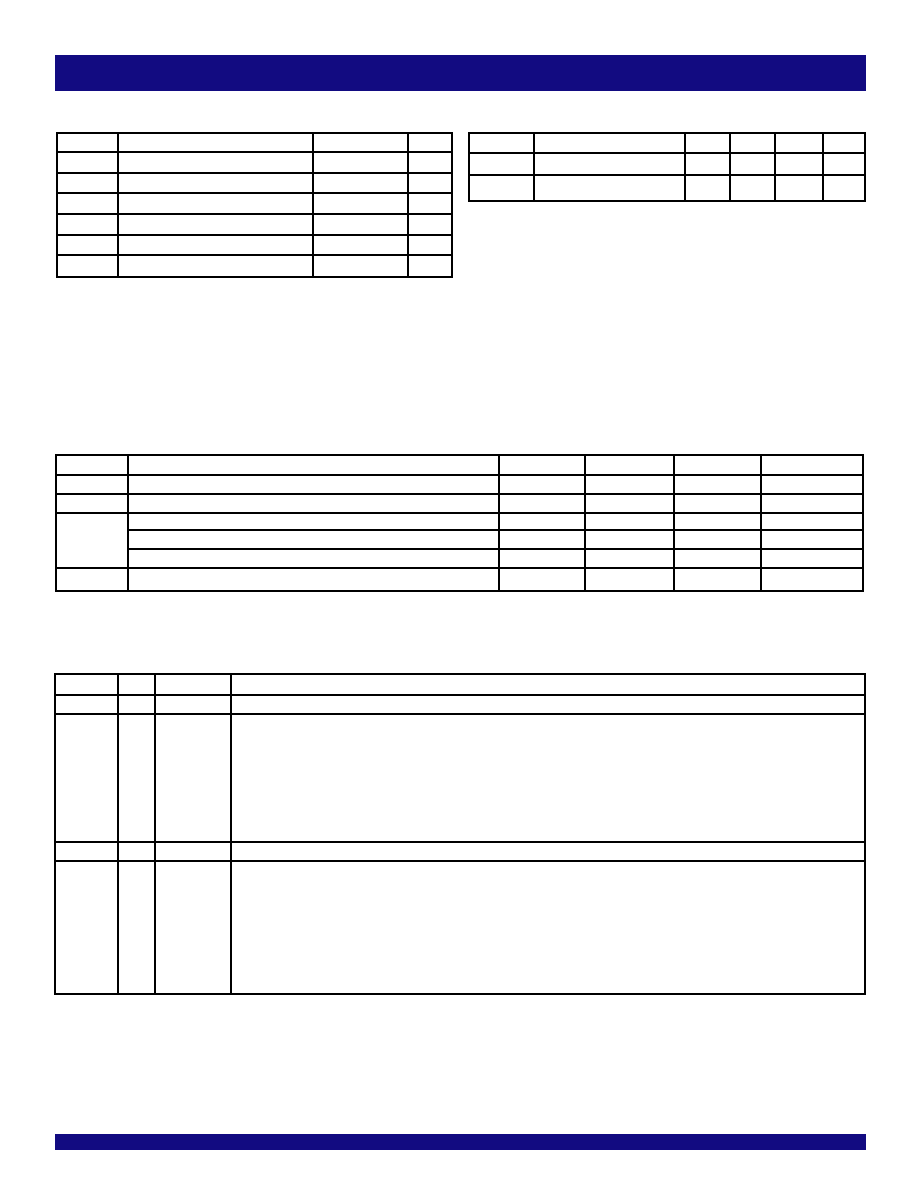

CAPACITANCE(TA=+25°C,f=1MHz,V

IN

= 0V)

Parameter

Description

Min.

Typ.

Max.

Unit

CIN

InputCapacitance

2.5

3

3.5

pF

COUT

OutputCapacitance

—

6.3

7

pF

Symbol

Description

Max

Unit

VDDQ, VDD

Power Supply Voltage(2)

–0.5 to +3.6

V

VI

Input Voltage

–0.5 to +3.6

V

VO

Output Voltage

–0.5 to VDDQ +0.5

V

VREF

Reference Voltage(3)

–0.5 to +3.6

V

TJ

Junction Temperature

150

° C

TSTG

Storage Temperature

–65 to +165

° C

ABSOLUTE MAXIMUM RATINGS(1)

NOTES:

1. Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause

permanent damage to the device. This is a stress rating only and functional operation

of the device at these or any other conditions above those indicated in the operational

sections of this specification is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect reliability.

2. VDDQ and VDD internally operate independently. No power sequencing requirements

need to be met.

3. Not to exceed 3.6V.

Symbol

Description

Min.

Typ.

Max.

Unit

TA

AmbientOperatingTemperature

–40

+25

+85

° C

VDD(1)

Internal Power Supply Voltage

2.3

2.5

2.7

V

HSTL Output Power Supply Voltage

1.4

1.5

1.6

V

VDDQ(1)

Extended HSTL and 1.8V LVTTL Output Power Supply Voltage

1.65

1.8

1.95

V

2.5V LVTTL Output Power Supply Voltage

VDD

V

VT

TerminationVoltage

VDDQ / 2

V

RECOMMENDED OPERATING RANGE

NOTE:

1. Inputs are capable of translating the following interface standards. User can select between:

Single-ended 2.5V LVTTL levels

Single-ended 1.8V LVTTL levels

or

Differential 2.5V/1.8V LVTTL levels

Differential HSTL and eHSTL levels

Differential LVEPECL levels

PIN DESCRIPTION

Symbol

I/O

Type

Description

REF[1:0]

I

Adjustable(1)

Clock input. REF[1:0] is the "true" side of the differential clock input. If operating in single-ended mode, REF[1:0] is the clock input.

REF[1:0]/

I

Adjustable(1)

Complementary clock input.

REF[1:0]/VREF[1:0] is the "complementary" side of REF[1:0] if the input is in differential mode. If operating

VREF[1:0]

in single-ended mode,

REF[1:0]/VREF[1:0] isleftfloating. Forsingle-endedoperationindifferentialmode,REF[1:0]/VREF[1:0]shouldbeset

to the desired toggle voltage for REF[1:0]:

2.5V LVTTL

VREF = 1250mV (SSTL2 compatible)

1.8V LVTTL, eHSTL

VREF = 900mV

HSTL

VREF = 750mV

LVEPECL

VREF = 1082mV

FB

I

Adjustable(1)

Clockinput. FBisthe"true"sideofthedifferentialfeedbackclockinput. Ifoperatinginsingle-endedmode,FBisthefeedbackclockinput.

FB/VREF2

I

Adjustable(1)

Complementaryfeedbackclockinput.

FB/VREF2isthe"complementary"sideofFBiftheinputisindifferentialmode. Ifoperatinginsingle-

endedmode,

FB/VREF2isleftfloating. Forsingle-endedoperationindifferentialmode, FB/VREF2shouldbesettothedesiredtogglevoltage

for FB:

2.5V LVTTL

VREF = 1250mV (SSTL2 compatible)

1.8V LVTTL, eHSTL

VREF = 900mV

HSTL

VREF = 750mV

LVEPECL

VREF = 1082mV

NOTE:

1. All power supplies should operate in tandem. If VDD or VDDQ is at maximum, then VDDQ or VDD (respectively) should be at maximum, and vice-versa.

相关PDF资料 |

PDF描述 |

|---|---|

| IDT5T2010BBI8 | 5T SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PBGA144 |

| IDT5T9010BBGI | 5T SERIES, PLL BASED CLOCK DRIVER, 5 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PBGA144 |

| IDT5T9010BBI | 5T SERIES, PLL BASED CLOCK DRIVER, 5 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PBGA144 |

| IDT5T9010BBI8 | 5T SERIES, PLL BASED CLOCK DRIVER, 5 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PBGA144 |

| IDT5T905PGGI | 5T SERIES, LOW SKEW CLOCK DRIVER, 5 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO28 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT5T2010BBGI8 | 功能描述:IC CLK DVR ZD PLL 2.5V 144-BGA RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:TeraClock™ 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| IDT5T2010BBI | 功能描述:IC CLK DVR ZD PLL 2.5V 144-BGA RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:TeraClock™ 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| IDT5T2010NLGI | 功能描述:IC CLK DVR ZD PLL 2.5V 68-VFQFPN RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:TeraClock™ 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| IDT5T2010NLGI8 | 功能描述:IC CLK DVR ZD PLL 2.5V 68-VFQFPN RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:TeraClock™ 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| IDT5T2110BBGI | 功能描述:IC CLK DVR 2.5V PLL DIFF 144BGA RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:TeraClock™ 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

发布紧急采购,3分钟左右您将得到回复。