- 您现在的位置:买卖IC网 > PDF目录67712 > IDT5T2010BBGI (INTEGRATED DEVICE TECHNOLOGY INC) 5T SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PBGA144 PDF资料下载

参数资料

| 型号: | IDT5T2010BBGI |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟及定时 |

| 英文描述: | 5T SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PBGA144 |

| 封装: | GREEN, PLASTIC, BGA-144 |

| 文件页数: | 9/24页 |

| 文件大小: | 201K |

| 代理商: | IDT5T2010BBGI |

17

INDUSTRIALTEMPERATURERANGE

IDT5T2010

2.5V ZERO DELAY PLL CLOCK DRIVER TERACLOCK

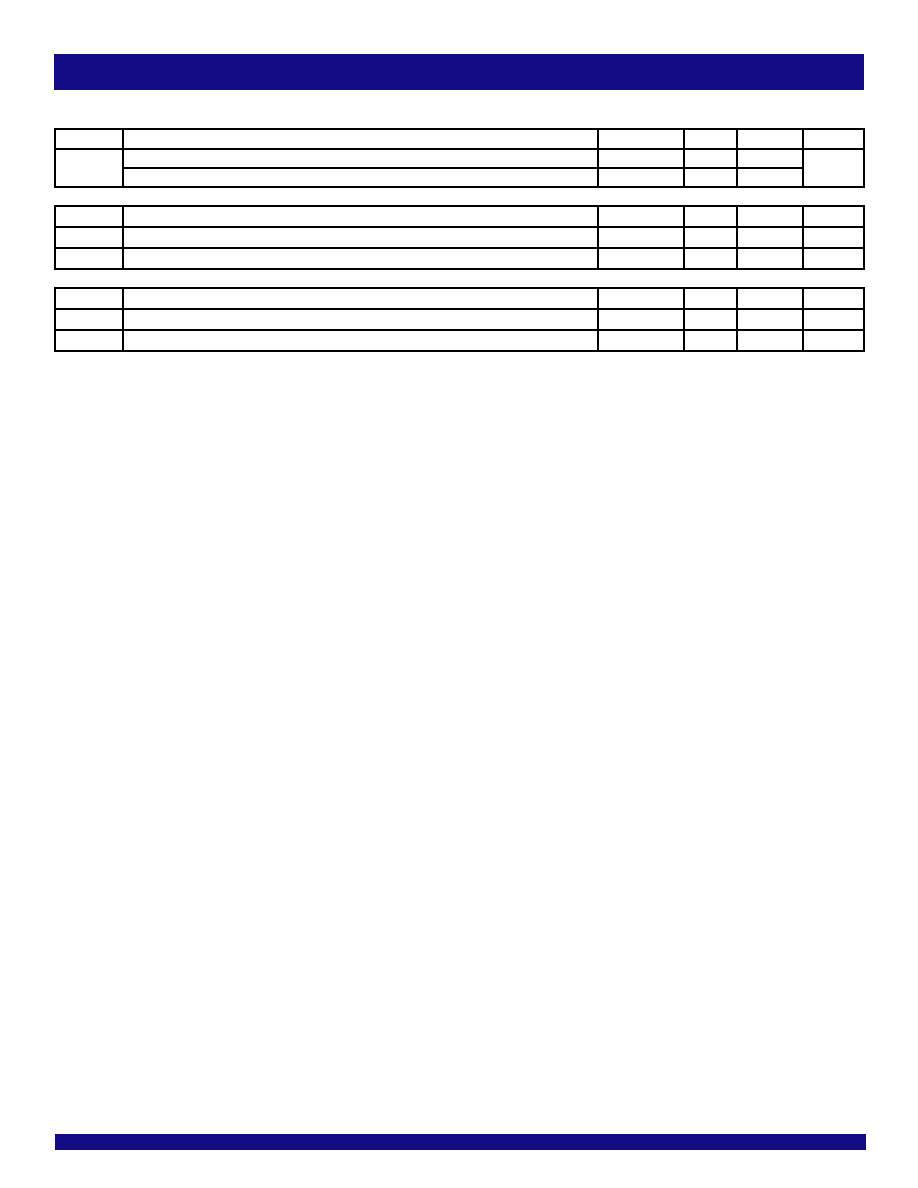

AC DIFFERENTIAL INPUT SPECIFICATIONS(1)

Symbol

Parameter

Min.

Typ.

Max

Unit

t W

Reference/Feedback Input Clock Pulse Width HIGH or LOW (HSTL/eHSTL outputs)(2)

1—

—

ns

Reference/Feedback Input Clock Pulse Width HIGH or LOW (2.5V / 1.8V LVTTL outputs)(2)

1—

—

HSTL/eHSTL/1.8V LVTTL/2.5V LVTTL

VDIF

AC Differential Voltage(3)

400

—

mV

VIH

AC Input HIGH(4,5)

Vx + 200

—

mV

VIL

AC Input LOW(4,6)

—

Vx - 200

mV

LVEPECL

VDIF

AC Differential Voltage(3)

400

—

mV

VIH

AC Input HIGH(4)

1275

—

mV

VIL

AC Input LOW(4)

—

875

mV

NOTES:

1. For differential input mode, RxS is tied to GND.

2. Both differential input signals should not be driven to the same level simultaneously. The input will not change state until the inputs have crossed and the voltage range defined

by VDIF has been met or exceeded.

3. Differential mode only.

VDIF specifies the minimum input voltage (VTR - VCP) required for switching where VTR is the "true" input level and VCP is the "complement" input level.

The AC differential voltage must be achieved to guarantee switching to a new state.

4. For single-ended operation,

REF[1:0]/VREF[1:0] is tied to the DC voltage VREF[1:0]. Refer to each input interface's DC specification for the correct VREF[1:0] range.

5. Voltage required to switch to a logic HIGH, single-ended operation only.

6. Voltage required to switch to a logic LOW, single-ended operation only.

相关PDF资料 |

PDF描述 |

|---|---|

| IDT5T2010BBI8 | 5T SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PBGA144 |

| IDT5T9010BBGI | 5T SERIES, PLL BASED CLOCK DRIVER, 5 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PBGA144 |

| IDT5T9010BBI | 5T SERIES, PLL BASED CLOCK DRIVER, 5 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PBGA144 |

| IDT5T9010BBI8 | 5T SERIES, PLL BASED CLOCK DRIVER, 5 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PBGA144 |

| IDT5T905PGGI | 5T SERIES, LOW SKEW CLOCK DRIVER, 5 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO28 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT5T2010BBGI8 | 功能描述:IC CLK DVR ZD PLL 2.5V 144-BGA RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:TeraClock™ 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| IDT5T2010BBI | 功能描述:IC CLK DVR ZD PLL 2.5V 144-BGA RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:TeraClock™ 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| IDT5T2010NLGI | 功能描述:IC CLK DVR ZD PLL 2.5V 68-VFQFPN RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:TeraClock™ 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| IDT5T2010NLGI8 | 功能描述:IC CLK DVR ZD PLL 2.5V 68-VFQFPN RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:TeraClock™ 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| IDT5T2110BBGI | 功能描述:IC CLK DVR 2.5V PLL DIFF 144BGA RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:TeraClock™ 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

发布紧急采购,3分钟左右您将得到回复。