- 您现在的位置:买卖IC网 > PDF目录67712 > IDT5T2010BBGI (INTEGRATED DEVICE TECHNOLOGY INC) 5T SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PBGA144 PDF资料下载

参数资料

| 型号: | IDT5T2010BBGI |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟及定时 |

| 英文描述: | 5T SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PBGA144 |

| 封装: | GREEN, PLASTIC, BGA-144 |

| 文件页数: | 8/24页 |

| 文件大小: | 201K |

| 代理商: | IDT5T2010BBGI |

16

INDUSTRIALTEMPERATURERANGE

IDT5T2010

2.5V ZERO DELAY PLL CLOCK DRIVER TERACLOCK

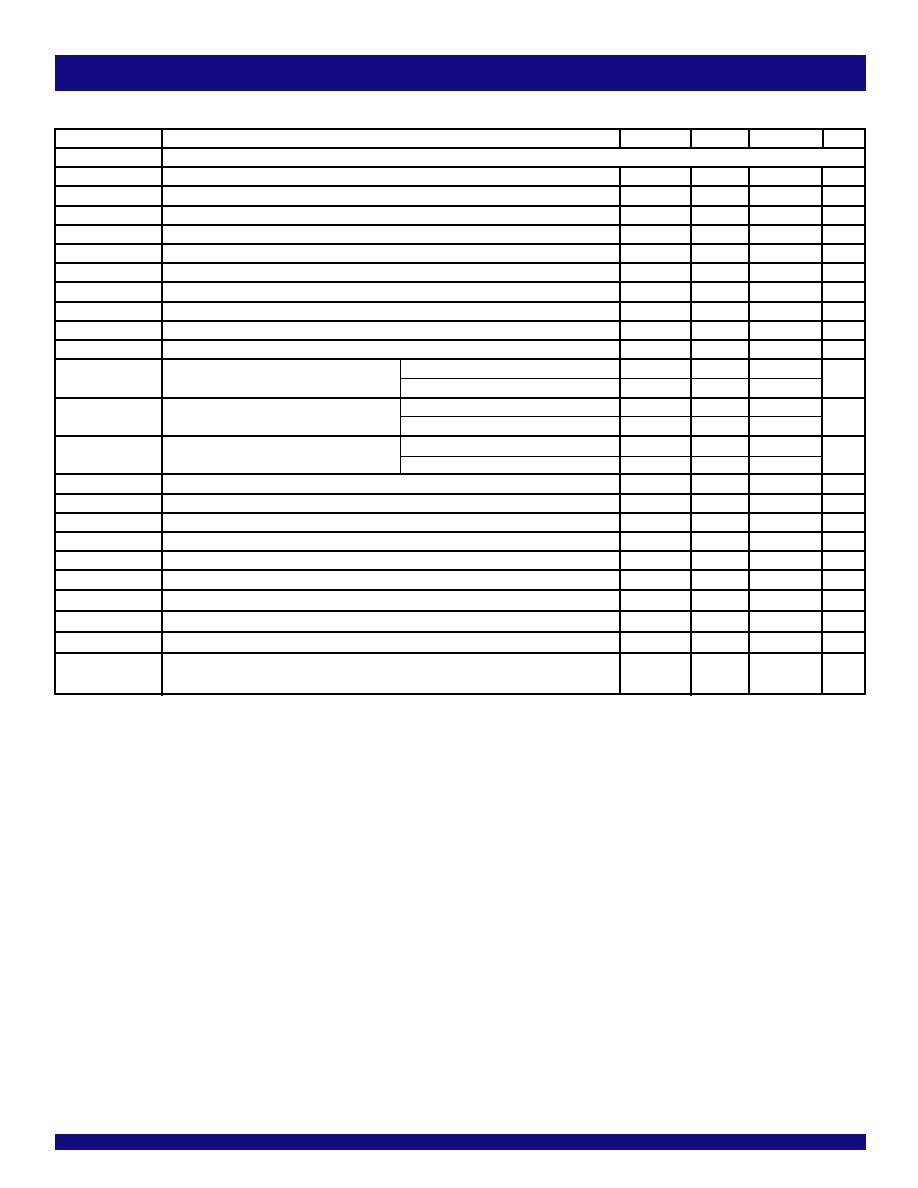

AC ELECTRICAL CHARACTERISTICS OVER OPERATING RANGE

Symbol

Parameter

Min.

Typ.

Max

Unit

FNOM

VCO Frequency Range

see VCO Frequency Range Select Table

tRPW

Reference Clock Pulse Width HIGH or LOW

1

—

ns

tFPW

Feedback Input Pulse Width HIGH or LOW

1

—

ns

tSK(B)

Output Matched Pair Skew(1,2,4)

——

50

ps

tSK(O)

Output Skew (Rise-Rise, Fall-Fall, Nominal)(1,3)

—

100

ps

tSK1(

ω)

Multiple Frequency Skew (Rise-Rise, Fall-Fall, Nominal-Divided, Divided-Divided)(1,3,4)

—

100

ps

tSK2(

ω)

Multiple Frequency Skew (Rise-Fall, Nominal-Divided, Divided-Divided)(1,3,4)

—

400

ps

tSK1(INV)

Inverting Skew (Nominal-Inverted)(1,3)

——

400

ps

tSK2(INV)

Inverting Skew (Rise-Rise, Fall-Fall, Rise-Fall, Inverted-Divided)(1,3,4)

—

400

ps

tSK(PR)

Process Skew(1,3.5)

——

300

ps

t(

φ)

REF Input to FB Static Phase Offset(6)

-100

—

100

ps

tODCV

Output Duty Cycle Variation from 50%(7)

HSTL / eHSTL / 1.8V LVTTL

-375

—

375

ps

2.5V LVTTL

-275

—

275

tORISE

Output Rise Time(8)

HSTL / eHSTL / 1.8V LVTTL

—

1.2

ns

2.5V LVTTL

—

1

tOFALL

OutputFallTime(8)

HSTL / eHSTL / 1.8V LVTTL

—

1.2

ns

2.5V LVTTL

—

1

tL

Power-up PLL Lock Time(9)

——

1

ms

tL(

ω)

PLL Lock Time After Input Frequency Change(9)

——

1

ms

tL(REFSEL1)

PLL Lock Time After Change in REF_SEL (9,11)

—

100

μs

tL(REFSEL2)

PLL Lock Time After Change in REF_SEL (REF1 and REF0 are different frequency)(9)

——

1

ms

tL(PD)

PLL Lock Time After Asserting

PD Pin(9)

——

1

ms

tJIT(CC)

Cycle-to-Cycle Output Jitter (peak-to-peak)(10)

—

50

75

ps

tJIT(PER)

PeriodJitter(peak-to-peak)(10)

——

75

ps

tJIT(HP)

Half Period Jitter (peak-to-peak, QFB/

QFB only)(10,12)

—

125

ps

tJIT(DUTY)

Duty Cycle Jitter (peak-to-peak)(10)

——

100

ps

VOX

HSTL and eHSTL Differential True and Complementary Output Crossing Voltage Level

VDDQ/2 - 150

VDDQ/2

VDDQ/2 + 150

mV

QFB/

QFB only(12)

NOTES:

1.

Skew is the time between the earliest and latest output transition among all outputs when all outputs are loaded with the specified load.

2.

tSK(B) is the skew between a pair of outputs (nQ0 and nQ1) when all outputs are selected as the same class.

3.

The measurement is made at VDDQ/2.

4.

There are three classes of outputs: nominal (zero delay), inverted, and divided (divide-by-2 or divide-by-4 mode).

5.

tSK(PR) is the output to corresponding output skew between any two devices operating under the same conditions (VDD and VDDQ, ambient temperature, air flow, etc.).

6.

t(

φ) is measured with REF and FB the same type of input, the same rise and fall times. For TxS/RxS = MID or HIGH, the measurement is taken from VTHI on REF to VTHI on

FB. For TxS/RxS = LOW, the measurement is taken from the crosspoint of REF/

REF to the crosspoint of FB/FB. All outputs are set to zero delay, FB input divider set to divide-

by-one, and FS = HIGH.

7.

tODCV is measured with all outputs selected for zero delay.

8.

Output rise and fall times are measured between 20% to 80% of the actual output voltage swing.

9.

tL, tL(

ω), tL(REFSEL1), tL(REFSEL2), and tL(PD) are the times that are required before the synchronization is achieved. These specifications are valid only after VDD/VDDQ is stable and

within the normal operating limits. These parameters are measured from the application of a new signal at REF or FB, or after

PD is (re)asserted until t(

φ) is within specified

limits.

10. The jitter parameters are measured with all outputs selected for zero delay, FB input divider is set to divide-by-one, and FS = HIGH.

11. Both REF inputs must be the same frequency, but up to ±180° out of phase.

12. For HSTL/eHSTL outputs only.

相关PDF资料 |

PDF描述 |

|---|---|

| IDT5T2010BBI8 | 5T SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PBGA144 |

| IDT5T9010BBGI | 5T SERIES, PLL BASED CLOCK DRIVER, 5 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PBGA144 |

| IDT5T9010BBI | 5T SERIES, PLL BASED CLOCK DRIVER, 5 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PBGA144 |

| IDT5T9010BBI8 | 5T SERIES, PLL BASED CLOCK DRIVER, 5 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PBGA144 |

| IDT5T905PGGI | 5T SERIES, LOW SKEW CLOCK DRIVER, 5 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO28 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT5T2010BBGI8 | 功能描述:IC CLK DVR ZD PLL 2.5V 144-BGA RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:TeraClock™ 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| IDT5T2010BBI | 功能描述:IC CLK DVR ZD PLL 2.5V 144-BGA RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:TeraClock™ 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| IDT5T2010NLGI | 功能描述:IC CLK DVR ZD PLL 2.5V 68-VFQFPN RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:TeraClock™ 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| IDT5T2010NLGI8 | 功能描述:IC CLK DVR ZD PLL 2.5V 68-VFQFPN RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:TeraClock™ 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| IDT5T2110BBGI | 功能描述:IC CLK DVR 2.5V PLL DIFF 144BGA RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:TeraClock™ 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

发布紧急采购,3分钟左右您将得到回复。