- 您现在的位置:买卖IC网 > PDF目录4172 > IDT71V632ZS5PFG (IDT, Integrated Device Technology Inc)IC SRAM 2MBIT 5NS 100TQFP PDF资料下载

参数资料

| 型号: | IDT71V632ZS5PFG |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 2/19页 |

| 文件大小: | 0K |

| 描述: | IC SRAM 2MBIT 5NS 100TQFP |

| 标准包装: | 72 |

| 格式 - 存储器: | RAM |

| 存储器类型: | SRAM - 同步 |

| 存储容量: | 2M(64K x 32) |

| 速度: | 5ns |

| 接口: | 并联 |

| 电源电压: | 3.135 V ~ 3.63 V |

| 工作温度: | 0°C ~ 70°C |

| 封装/外壳: | 100-LQFP |

| 供应商设备封装: | 100-TQFP(14x20) |

| 包装: | 托盘 |

�� ��

��

��

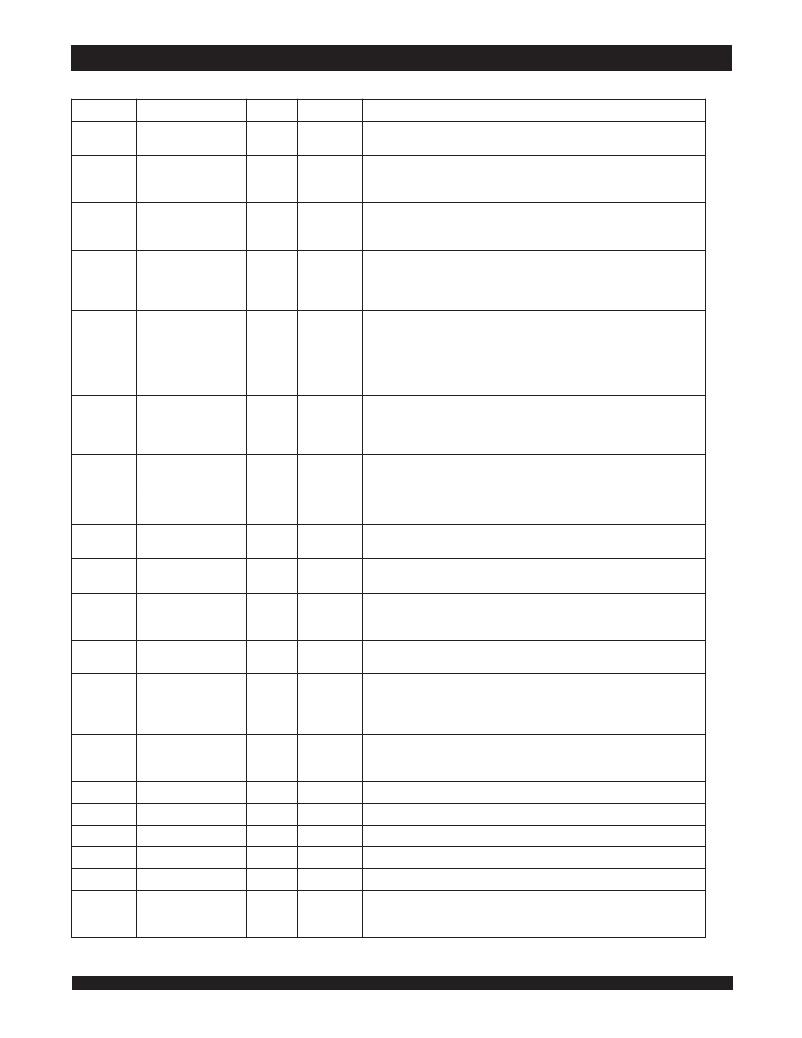

��IDT71V632,� 64K� x� 32,� 3.3V� Synchronous� SRAM�

�with� Pipelined� Outputs� and� Single� Cycle� Deselect�

�Pin� Definitions� (1)�

�Commercial� and� Industrial� Temperature� Ranges�

�S� y� m� b� o� l�

�A� 0� –� A� 1� 5�

�P� i� n� F� u� n� c� t� i� o� n�

�A� d� d� r� e� s� s� I� n� p� u� t� s�

�I� /� O�

�I�

�A� c� t� i� v� e�

�N� /� A�

�D� e� s� c� r� i� p� t� i� o� n�

�S� y� n� c� h� r� o� n� o� u� s� A� d� d� r� e� s� s� i� n� p� u� t� s� .� T� h� e� a� d� d� r� e� s� s� r� e� g� i� s� t� e� r� i� s� t� r� i� g� g� e� r� e� d� b� y� a� c� o� m� b� i� n� a� t� i� o� n�

�o� f� t� h� e� r� i� s� i� n� g� e� d� g� e� o� f� C� L� K� a� n� d� A� D� S� C� L� o� w� o� r� A� D� S� P� L� o� w� a� n� d� C� E� L� o� w� .�

�A� D� S� C�

�A� d� d� r� e� s� s� S� t� a� t� u� s�

�I�

�L� O� W�

�S� y� n� c� h� r� o� n� o� u� s� A� d� d� r� e� s� s� S� t� a� t� u� s� f� r� o� m� C� a� c� h� e� C� o� n� t� r� o� l� l� e� r� .� A� D� S� C� i� s� a� n� a� c� t� i� v� e� L� O� W�

�(� C� a� c� h� e� C� o� n� t� r� o� l� l� e� r� )�

�i� n� p� u� t� t� h� a� t� i� s� u� s� e� d� t� o� l� o� a� d� t� h� e� a� d� d� r� e� s� s� r� e� g� i� s� t� e� r� s� w� i� t� h� n� e� w� a� d� d� r� e� s� s� e� s� .� A� D� S� C� i� s�

�N� O� T� G� A� T� E� D� b� y� C� E� .�

�A� D� S� P�

�A� D� V�

�A� d� d� r� e� s� s� S� t� a� t� u� s�

�(� P� r� o� c� e� s� s� o� r� )�

�B� u� r� s� t� A� d� d� r� e� s� s� A� d� v� a� n� c� e�

�I�

�I�

�L� O� W�

�L� O� W�

�S� y� n� c� h� r� o� n� o� u� s� A� d� d� r� e� s� s� S� t� a� t� u� s� f� r� o� m� P� r� o� c� e� s� s� o� r� .� A� D� S� P� i� s� a� n� a� c� t� i� v� e� L� O� W� i� n� p� u� t� t� h� a� t�

�i� s� u� s� e� d� t� o� l� o� a� d� t� h� e� a� d� d� r� e� s� s� r� e� g� i� s� t� e� r� s� w� i� t� h� n� e� w� a� d� d� r� e� s� s� e� s� .� A� D� S� P� i� s� g� a� t� e� d� b� y�

�C� E� .�

�S� y� n� c� h� r� o� n� o� u� s� A� d� d� r� e� s� s� A� d� v� a� n� c� e� .� A� D� V� i� s� a� n� a� c� t� i� v� e� L� O� W� i� n� p� u� t� t� h� a� t� i� s� u� s� e� d� t� o�

�a� d� v� a� n� c� e� t� h� e� i� n� t� e� r� n� a� l� b� u� r� s� t� c� o� u� n� t� e� r� ,� c� o� n� t� r� o� l� l� i� n� g� b� u� r� s� t� a� c� c� e� s� s� a� f� t� e� r� t� h� e� i� n� i� t� i� a� l�

�a� d� d� r� e� s� s� i� s� l� o� a� d� e� d� .� W� h� e� n� t� h� i� s� i� n� p� u� t� i� s� H� I� G� H� t� h� e� b� u� r� s� t� c� o� u� n� t� e� r� i� s� n� o� t� i� n� c� r� e� m� e� n� t� e� d� ;�

�t� h� a� t� i� s� ,� t� h� e� r� e� i� s� n� o� a� d� d� r� e� s� s� a� d� v� a� n� c� e� .�

�B� W� E�

�B� y� t� e� W� r� i� t� e� E� n� a� b� l� e�

�I�

�L� O� W�

�S� y� n� c� h� r� o� n� o� u� s� b� y� t� e� w� r� i� t� e� e� n� a� b� l� e� g� a� t� e� s� t� h� e� b� y� t� e� w� r� i� t� e� i� n� p� u� t� s� B� W� 1� –� B� W� 4� .� I� f� B� W� E� i� s�

�L� O� W� a� t� t� h� e� r� i� s� i� n� g� e� d� g� e� o� f� C� L� K� t� h� e� n� B� W� X� i� n� p� u� t� s� a� r� e� p� a� s� s� e� d� t� o� t� h� e� n� e� x� t� s� t� a� g� e� i� n�

�t� h� e� c� i� r� c� u� i� t� .� A� b� y� t� e� w� r� i� t� e� c� a� n� s� t� i� l� l� b� e� b� l� o� c� k� e� d� i� f� A� D� S� P� i� s� L� O� W� a� t� t� h� e� r� i� s� i� n� g� e� d� g� e� o� f�

�C� L� K� .� I� f� A� D� S� P� i� s� H� I� G� H� a� n� d� B� W� X� i� s� L� O� W� a� t� t� h� e� r� i� s� i� n� g� e� d� g� e� o� f� C� L� K� t� h� e� n� d� a� t� a� w� i� l� l�

�b� e� w� r� i� t� t� e� n� t� o� t� h� e� S� R� A� M� .� I� f� B� W� E� i� s� H� I� G� H� t� h� e� n� t� h� e� b� y� t� e� w� r� i� t� e� i� n� p� u� t� s� a� r� e� b� l� o� c� k� e� d�

�a� n� d� o� n� l� y� G� W� c� a� n� i� n� i� t� i� a� t� e� a� w� r� i� t� e� c� y� c� l� e� .�

�B� W� 1� –� B� W� 4�

�I� n� d� i� v� i� d� u� a� l� B� y� t� e�

�W� r� i� t� e� E� n� a� b� l� e� s�

�I�

�L� O� W�

�S� y� n� c� h� r� o� n� o� u� s� b� y� t� e� w� r� i� t� e� e� n� a� b� l� e� s� .� B� W� 1� c� o� n� t� r� o� l� s� I� /� O� (� 7� :� 0� )� ,� B� W� 2� c� o� n� t� r� o� l� s� I� /� O� (� 1� 5� :� 8� )� ,�

�e� t� c� .� A� n� y� a� c� t� i� v� e� b� y� t� e� w� r� i� t� e� c� a� u� s� e� s� a� l� l� o� u� t� p� u� t� s� t� o� b� e� d� i� s� a� b� l� e� d� .� A� D� S� P� L� O� W�

�d� i� s� a� b� l� e� s� a� l� l� b� y� t� e� w� r� i� t� e� s� .� B� W� 1� –� B� W� 4� m� u� s� t� m� e� e� t� s� p� e� c� i� f� i� e� d� s� e� t� u� p� a� n� d� h� o� l� d� t� i� m� e� s�

�w� i� t� h� r� e� s� p� e� c� t� t� o� C� L� K� .�

�C� E�

�C� h� i� p� E� n� a� b� l� e�

�I�

�L� O� W�

�S� y� n� c� h� r� o� n� o� u� s� c� h� i� p� e� n� a� b� l� e� .� C� E� i� s� u� s� e� d� w� i� t� h� C� S� 0� a� n� d� C� S� 1� t� o� e� n� a� b� l� e� t� h� e�

�I� D� T� 7� 1� V� 6� 3� 2� .� C� E� a� l� s� o� g� a� t� e� s� A� D� S� P� .�

�C� L� K�

�C� l� o� c� k�

�I�

�N� /� A�

�T� h� i� s� i� s� t� h� e� c� l� o� c� k� i� n� p� u� t� .� A� l� l� t� i� m� i� n� g� r� e� f� e� r� e� n� c� e� s� f� o� r� t� h� e� d� e� v� i� c� e� a� r� e� m� a� d� e� w� i� t� h� r� e� s� p� e� c� t�

�t� o� t� h� i� s� i� n� p� u� t� .�

�C� S� 0�

�C� h� i� p� S� e� l� e� c� t� 0�

�I�

�H� I� G� H�

�S� y� n� c� h� r� o� n� o� u� s� a� c� t� i� v� e� H� I� G� H� c� h� i� p� s� e� l� e� c� t� .� C� S� 0� i� s� u� s� e� d� w� i� t� h� C� E� a� n� d� C� S� 1� t� o� e� n� a� b� l� e�

�t� h� e� c� h� i� p� .�

�C� S� 1�

�C� h� i� p� S� e� l� e� c� t� 1�

�I�

�L� O� W�

�S� y� n� c� h� r� o� n� o� u� s� a� c� t� i� v� e� L� O� W� c� h� i� p� s� e� l� e� c� t� .� C� S� 1� i� s� u� s� e� d� w� i� t� h� C� E� a� n� d� C� S� 0� t� o� e� n� a� b� l� e�

�t� h� e� c� h� i� p� .�

�G� W�

�G� l� o� b� a� l� W� r� i� t� e� E� n� a� b� l� e�

�I�

�L� O� W�

�S� y� n� c� h� r� o� n� o� u� s� g� l� o� b� a� l� w� r� i� t� e� e� n� a� b� l� e� .� T� h� i� s� i� n� p� u� t� w� i� l� l� w� r� i� t� e� a� l� l� f� o� u� r� 8� -� b� i� t� d� a� t� a� b� y� t� e� s�

�w� h� e� n� L� O� W� o� n� t� h� e� r� i� s� i� n� g� e� d� g� e� o� f� C� L� K� .� G� W� s� u� p� e� r� c� e� d� e� s� i� n� d� i� v� i� d� u� a� l� b� y� t� e� w� r� i� t� e�

�e� n� a� b� l� e� s� .�

�I� /� O� 0� –� I� /� O� 3� 1�

�D� a� t� a� I� n� p� u� t� /� O� u� t� p� u� t�

�I� /� O�

�N� /� A�

�S� y� n� c� h� r� o� n� o� u� s� d� a� t� a� i� n� p� u� t� /� o� u� t� p� u� t� (� I� /� O� )� p� i� n� s� .� B� o� t� h� t� h� e� d� a� t� a� i� n� p� u� t� p� a� t� h� a� n� d� d� a� t� a� o� u� t� p� u� t�

�p� a� t� h� a� r� e� r� e� g� i� s� t� e� r� e� d� a� n� d� t� r� i� g� g� e� r� e� d� b� y� t� h� e� r� i� s� i� n� g� e� d� g� e� o� f� C� L� K� .�

�L� B� O�

�L� i� n� e� a� r� B� u� r� s� t� O� r� d� e� r�

�I�

�L� O� W�

�A� s� y� n� c� h� r� o� n� o� u� s� b� u� r� s� t� o� r� d� e� r� s� e� l� e� c� t� i� o� n� D� C� i� n� p� u� t� .� W� h� e� n� L� B� O� i� s� H� I� G� H� t� h� e� I� n� t� e� r� l� e� a� v� e� d�

�(� I� n� t� e� l� )� b� u� r� s� t� s� e� q� u� e� n� c� e� i� s� s� e� l� e� c� t� e� d� .� W� h� e� n� L� B� O� i� s� L� O� W� t� h� e� L� i� n� e� a� r� (� P� o� w� e� r� P� C� )� b� u� r� s� t�

�s� e� q� u� e� n� c� e� i� s� s� e� l� e� c� t� e� d� .� L� B� O� i� s� a� s� t� a� t� i� c� D� C� i� n� p� u� t� a� n� d� m� u� s� t� n� o� t� c� h� a� n� g� e� s� t� a� t� e� w� h� i� l� e�

�t� h� e� d� e� v� i� c� e� i� s� o� p� e� r� a� t� i� n� g� .�

�O� E�

�O� u� t� p� u� t� E� n� a� b� l� e�

�I�

�L� O� W�

�A� s� y� n� c� h� r� o� n� o� u� s� o� u� t� p� u� t� e� n� a� b� l� e� .� W� h� e� n� O� E� i� s� L� O� W� t� h� e� d� a� t� a� o� u� t� p� u� t� d� r� i� v� e� r� s� a� r� e�

�e� n� a� b� l� e� d� o� n� t� h� e� I� /� O� p� i� n� s� i� f� t� h� e� c� h� i� p� i� s� a� l� s� o� s� e� l� e� c� t� e� d� .� W� h� e� n� O� E� i� s� H� I� G� H� t� h� e� I� /� O�

�p� i� n� s� a� r� e� i� n� a� h� i� g� h� -� i� m� p� e� d� e� n� c� e� s� t� a� t� e� .�

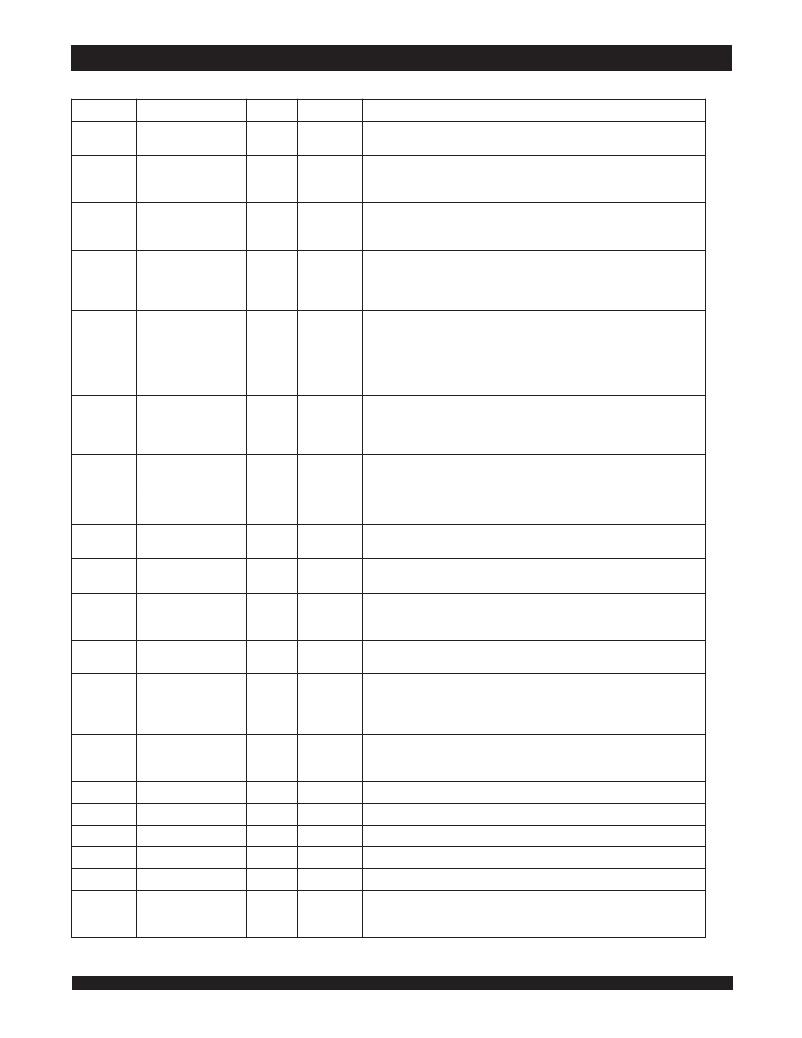

�V� D� D�

�V� D� D� Q�

�V� S� S�

�V� S� S� Q�

�N� C�

�Z� Z�

�P� o� w� e� r� S� u� p� p� l� y�

�P� o� w� e� r� S� u� p� p� l� y�

�G� r� o� u� n� d�

�G� r� o� u� n� d�

�N� o� C� o� n� n� e� c� t�

�S� l� e� e� p� M� o� d� e�

�N� /� A�

�N� /� A�

�N� /� A�

�N� /� A�

�N� /� A�

�I�

�N� /� A�

�N� /� A�

�N� /� A�

�N� /� A�

�N� /� A�

�H� I� G� H�

�3� .� 3� V� c� o� r� e� p� o� w� e� r� s� u� p� p� l� y� i� n� p� u� t� s� .�

�3� .� 3� V� I� /� O� p� o� w� e� r� s� u� p� p� l� y� i� n� p� u� t� s� .�

�C� o� r� e� g� r� o� u� n� d� p� i� n� s� .�

�I� /� O� g� r� o� u� n� d� p� i� n� s� .�

�N� C� p� i� n� s� a� r� e� n� o� t� e� l� e� c� t� r� i� c� a� l� l� y� c� o� n� n� e� c� t� e� d� t� o� t� h� e� c� h� i� p� .�

�A� s� y� n� c� h� r� o� n� o� u� s� s� l� e� e� p� m� o� d� e� i� n� p� u� t� .� Z� Z� H� I� G� H� w� i� l� l� g� a� t� e� t� h� e� C� L� K� i� n� t� e� r� n� a� l� l� y� a� n� d� p� o� w� e� r�

�d� o� w� n� t� h� e� I� D� T� 7� 1� V� 6� 3� 2� t� o� i� t� s� l� o� w� e� s� t� p� o� w� e� r� c� o� n� s� u� m� p� t� i� o� n� l� e� v� e� l� .� D� a� t� a� r� e� t� e� n� t� i� o� n� i� s�

�g� u� a� r� a� n� t� e� e� d� i� n� S� l� e� e� p� M� o� d� e� .�

�NOTE:�

�1.� All� synchronous� inputs� must� meet� specified� setup� and� hold� times� with� respect� to� CLK.�

�6.42�

�3� 6� 1� 9� t� b� l� 0� 2�

�相关PDF资料 |

PDF描述 |

|---|---|

| IDT7164L20YGI | IC SRAM 64KBIT 20NS 28SOJ |

| XC4003E-3PG120I | IC FPGA I-TEMP 5V 3-SPD 120-CPGA |

| IDT71V3559S85PFG | IC SRAM 4MBIT 85NS 100TQFP |

| IDT71V3559S80PFG | IC SRAM 4MBIT 80NS 100TQFP |

| XC4003E-3PG120C | IC FPGA C-TEMP 5V 3-SPD 120-CPGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT71V632ZS6PFG | 功能描述:IC SRAM 2MBIT 6NS 100TQFP RoHS:是 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:72 系列:- 格式 - 存储器:RAM 存储器类型:SRAM - 同步 存储容量:4.5M(256K x 18) 速度:133MHz 接口:并联 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 70°C 封装/外壳:100-LQFP 供应商设备封装:100-TQFP(14x20) 包装:托盘 |

| IDT71V633S11PF | 制造商:Integrated Device Technology Inc 功能描述:SRAM Chip Sync Single 3.3V 2M-Bit 64K x 32 11ns 100-Pin PQFP |

| IDT71V65602S100BG | 功能描述:IC SRAM 9MBIT 100MHZ 119BGA RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:576 系列:- 格式 - 存储器:闪存 存储器类型:闪存 - NAND 存储容量:512M(64M x 8) 速度:- 接口:并联 电源电压:2.7 V ~ 3.6 V 工作温度:-40°C ~ 85°C 封装/外壳:48-TFSOP(0.724",18.40mm 宽) 供应商设备封装:48-TSOP 包装:托盘 其它名称:497-5040 |

| IDT71V65602S100BG8 | 功能描述:IC SRAM 9MBIT 100MHZ 119BGA RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:576 系列:- 格式 - 存储器:闪存 存储器类型:闪存 - NAND 存储容量:512M(64M x 8) 速度:- 接口:并联 电源电压:2.7 V ~ 3.6 V 工作温度:-40°C ~ 85°C 封装/外壳:48-TFSOP(0.724",18.40mm 宽) 供应商设备封装:48-TSOP 包装:托盘 其它名称:497-5040 |

| IDT71V65602S100BQ | 功能描述:IC SRAM 9MBIT 100MHZ 165FBGA RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:576 系列:- 格式 - 存储器:闪存 存储器类型:闪存 - NAND 存储容量:512M(64M x 8) 速度:- 接口:并联 电源电压:2.7 V ~ 3.6 V 工作温度:-40°C ~ 85°C 封装/外壳:48-TFSOP(0.724",18.40mm 宽) 供应商设备封装:48-TSOP 包装:托盘 其它名称:497-5040 |

发布紧急采购,3分钟左右您将得到回复。