- 您现在的位置:买卖IC网 > PDF目录9580 > IDT82V3010PVG8 (IDT, Integrated Device Technology Inc)IC PLL WAN 51/E1/OC3 DUAL 56SSOP PDF资料下载

参数资料

| 型号: | IDT82V3010PVG8 |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 7/31页 |

| 文件大小: | 0K |

| 描述: | IC PLL WAN 51/E1/OC3 DUAL 56SSOP |

| 标准包装: | 1,000 |

| 类型: | 时钟/频率发生器,多路复用器 |

| PLL: | 是 |

| 主要目的: | 电信 |

| 输入: | 时钟 |

| 输出: | CMOS,LVDS,TTL |

| 电路数: | 1 |

| 比率 - 输入:输出: | 2:12 |

| 差分 - 输入:输出: | 无/是 |

| 频率 - 最大: | 32.768MHz |

| 电源电压: | 3 V ~ 3.6 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 56-BSSOP(0.295",7.50mm 宽) |

| 供应商设备封装: | 56-SSOP |

| 包装: | 带卷 (TR) |

| 其它名称: | 82V3010PVG8 |

第1页第2页第3页第4页第5页第6页当前第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页

IDT82V3010

T1/E1/OC3 Telecom Clock Generator with Dual Reference Inputs

Functional Description

15

Feberuary 20, 2009

2.11

POWER SUPPLY FILTERING TECHNIQUES

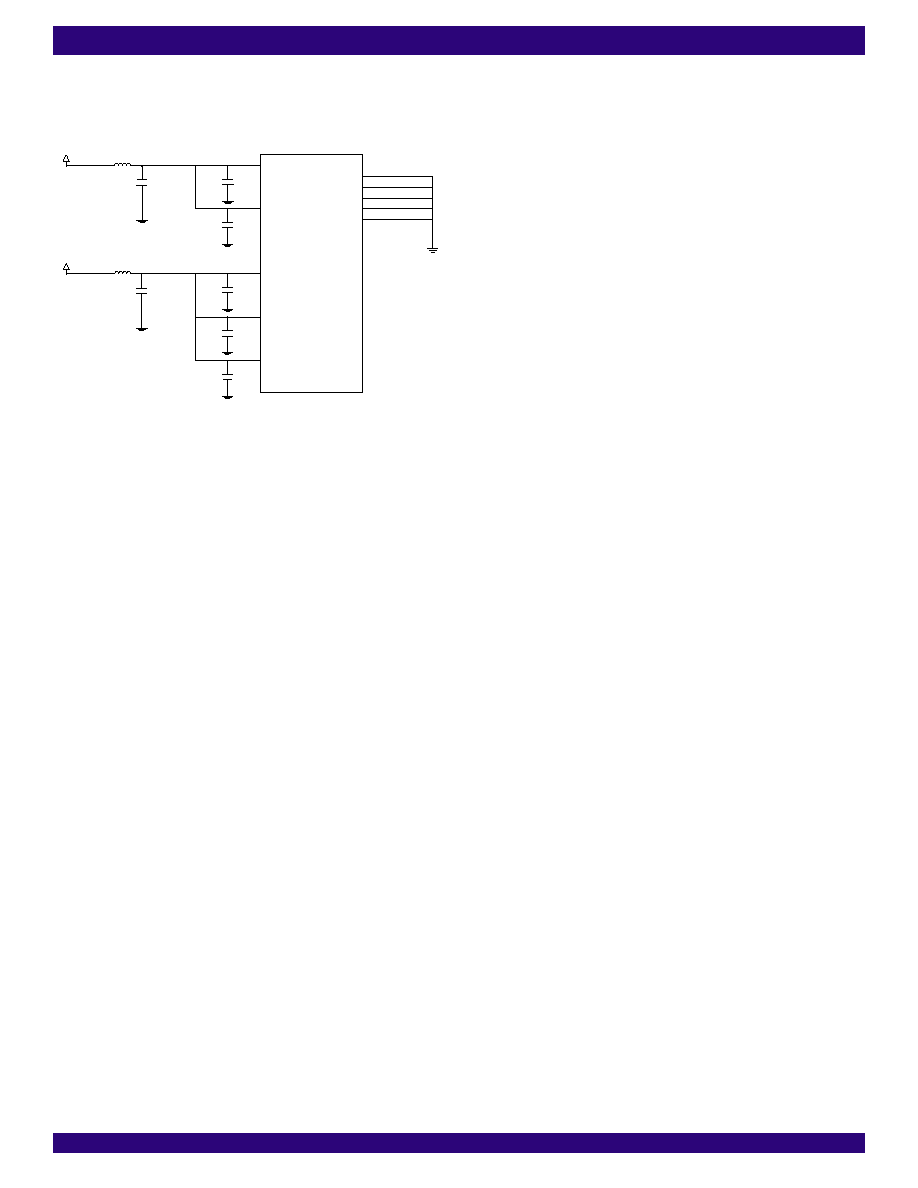

Figure - 10 IDT82V3010 Power Decoupling Scheme

As in any high speed analog circuitry, the power supply pins are

vulnerable to random noise. The 82V3010 provides separate power

supplies to isolate any high switching noise from the outputs to the

internal PLL. VDDD and VDDA should be individually connected to the

power supply plane through vias, and bypass capacitors should be used

for each pin. To achieve optimum jitter performance, power supply

isolation is required. Figure - 10 illustrated how bypass capacitor and

ferrite bead should be connected to each power pin.

For the 82V3010, the decoupling for VDDA and VDDD must all be

handled individually. The switching power supply should be filtering with

a large bulk capacitor of 47 uF (1210 case size, ceramic) and a 0.1 uF

(0402 case size, ceramic).

VDDA provides power to the analog circuits. The analog power

supply VDDA should have low impedance. This can be achieved by

using one 10 uF (1210 case size, ceramic) and at least two 0.1 uF (0402

case size, ceramic) capacitors in parallel. The 0.1 uF (0402 case size,

ceramic) capacitors must be placed right next to the VDDA pins as close

as possible. Note that the 10 uF capacitor must be of 1210 case size,

and it must be ceramic for lowest ESR (Effective Series Resistance)

possible. The 0.1 uF should be of case size 0402, this offers the lowest

ESL (Effective Series Inductance) to achieve low impedance towards

the high speed range.

VDDD is the power rail for the core logic as well as I/O driver circuits.

For the VDDD, at least three 0.1 uF (0402 case size, ceramic) and one

10 uF (1210 case size, ceramic) capacitors are recommended. The 0.1

uF capacitors should be placed as close to the VDDD pins as possible.

Please refer to evaluation board schematic for details.

37

48

IDT82V3010

V

SS

3.3V

0.1

F

0.1

F

10

F

12

V

SS

18

V

SS

27

V

SS

38

V

SS

47

V

DDA

V

DDA

13

26

19

V

DDD

V

DDD

SLF7028T-100M1R1

0.1

F

3.3V

0.1

F

10

F

SLF7028T-100M1R1

V

DDD

0.1

F

相关PDF资料 |

PDF描述 |

|---|---|

| D38999/26MF28SN | CONN PLUG 28POS STRAIGHT W/SCKT |

| D38999/26MG16SA | CONN PLUG 16POS STRAIGHT W/SCKT |

| ICS894D115BGI-01 | IC CLK/DATA RECOVERY 20-TSSOP |

| VE-2N0-MX-F2 | CONVERTER MOD DC/DC 5V 75W |

| VI-B1P-MW-F2 | CONVERTER MOD DC/DC 13.8V 100W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT82V3011 | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:T1/E1/OC3 WAN PLL WITH SINGLE REFERENCE INPUT |

| IDT82V3011PV | 制造商:INT_DEV_TECH 功能描述: |

| IDT82V3011PVG | 功能描述:IC PLL WAN T1/E1/OC3 SGL 56-SSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT |

| IDT82V3011PVG8 | 功能描述:IC PLL WAN T1/E1/OC3 SGL 56-SSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT |

| IDT82V3012 | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:T1/E1/OC3 WAN PLL WITH DUAL REFERENCE INPUTS |

发布紧急采购,3分钟左右您将得到回复。