- 您现在的位置:买卖IC网 > PDF目录377488 > IDT82V3280DQG (INTEGRATED DEVICE TECHNOLOGY INC) WAN PLL PDF资料下载

参数资料

| 型号: | IDT82V3280DQG |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 通信及网络 |

| 英文描述: | WAN PLL |

| 中文描述: | SPECIALTY TELECOM CIRCUIT, PQFP100 |

| 封装: | GREEN, TQFP-100 |

| 文件页数: | 25/167页 |

| 文件大小: | 1039K |

| 代理商: | IDT82V3280DQG |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页当前第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页第153页第154页第155页第156页第157页第158页第159页第160页第161页第162页第163页第164页第165页第166页第167页

IDT82V3280

WAN PLL

Functional Description

25

June 19, 2006

3.6

T0 / T4 DPLL INPUT CLOCK SELECTION

An input clock is selected for T0 DPLL and for T4 DPLL respectively.

For T0 path, the EXT_SW bit and the T0_INPUT_SEL[3:0] bits deter-

mine the input clock selection, as shown in

Table 6

:

For T4 path, the T4 DPLL may lock to a T0 DPLL output or lock inde-

pendently from T0 path, as determined by the T4_LOCK_T0 bit. When

the T4 DPLL locks to the T0 DPLL output, the T4 selected input clock is

a 77.76 MHz or 8 kHz signal from the T0 DPLL 77.76 MHz path (refer to

Chapter 3.11.5.1 T0 Path

), as determined by the T0_FOR_T4 bit. When

the T4 path locks independently from the T0 path, the T4 DPLL input

clock selection is determined by the T4_INPUT_SEL[3:0] bits. Refer to

Table 7

:

External Fast selection is done between IN3/IN5 and IN4/IN6 pairs.

Forced selection is done by setting the related registers.

Automatic selection is done based on the results of input clocks qual-

ity monitoring and the related registers configuration.

The selected input clock is attempted to be locked in T0/T4 DPLL.

3.6.1

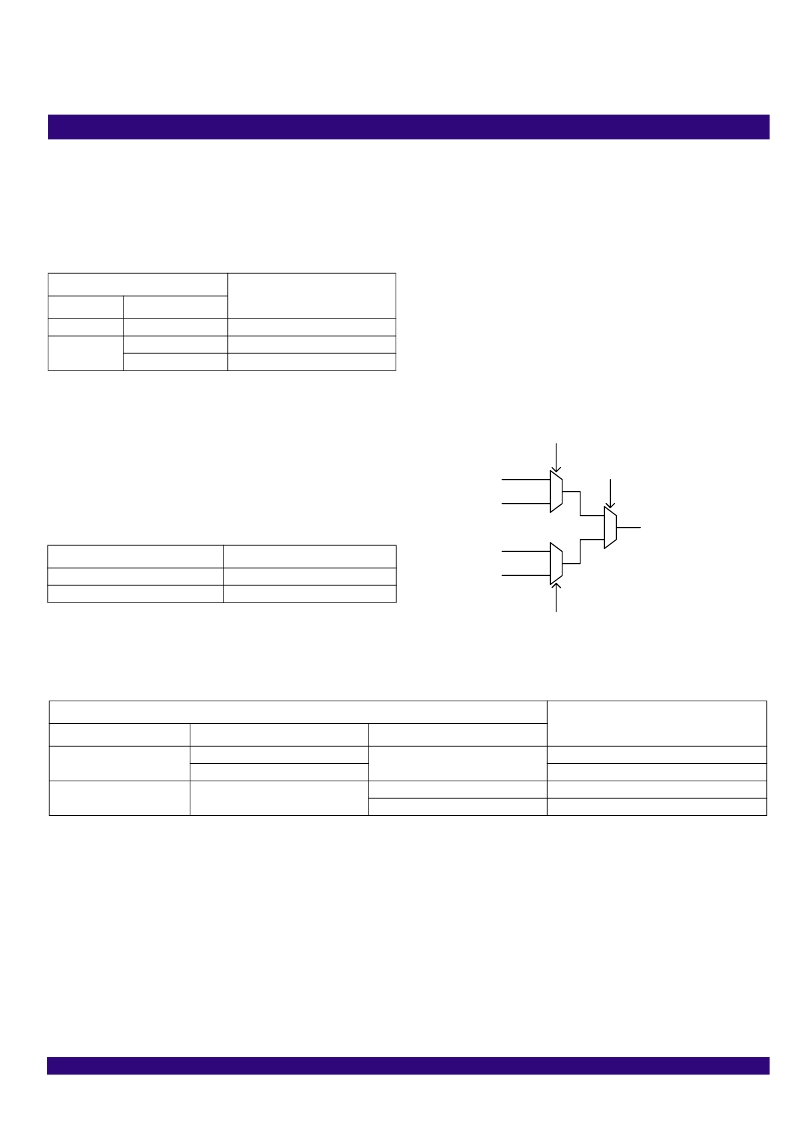

EXTERNAL FAST SELECTION (T0 ONLY)

The External Fast selection is supported by T0 path only. In External

Fast selection, only IN3/IN5 and IN4/IN6 pairs are available for selec-

tion. Refer to

Figure 5

. The results of input clocks quality monitoring

(refer to

Chapter 3.5 Input Clock Quality Monitoring

) do not affect input

clock selection.

The T0 input clock selection is determined by the FF_SRCSW pin

after reset (this pin determines the default value of the EXT_SW bit dur-

ing

reset,

refer

to

Chapter 2

IN3_SEL_PRIORITY[3:0] bits and the IN4_SEL_PRIORITY[3:0] bits, as

shown in

Figure 5

and

Table 8

:

Pin

Description

),

the

Figure 5. External Fast Selection

Table 6: Input Clock Selection for T0 Path

Control Bits

Input Clock Selection

EXT_SW

T0_INPUT_SEL[3:0]

1

don’t-care

other than 0000

0000

External Fast selection

Forced selection

Automatic selection

0

Table 7: Input Clock Selection for T4 Path

Control Bits - T4_INPUT_SEL[3:0]

Input Clock Selection

other than 0000

0000

Forced selection

Automatic selection

FF_SRCSW pin

IN3

IN5

IN4

IN6

IN3_SEL_PRIORITY[3:0] bits

IN4_SEL_PRIORITY[3:0] bits

attempted to be

locked in T0 DPLL

Table 8: External Fast Selection

Control Pin & Bits

the Selected Input Clock

FF_SRCSW (after reset)

IN3_SEL_PRIORITY[3:0]

IN4_SEL_PRIORITY[3:0]

high

0000

don’t-care

IN5

IN3

IN6

IN4

other than 0000

low

don’t-care

0000

other than 0000

相关PDF资料 |

PDF描述 |

|---|---|

| IDT82V3280PF | WAN PLL |

| IDT82V3280PFG | WAN PLL |

| IDT82V3288 | WAN PLL |

| IDT82V3288BC | WAN PLL |

| IDT82V3288BCG | WAN PLL |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT82V3280DQG8 | 功能描述:IC PLL WAN SE STRATUM 2 100-TQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT |

| IDT82V3280EQG | 功能描述:IC PLL WAN SE STRATUM 2 100TQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT |

| IDT82V3280EQG8 | 制造商:Integrated Device Technology Inc 功能描述:IC PLL WAN SE STRATUM 2 100TQFP |

| IDT82V3280EQGBLANK | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:WAN PLL |

| IDT82V3280PF | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:WAN PLL |

发布紧急采购,3分钟左右您将得到回复。